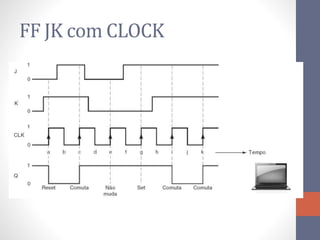

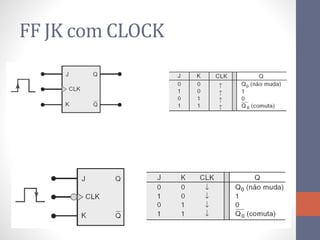

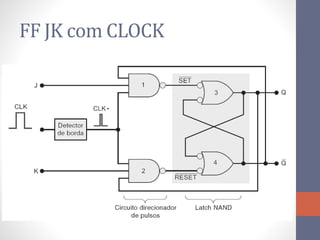

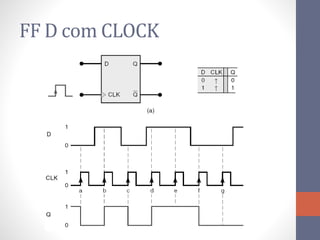

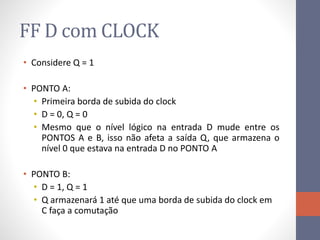

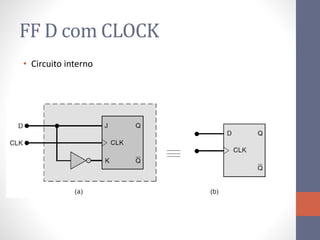

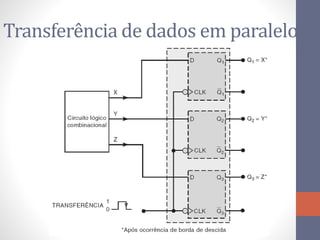

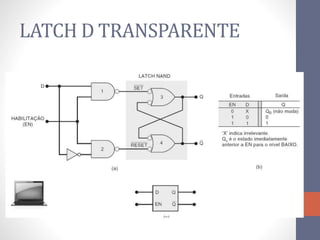

O documento descreve os circuitos de flip-flops JK, D e latch D transparente. Explica como cada um opera, incluindo suas entradas, saídas e como respondem aos pulsos de clock. Também fornece exemplos de suas aplicações em circuitos digitais como contadores e transferência de dados paralela.