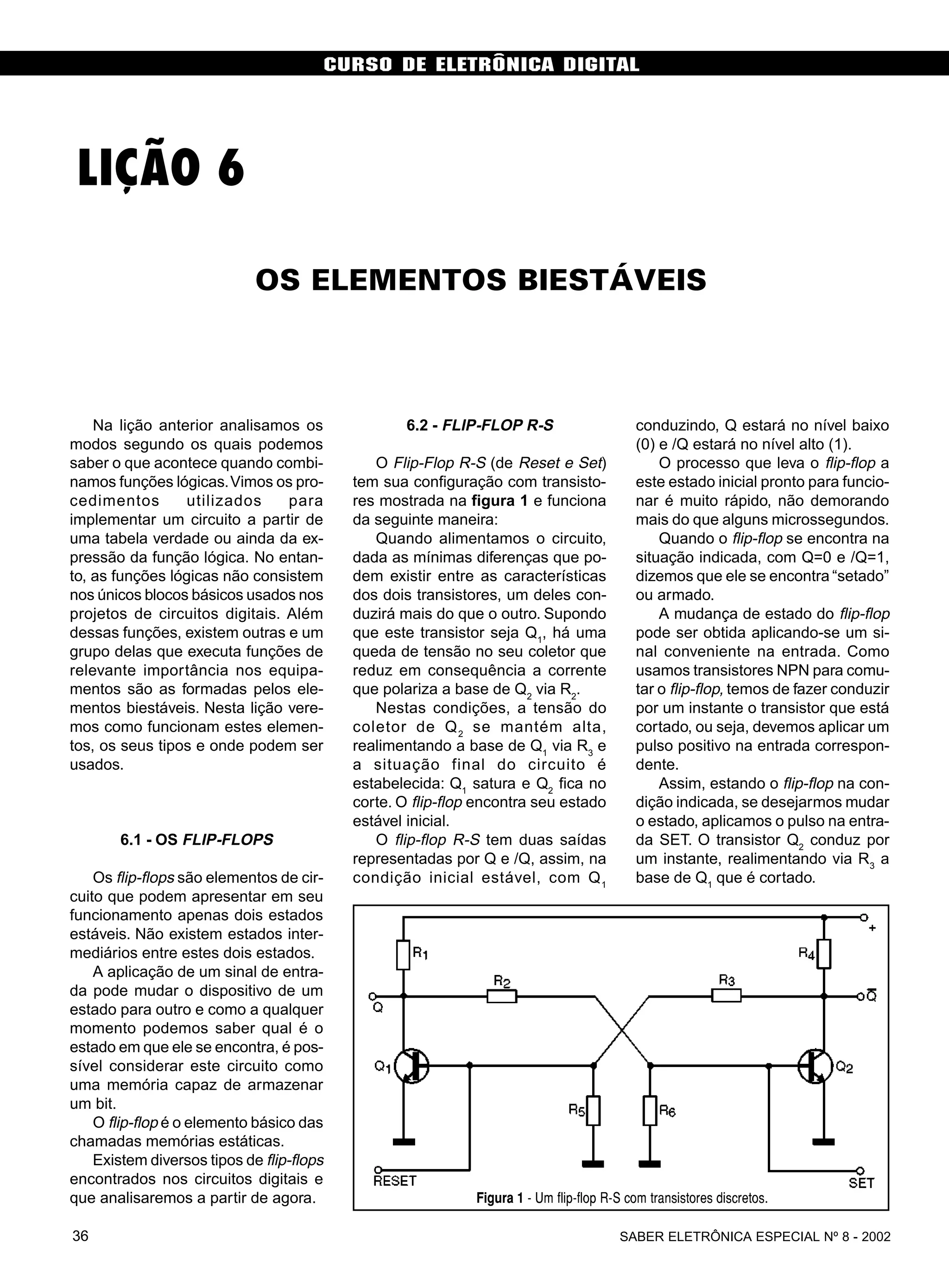

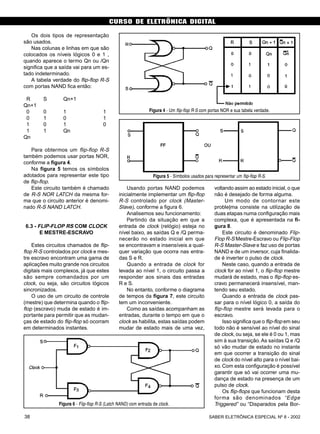

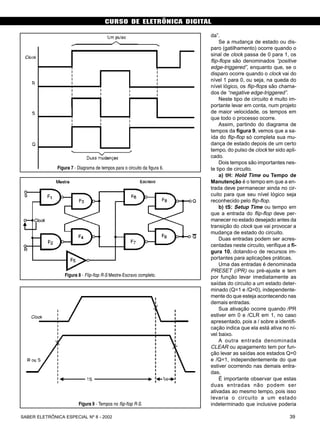

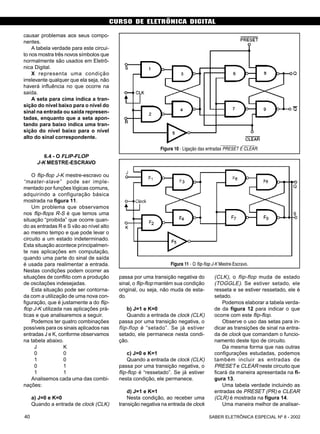

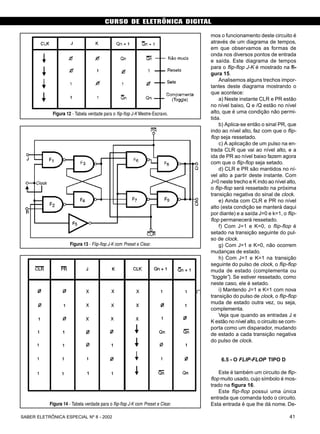

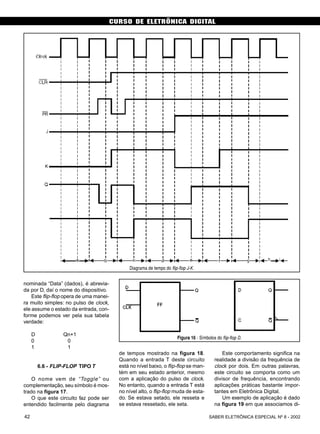

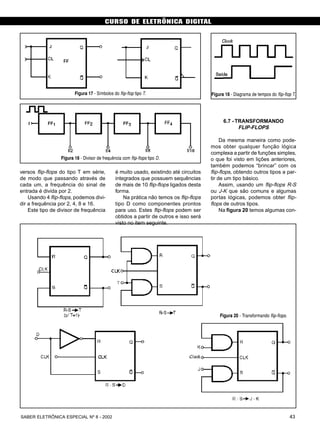

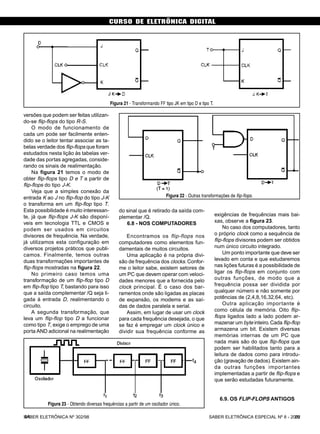

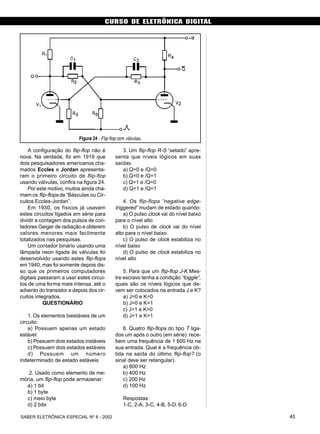

O documento descreve os elementos biestáveis, em particular os flip-flops. Os flip-flops são circuitos digitais que podem assumir apenas dois estados estáveis e funcionam como memória de um bit. Existem diferentes tipos de flip-flops, incluindo o flip-flop R-S, que pode ser implementado com portas lógicas ou transistores e tem duas saídas Q e Q barra. O documento também descreve flip-flops controlados por clock e na configuração mestre-escravo.