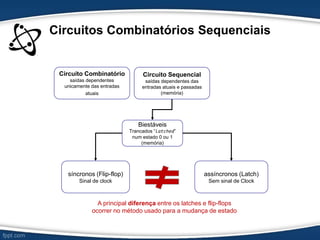

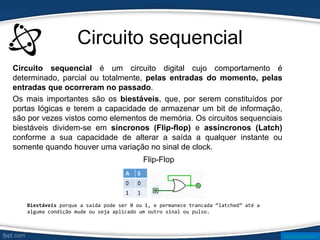

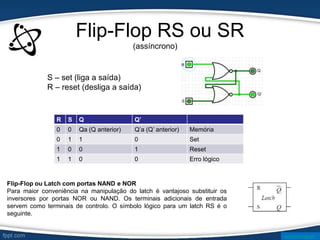

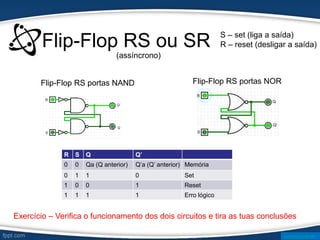

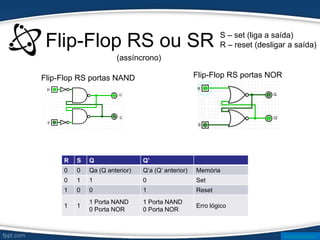

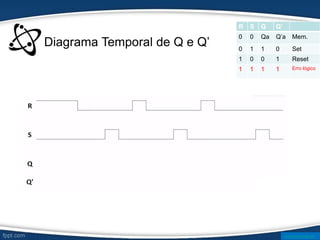

Os circuitos sequenciais dependem das entradas atuais e passadas, diferente dos combinatórios que dependem apenas das entradas atuais. Os biestáveis como latches e flip-flops armazenam um bit de informação e podem mudar de estado assincronamente ou com um sinal de clock. A principal diferença entre latches e flip-flops é o método para mudança de estado.