O documento apresenta uma introdução aos circuitos sequenciais síncronos, abordando os seguintes tópicos:

1) A diferença entre circuitos combinatórios e sequenciais e a noção de memória nos circuitos sequenciais;

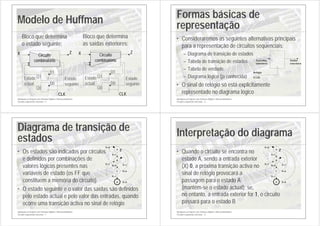

2) As formas básicas de representação de circuitos sequenciais, incluindo diagrama de transição de estados e tabela de verdade;

3) Os conceitos de estado atual, estado seguinte, flip-flops e o modelo de Huffman para circuitos sequenciais síncronos.

![Introdução ao Projecto com Sistemas Digitais e Microcontroladores

Circuitos sequenciais síncronos - 21

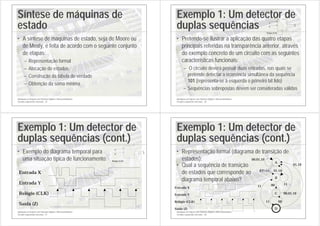

Exemplo 1: Um detector de

janela

• Apresente o diagrama de transição de estados para

um circuito com uma entrada, à qual chegam

continuamente (em forma série) palavras de 3 bits, e

com uma saída, que deverá ser colocada em 1

sempre que a palavra lida pertença ao intervalo [2,5]

• Assuma que a saída é considerada válida apenas

durante cada terceiro ciclo de relógio, após o que se

inicia imediatamente a leitura de uma nova sequência

Introdução ao Projecto com Sistemas Digitais e Microcontroladores

Circuitos sequenciais síncronos - 22

Exemplo 1: Um detector de

janela (conclusão)

E

1

F

A

D

C

B

0

0

1

1

0

1

0

0,1

0,1

Assumindo que o bit mais

significativo é lido em

primeiro lugar, concluímos

facilmente que as sequências

que devem colocar a saída

em 1 são aquelas nas quais

os dois primeiros bits lidos

são diferentes: 010 (2), 011

(3), 100 (4) e 101 (5).

Introdução ao Projecto com Sistemas Digitais e Microcontroladores

Circuitos sequenciais síncronos - 23

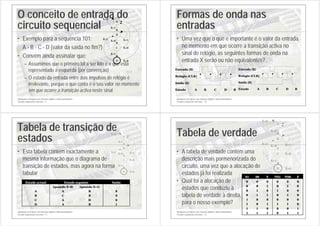

Exemplo 2: Um votador

sequencial

• Apresente o diagrama de transição de estados para

um circuito com uma entrada e uma saída, que

deverá ser colocada em 1 sempre que a entrada se

mantiver no mesmo estado durante pelo menos dois

impulsos de relógio consecutivos (voltando a 0

quando esta situação deixar de ter lugar)

Introdução ao Projecto com Sistemas Digitais e Microcontroladores

Circuitos sequenciais síncronos - 24

Exemplo 2: Um votador

sequencial (conclusão)

A

0

B

C

D E

1

1

0

0

1

0

1

0

1

A: Estado inicial - B: Estado onde já foi lido o

primeiro 0 - C: Estado onde já foi lido o primeiro 1 -

D: Estado onde já foram lidos dois 0 (e portanto a

saída está em 1)

- E: Estado onde

já foram lidos

dois 1 (e

portanto a saída

está em 1).](https://image.slidesharecdn.com/slidescircuitossequenciais-230117163927-36847e20/85/Slides-Circuitos-Sequenciais-pdf-6-320.jpg)

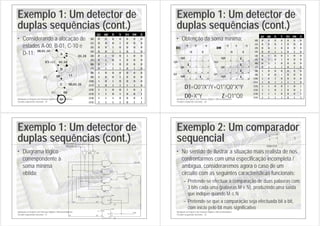

![Introdução ao Projecto com Sistemas Digitais e Microcontroladores

Circuitos sequenciais síncronos - 49

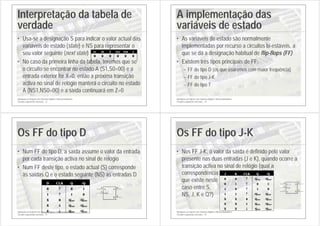

Contadores

(74x161)

TC

15

Q0

14

Q1

13

CP

2

Q2

12

CEP

7

D0

3

MR

1

D1

4

D2

5

D3

6

CET

10

Q3

11

PE

9

CTR DIV 16

/1,2D

1

9

7

10

2

3

4

5

6

4 CT=15

14

13

12

11

15

R

M1

G3

G4

C2/1,3,4<-

Qn TC

Dn

/PE

CET

CEP

CP

/MR

H

H

L Reset

H

h

Modo de

operação

Saídas

Entradas

h

X

X

X

X

X

X

X

X

X

X

X

X X

X

X

X

h h h

h

h

h

l

l

l

l

l

L

L

L

L

L

H

C

qn

qn

(a)

(a)

(a)

Carga

paralela

Contagem

Mantém

H = Nível lógico "alto" (1)

h = O nível H tem que estar presente um

"setup time" antes da subida no relógio

l = O nível L tem que estar presente um

"setup time" antes da subida no relógio

L = Nível lógico "baixo" (0)

C = Contagem

= Subida no relógio

X = "tanto faz" (don't care)

qn = a letra pequena indica o estado

da saída antes da subida no relógio

(a) A saída está em H quando CET estiver em H e o

contador estiver no último estado da contagem (HHHH)

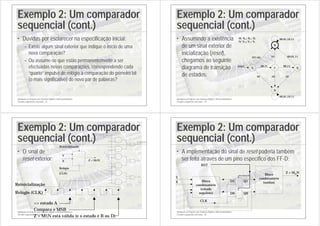

Introdução ao Projecto com Sistemas Digitais e Microcontroladores

Circuitos sequenciais síncronos - 50

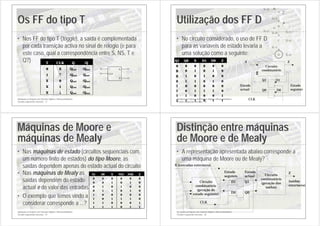

Contadores

(74x192)

D1

1

Q1

2

Q0

3

CPU

5

Q2

6

D0

15

Q3

7

D2

10

TCU

12

PL

11

D3

9

TCD

13

CPD

4

MR

14

3D

CTR DIV 10

3

2

6

7

13

12

11

5

4

14

15

1

10

9

C3

2+

1-

R

/2CT=0

/1CT=9

G1

G2

D2

D1

D0

CPU

/PL

MR

H

H

Q0 Q1 Q2

L

Modo de

operação

Q3

Saídas

Entradas

D3

CPD

Contagem ascendente

Contagem descendente

Reset assíncrono

Carga paralela

L

L

L

L

L

L

L

L

L

L

L

L L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

/TCU /TCD

H

H

H

H

H

H

H

H

H

H

H

L

L

L

H

H

H

H

H

H

H

H

H

H

H (2) H

H (3)

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

Qn = Dn

Qn = Dn

Contagem

ascendente

Contagem

descendente

H = Nível lógico "alto" (1)

L = Nível lógico "baixo" (0)

X = "tanto faz" (don't care)

(2) /TCU = CPU quando se atinge o máximo na contagem ascendente (HLLH)

(3) /TCD = CPD quando se atinge o mínimo na contagem descendente (LLLL)

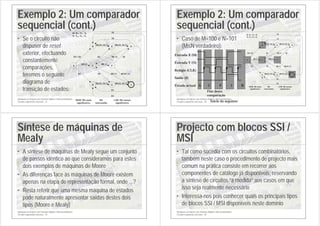

Introdução ao Projecto com Sistemas Digitais e Microcontroladores

Circuitos sequenciais síncronos - 51

Contadores (74x192, cont.)

Reset Preset Contagem ascendente Contagem descendente

0 7 9 0 1

8 0 9 8

1

2 7

MR (1)

/PL

D0

D1

D2

D3

CPU (2)

CPD (2)

Q0

Q1

Q2

Q3

/TCU

/TCD

(1)

(2) Quando em contagem ascendente, a entrada de relógio para a contagem

descendente (CPD) deve estar em H; quando em contagem descendente, a entrada

de relógio para a contagem ascendente (CPU) deve estar em H

O sinal MR sobrepõe-se às entradas de carga, dados e contagem

Introdução ao Projecto com Sistemas Digitais e Microcontroladores

Circuitos sequenciais síncronos - 52

Exemplo 1: Um detector de

sequência

• Pretende-se projectar um circuito que efectue

constantemente a leitura de palavras com 3 bits

(valor ∈ [0..7]) e produza uma saída que indique

quando a palavra lida pertence ao intervalo [2,5]

• O bit mais significativo é primeiro a ser lido e a saída

é válida apenas em cada terceiro impulso de relógio

• Pretende-se uma solução baseada no registo de

deslocamento 74x195](https://image.slidesharecdn.com/slidescircuitossequenciais-230117163927-36847e20/85/Slides-Circuitos-Sequenciais-pdf-13-320.jpg)