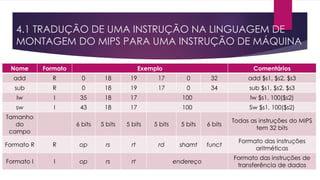

1. O documento descreve o conjunto de instruções MIPS e suas características. 2. As instruções MIPS possuem três operandos fixos e operam apenas em registradores. 3. É necessário transferir dados entre registradores e memória usando instruções de load e store.

![3.2. COMPILAÇÃO DE UMA ATRIBUIÇÃO COM

UM OPERANDO NA MEMÓRIA

EXEMPLO:

Traduza o comando de atribuição abaixo, escrito em C, para a

linguagem de montagem do MIPS, em que A é um array de 100

palavras.

g = h + a[8];

SOLUÇÃO:

G = $s1, H = $s2; $s3 = endereço-base (endereço inicial do array)](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-29-320.jpg)

![ Há uma única operação no trecho de código em C, que é a soma!

Um dos operandos da operação está na memória (no caso, o array)

O operando da memória deve ser transferido (copiado) para um

registrador (A[8])

3.2. COMPILAÇÃO DE UMA ATRIBUIÇÃO COM

UM OPERANDO NA MEMÓRIA](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-30-320.jpg)

![ CÁLCULO DO ENDEREÇO:

Onde está, na memória, o elemento do array que preciso transferir?

Endereço na memória = endereço-base + índice

O valor resultante do cálculo também deve ser guardado em um

registrador temporário para uso posterior

Portanto:

lw = $t0, 8 ( $s3) #O registrador temporário $t0

recebe a[8]

3.2. COMPILAÇÃO DE UMA ATRIBUIÇÃO COM

UM OPERANDO NA MEMÓRIA](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-31-320.jpg)

![ Agora, o valor de a[8] já está em um registrador temporário para

manipulação ($t0)

O que precisamos fazer agora? Somar o valor de h com o valor que está

em a[8]

Portanto:

add $s1, $s2, $t0 # g recebe h + a[8]

3.2. COMPILAÇÃO DE UMA ATRIBUIÇÃO COM

UM OPERANDO NA MEMÓRIA](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-32-320.jpg)

![g = h + a[8];

É o mesmo que:

lw = $t0, 8 ( $s3)

add $s1, $s2, $t0

3.2. COMPILAÇÃO DE UMA ATRIBUIÇÃO COM

UM OPERANDO NA MEMÓRIA](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-33-320.jpg)

![ EXERCÍCIOS:

Traduza o comando de atribuição abaixo, escrito em C, para a

linguagem de montagem do MIPS, em que A é um array de 100

palavras.

w = x + y[4];

SOLUÇÃO

??????

3.2. COMPILAÇÃO DE UMA ATRIBUIÇÃO COM

UM OPERANDO NA MEMÓRIA](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-34-320.jpg)

![ O endereçamento de bytes afeta a indexação dos arrays

O deslocamento a ser adicionado ao conteúdo do registrador-base

deve ser 4 x Y, de modo que o elemento do array selecionado pela

instrução load seja a[Y] e não a[Y/4]

3.A – INTERFACE HARDWARE/SOFTWARE](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-39-320.jpg)

![3.3. COMPILAÇÃO USANDO

INSTRUÇÕES DE LOAD E STORE

EXEMPLO:

Dado o trecho de código em linguagem C abaixo, qual é o código de

montagem em linguagem MIPS?

a[12] = h + a[8];

SOLUÇÃO:

Uma única operação (soma)

Dois operandos na memória (a[12] e a[8])](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-41-320.jpg)

![3.3. COMPILAÇÃO USANDO

INSTRUÇÕES DE LOAD E STORE

EXEMPLO:

Dado o trecho de código em linguagem C abaixo, qual é o código de

montagem em linguagem MIPS?

z[16] = y + z[12];

SOLUÇÃO:

??????](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-43-320.jpg)

![3.4. COMPILAÇÃO USANDO UMA

VARIÁVEL PARA INDEXAR O ARRAY

EXEMPLO:

Dado o trecho de código em linguagem C abaixo, qual o código MIPS

correspondente?

g = h + a[i];

SOLUÇÃO:

Instrução com uma operação (soma)

Instrução com uma transferência da memória](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-44-320.jpg)

![3.4. COMPILAÇÃO USANDO UMA

VARIÁVEL PARA INDEXAR O ARRAY

1º passo:

Calcular o endereço de a[i], para isto:

Multiplicar o valor do índice i por 4 (i *4)

Fazer a multiplicação (i * 4) usando somas:

i + i = 2i

2i + 2i = 4i

add $t1, $s4, $s4 #2*i

add $t1, $t1, $t1 #4*i

Em seguida, obter o

endereço de a[i]

somando $t1 ao

endereço-base de a,

armazenado em #s3

add $t1, $t1, $s3

#a[i] = (4*i+$s3)](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-45-320.jpg)

![3.4. COMPILAÇÃO USANDO UMA

VARIÁVEL PARA INDEXAR O ARRAY

2º passo:

Usar o endereço calculado para carregar a[i] em um registrador

lw $t0,0($t1) #$t0=a[i]

Agora somar:

add $s1, $s2, $t0 #g=h+a[i]](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-46-320.jpg)

![3.4. COMPILAÇÃO USANDO UMA

VARIÁVEL PARA INDEXAR O ARRAY

g = h + a[i];

Código completo:

add $t1, $s4, $s4 #2*i

add $t1, $t1, $t1 #4*i

add $t1, $t1, $s3 #a[i]=(4*i+$s3)

lw $t0,0($t1) #$t0=a[i]

add $s1, $s2, $t0 #g=h+a[i]](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-47-320.jpg)

![3.4. COMPILAÇÃO USANDO UMA

VARIÁVEL PARA INDEXAR O ARRAY

EXEMPLO:

Dado o trecho de código em linguagem C abaixo, qual o código MIPS

correspondente?

y = x + w[i];

SOLUÇÃO:

????](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-48-320.jpg)

![Nome Exemplo Comentários

32 registradores $s0, $s1

Posições de acesso rápido para armazenamento de dados.

Os dados devem estar em registradores para que as

operações aritméticas possam ser relizadas.

230 palavras de memória

Memória[0]

Memória[4]

Estas posições só são acessadas por instruções de

transferência de dados.

Endereça bytes

Os endereços de palavras consecutivas diferem de 4

unidades.

3. OPERANDOS DE HARDWARE DE MÁQUINA

TABELA 2: OPERANDOS DO MIPS](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-54-320.jpg)

![3. OPERANDOS DE HARDWARE DE MÁQUINA

Categoria Instrução Exemplo Significado Comentário

Aritmética

add add $s1, $s2, $s3 $s1 = $s2 + $s3

Três operandos

Dados em registradores

subtract sub $s1, $s2, $s3 $s1 = $s2 - $s3

Três operandos

Dados em registradores

Transferência

de dados

load word lw $s1, 100($s2) $s1 = Memória[$s2 + 100]

Memória Registrador

store word sw $s1, 100($s2) Memória[$s2 + 100] = $s1

Registrador Memória

TABELA 3: Arquitetura do MIPS](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-55-320.jpg)

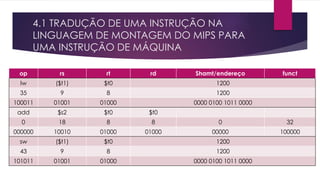

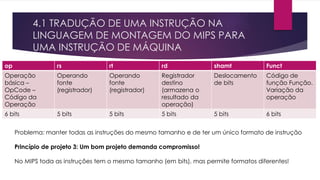

![4.1 TRADUÇÃO DE UMA INSTRUÇÃO NA

LINGUAGEM DE MONTAGEM DO MIPS PARA

UMA INSTRUÇÃO DE MÁQUINA

Exemplo:

g = h + A[8];

lw $t0, 32($s3) #Registrador temporário recebe a[8]

A distinção entre os formatos de instruções no MIPS se dá pelo valor do primeiro

campo

op rs rt Endereço

lw $s3 $t0 32

35 19 8 32

6 bits 5 bits 5 bits 16 bits](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-63-320.jpg)

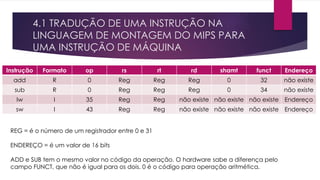

![4.1 TRADUÇÃO DE UMA INSTRUÇÃO NA

LINGUAGEM DE MONTAGEM DO MIPS PARA

UMA INSTRUÇÃO DE MÁQUINA

Exemplo: Dado o código em linguagem de alto nível A[300] = h +

A[300], converta-o para código MIPS, faça a representação de

linguagem de máquina e de código de máquina.

lw $t0, 1200 ($t1)

add $t0, $s2, $t0

sw $to, 1200($t1)](https://image.slidesharecdn.com/1-conjuntodeinstruesmips-introduo-140625082349-phpapp02/85/Conjunto-de-instrucoes-mips-introducao-65-320.jpg)