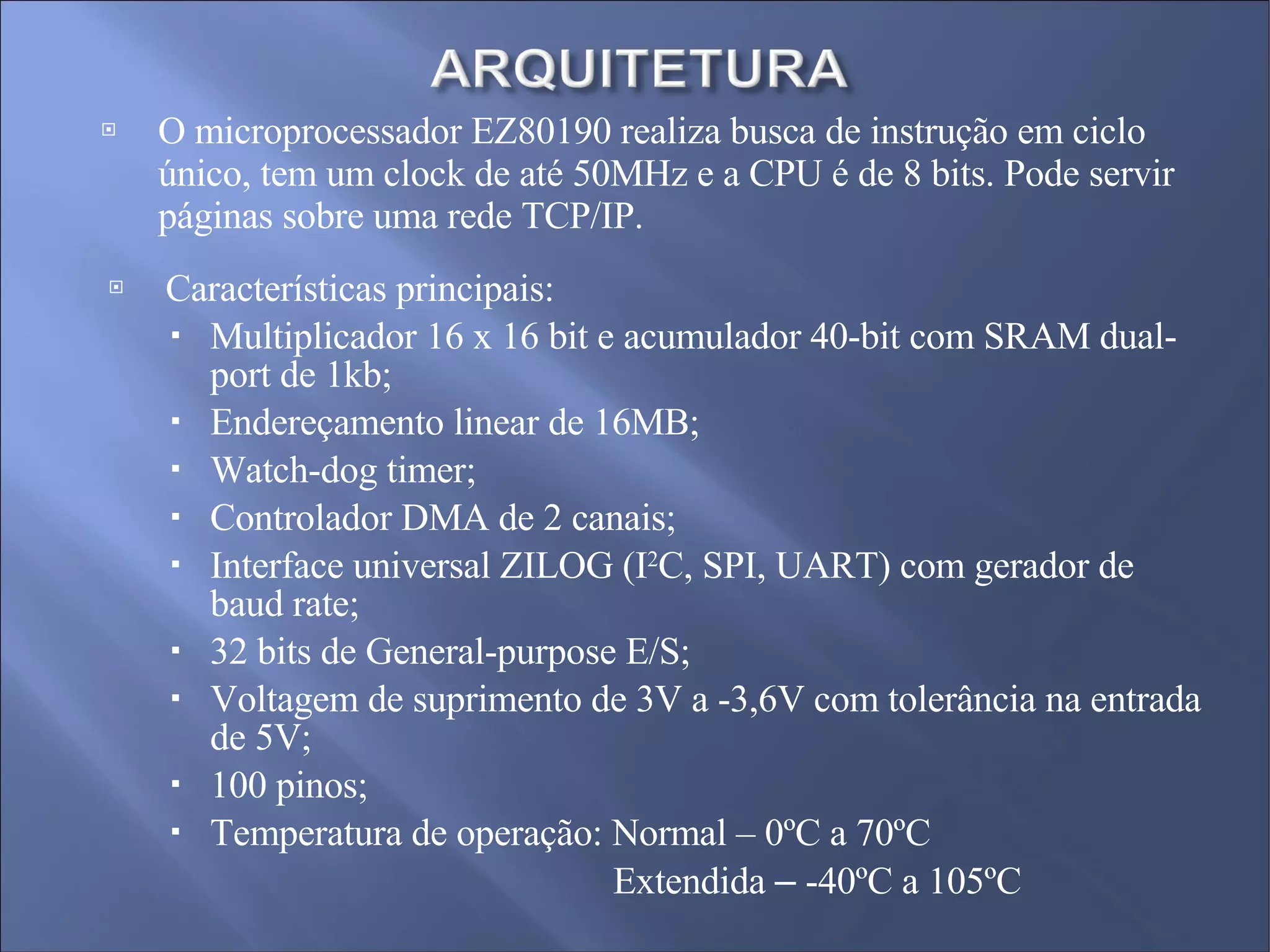

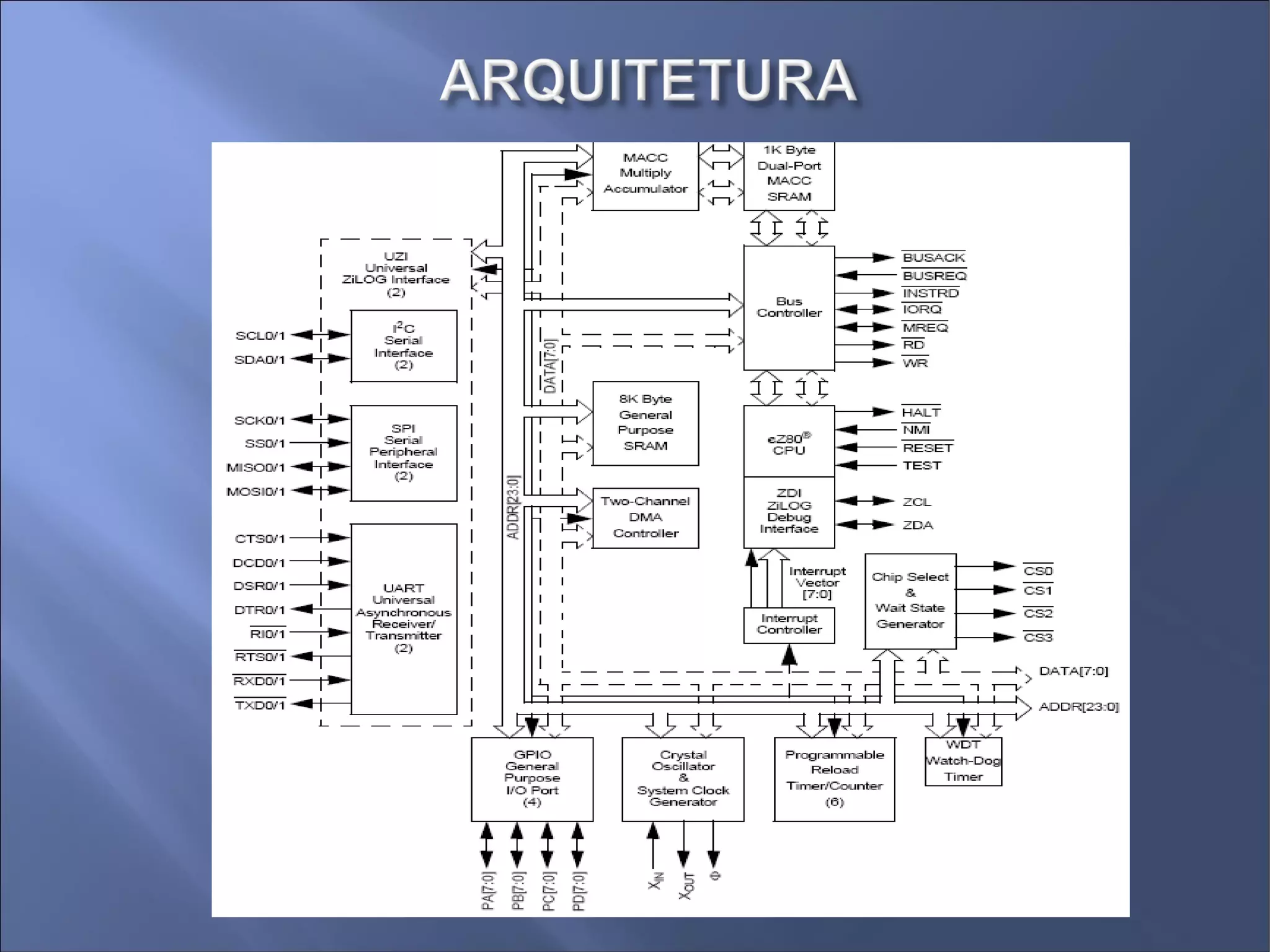

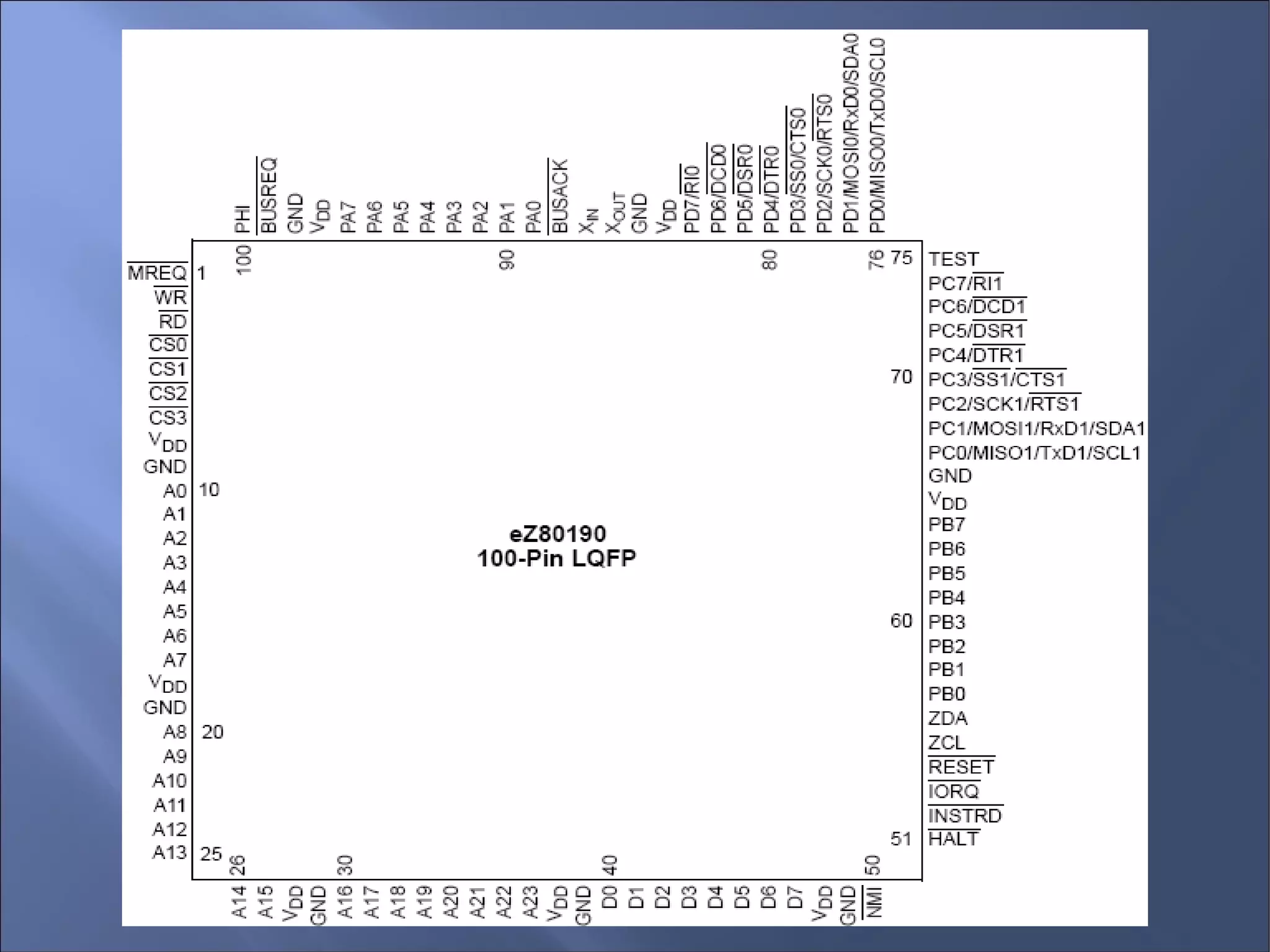

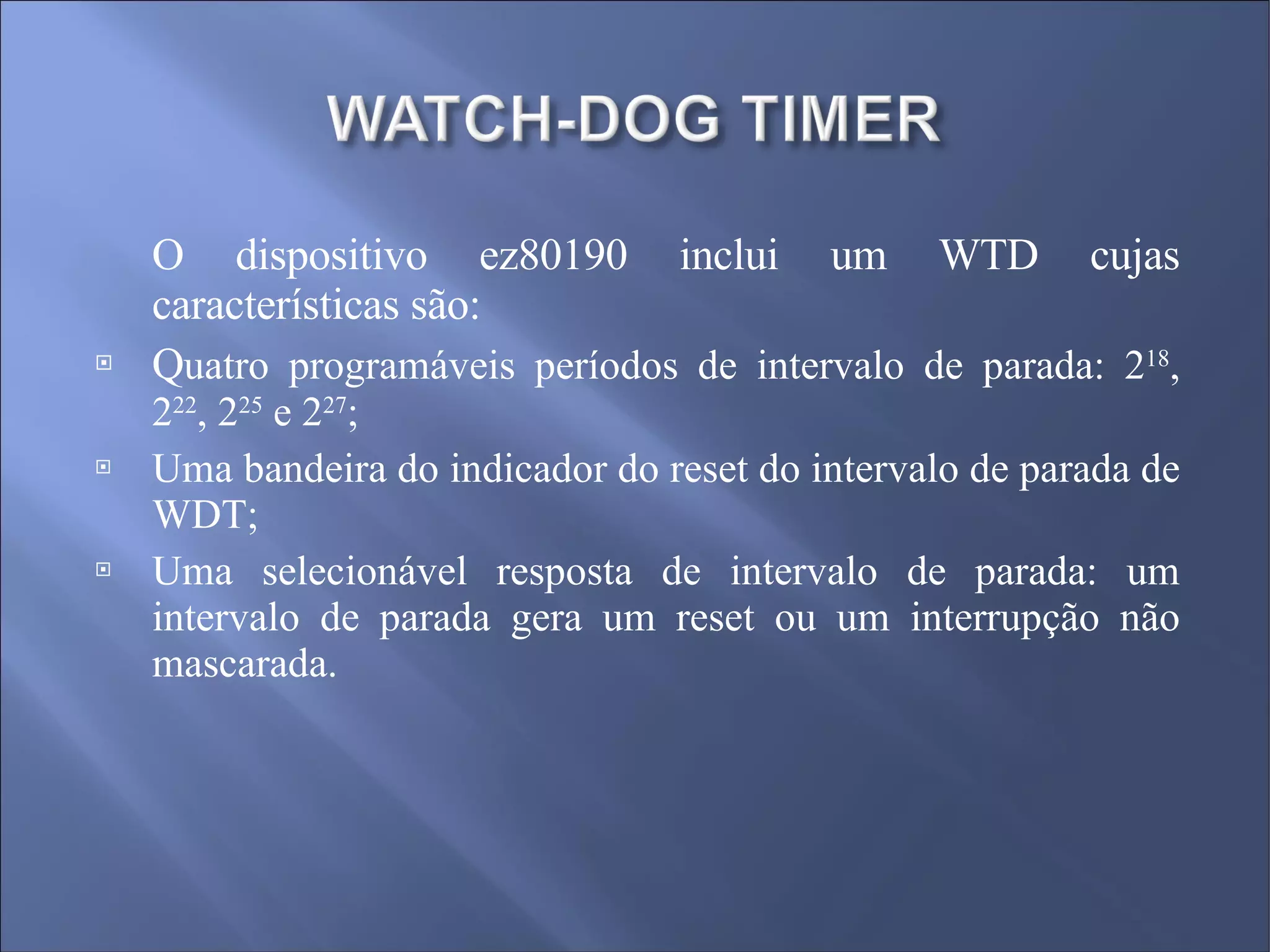

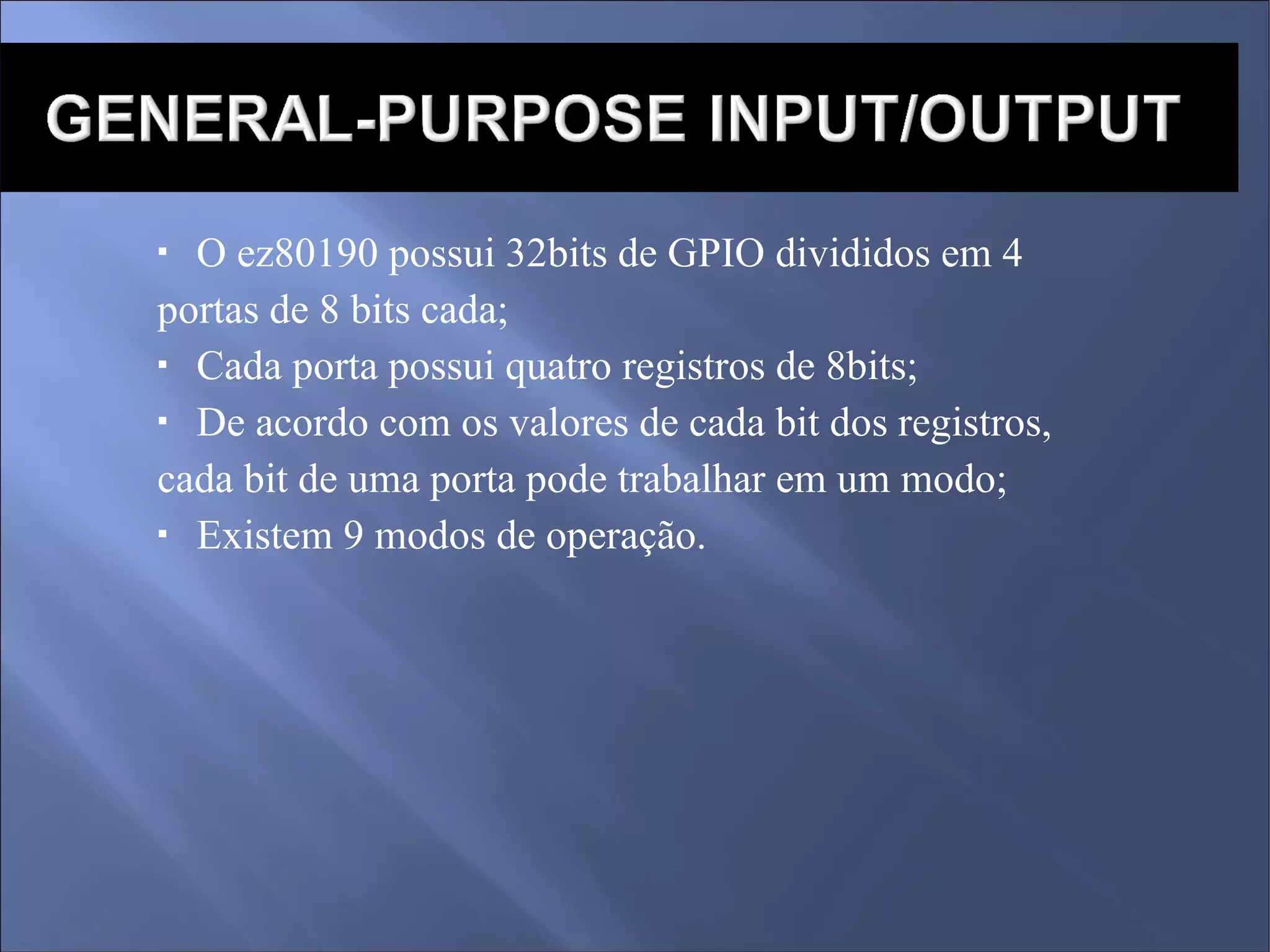

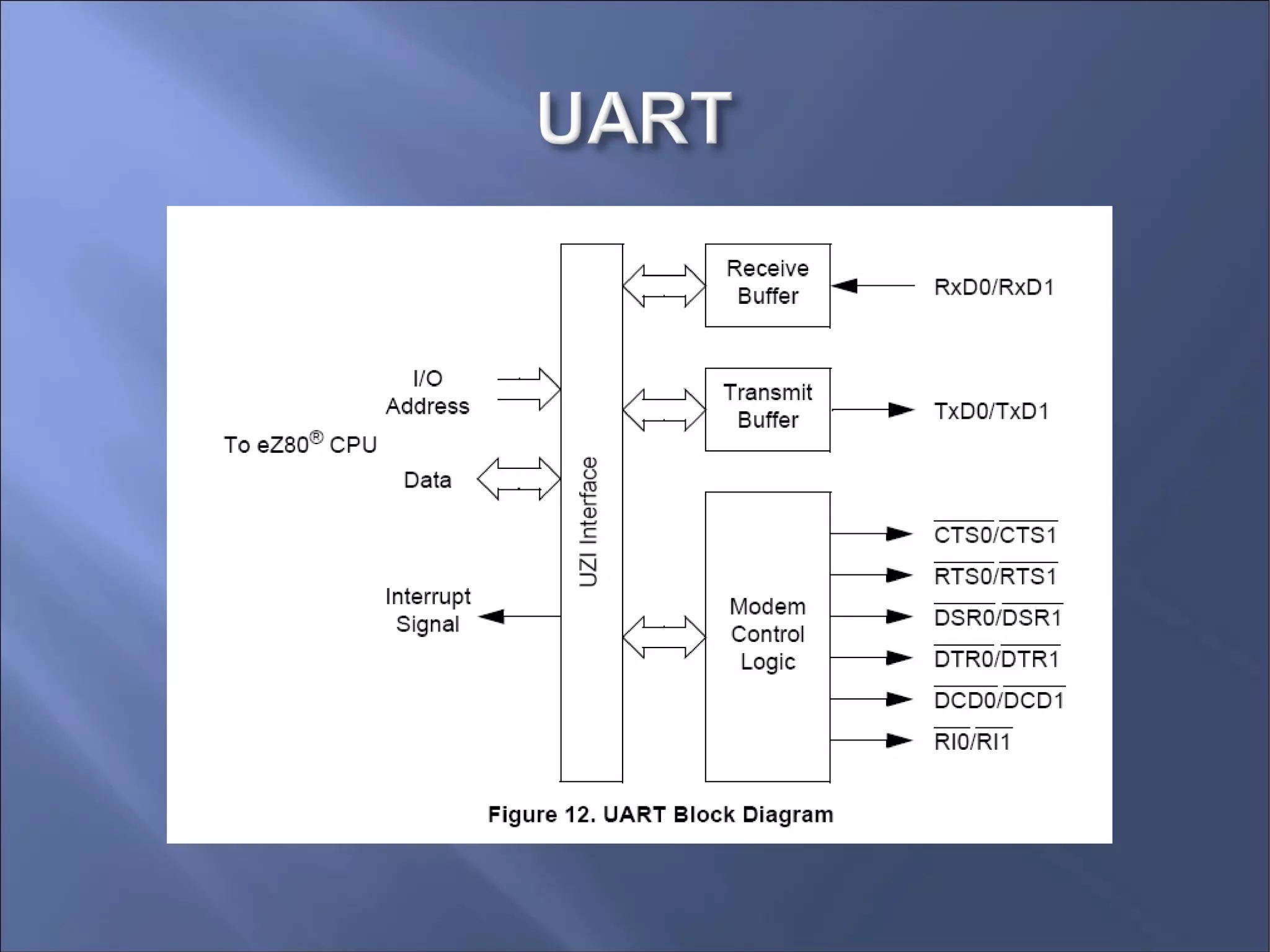

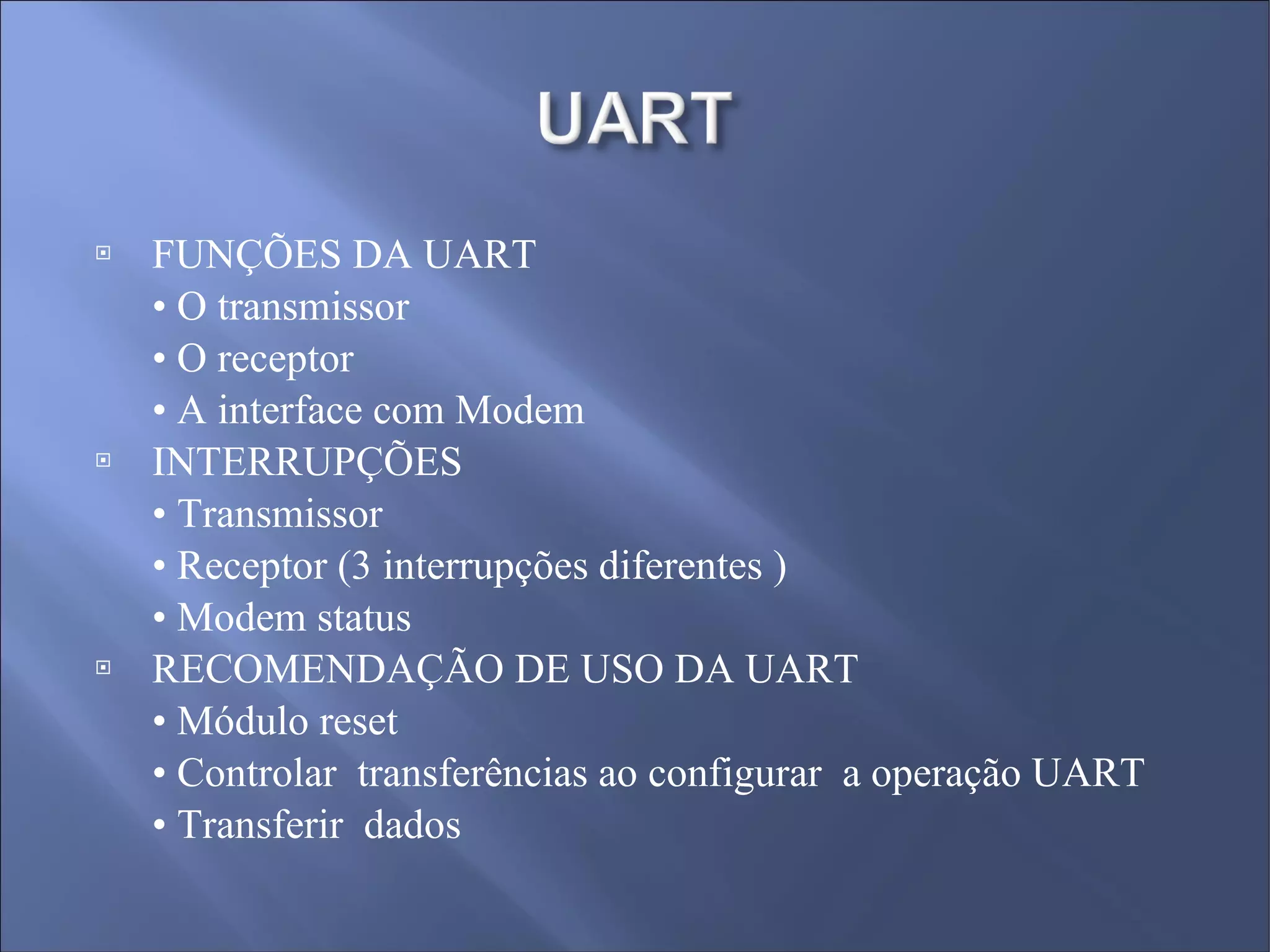

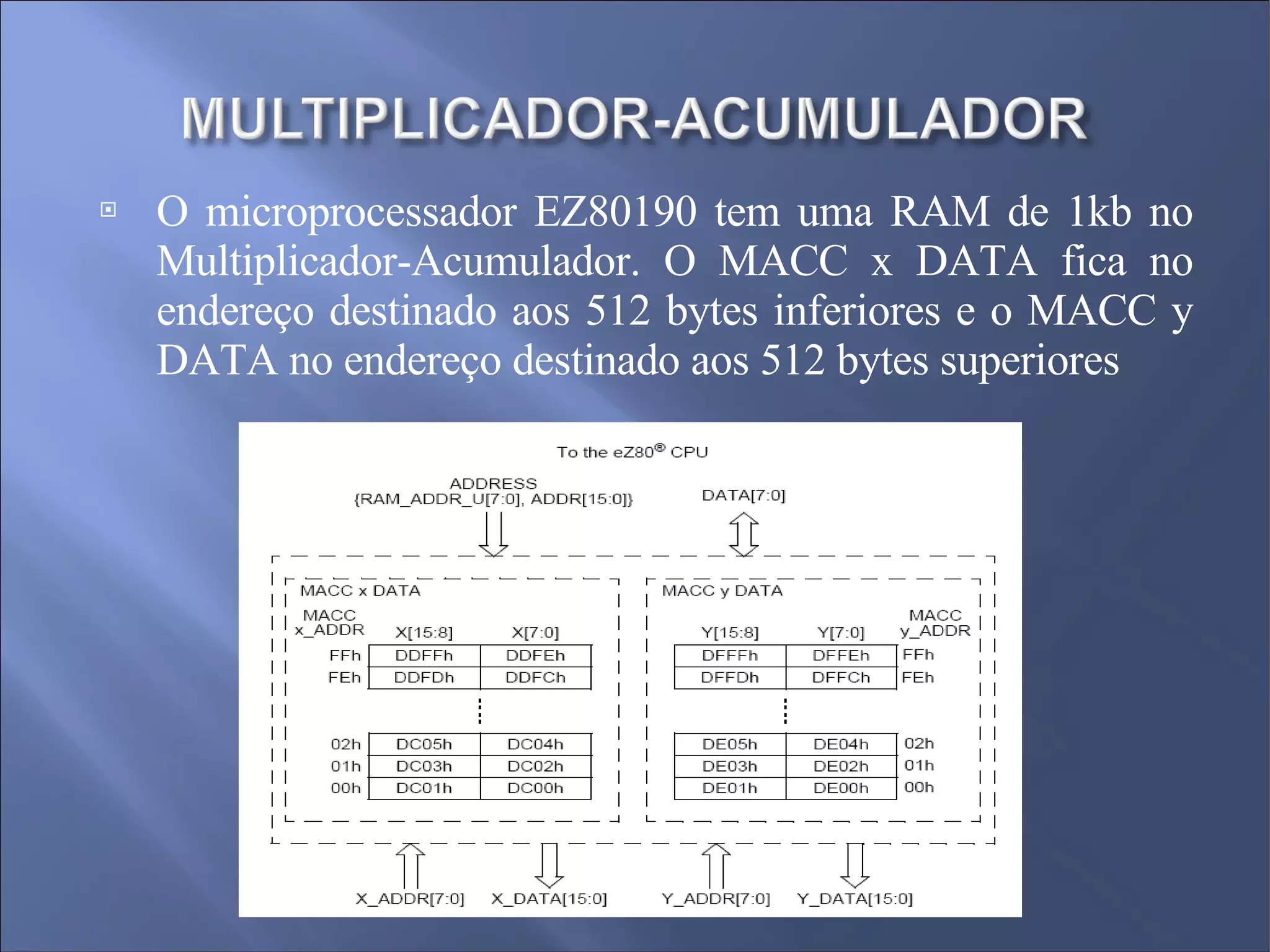

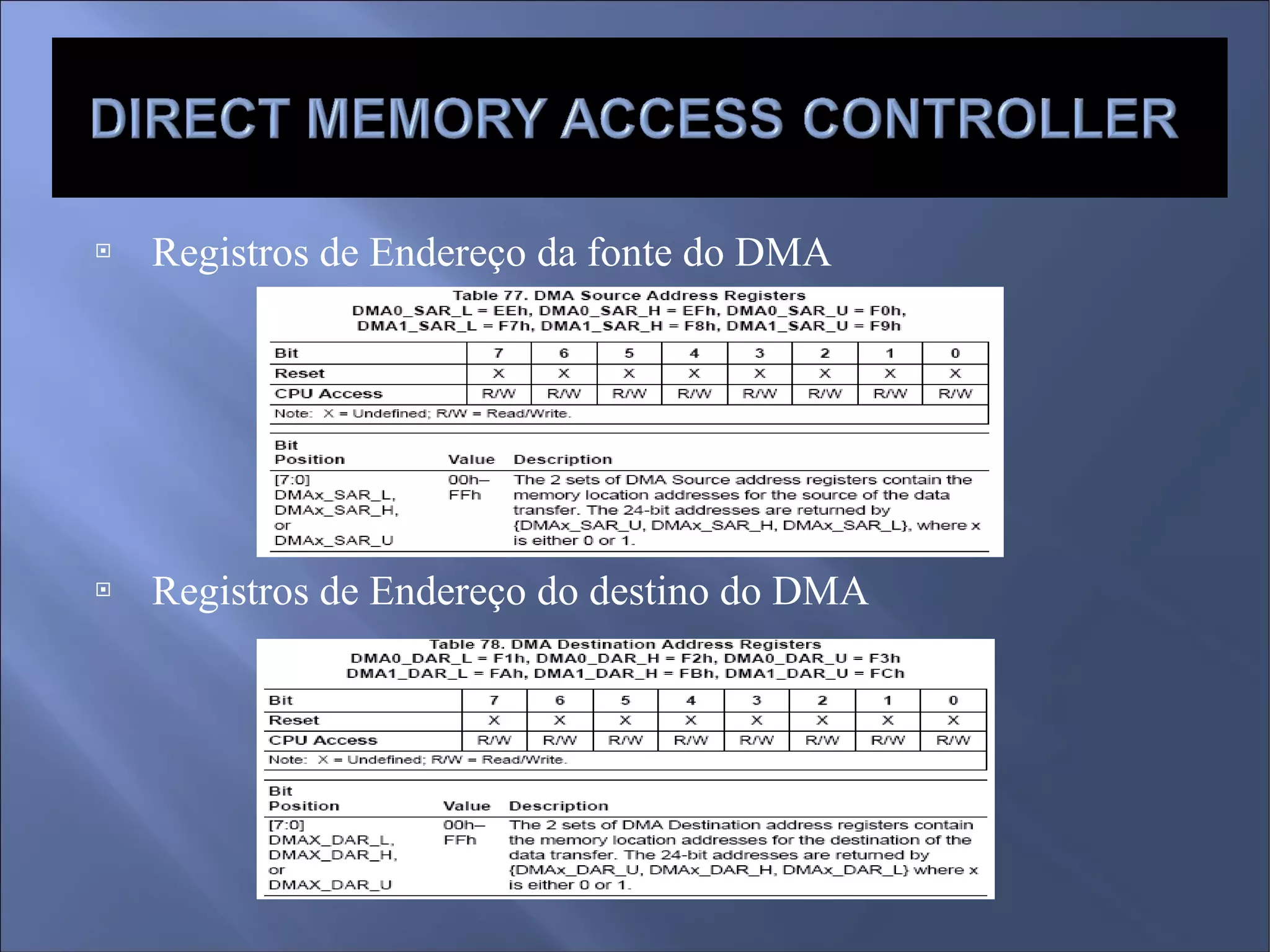

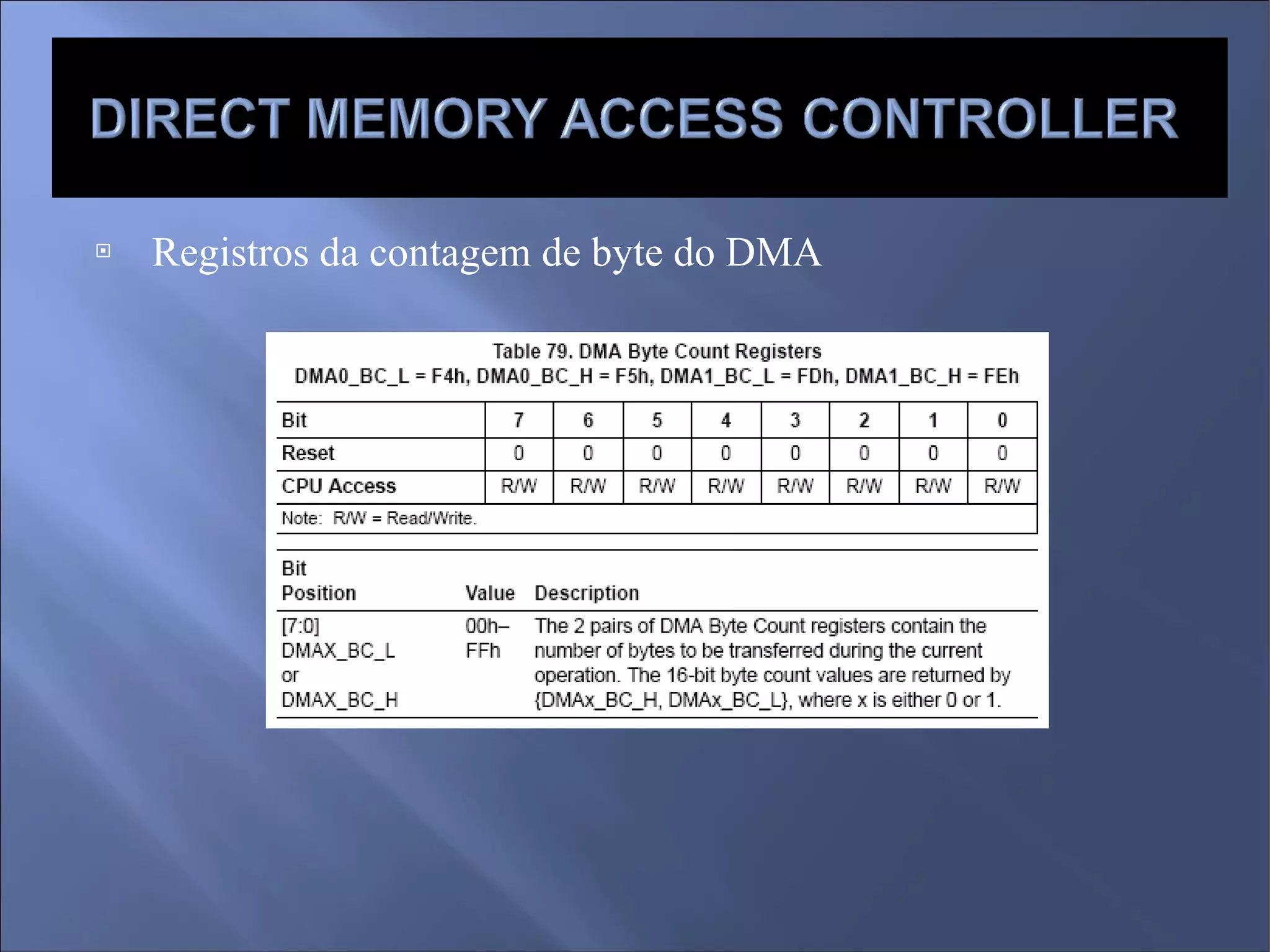

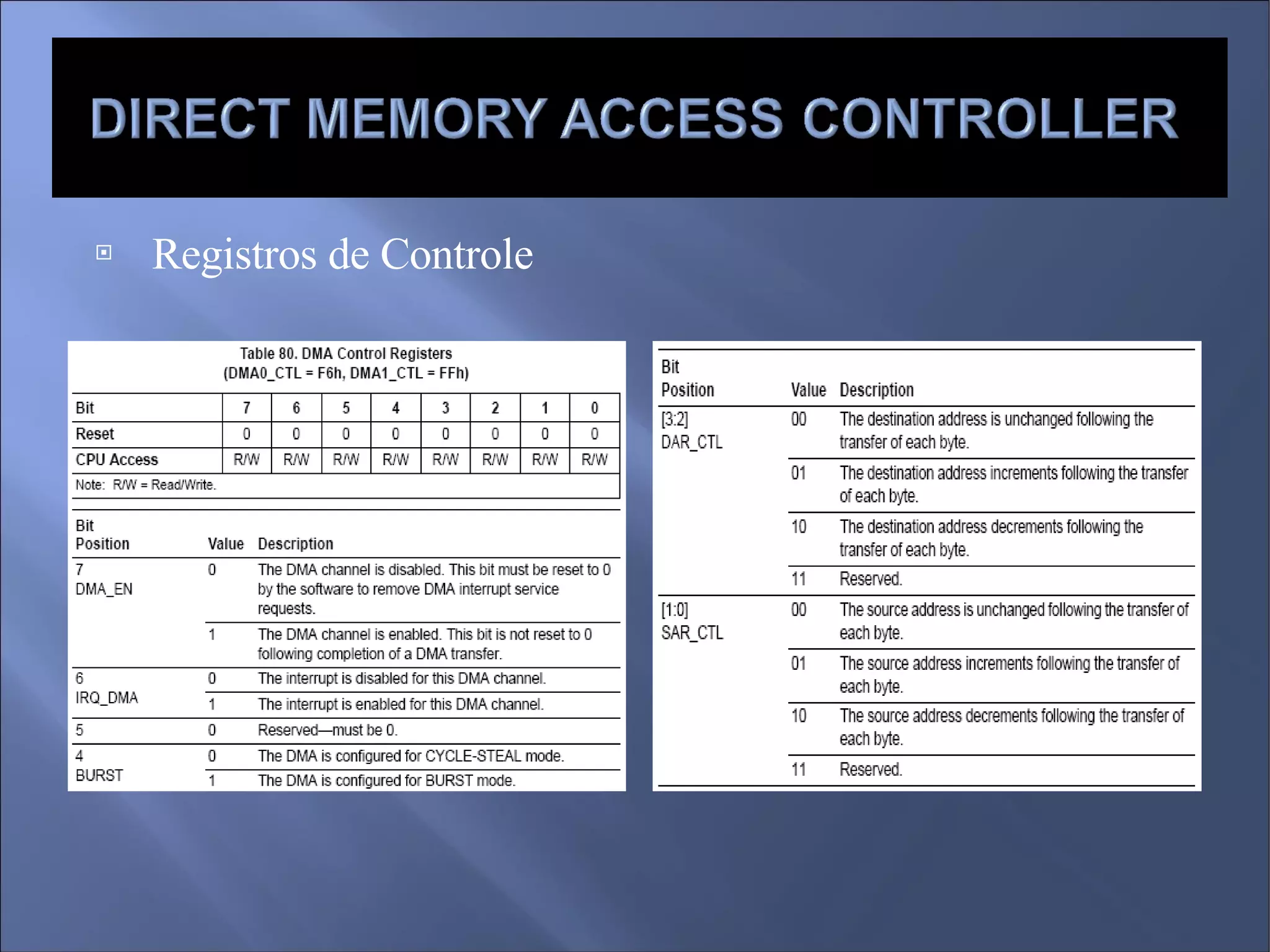

O microprocessador ez80190 possui características como clock de até 50MHz, CPU de 8 bits, endereçamento linear de 16MB e interface universal ZILOG. Ele inclui 6 timers programáveis, 32 bits de GPIO divididos em 4 portas e um Watchdog Timer com 4 períodos de intervalo programáveis. O dispositivo também suporta operações DMA e comunicação serial UART.

![DESCRIÇÃO FUNCIONAL RECOMENDAÇÃO DE USO DO GERADOR DE BAUD RATE • RESET • Setar UARTx_LCTL[7] para 1 para habilitar o acesso aos registros divisores do BRG. • Programar os registros BRGx_DLR_L e BRGx_DLR_H. • Resetar UARTx_LCTL[7] para 0 para desabilitar accesso aos registros divisores do BRG.](https://image.slidesharecdn.com/zilog-1213951507086601-9/75/Zilog-25-2048.jpg)

![[1] ez80190 ProductSpecification, disponível em: Site: http://www.zilog.com Acessado em 09/05/2008](https://image.slidesharecdn.com/zilog-1213951507086601-9/75/Zilog-39-2048.jpg)