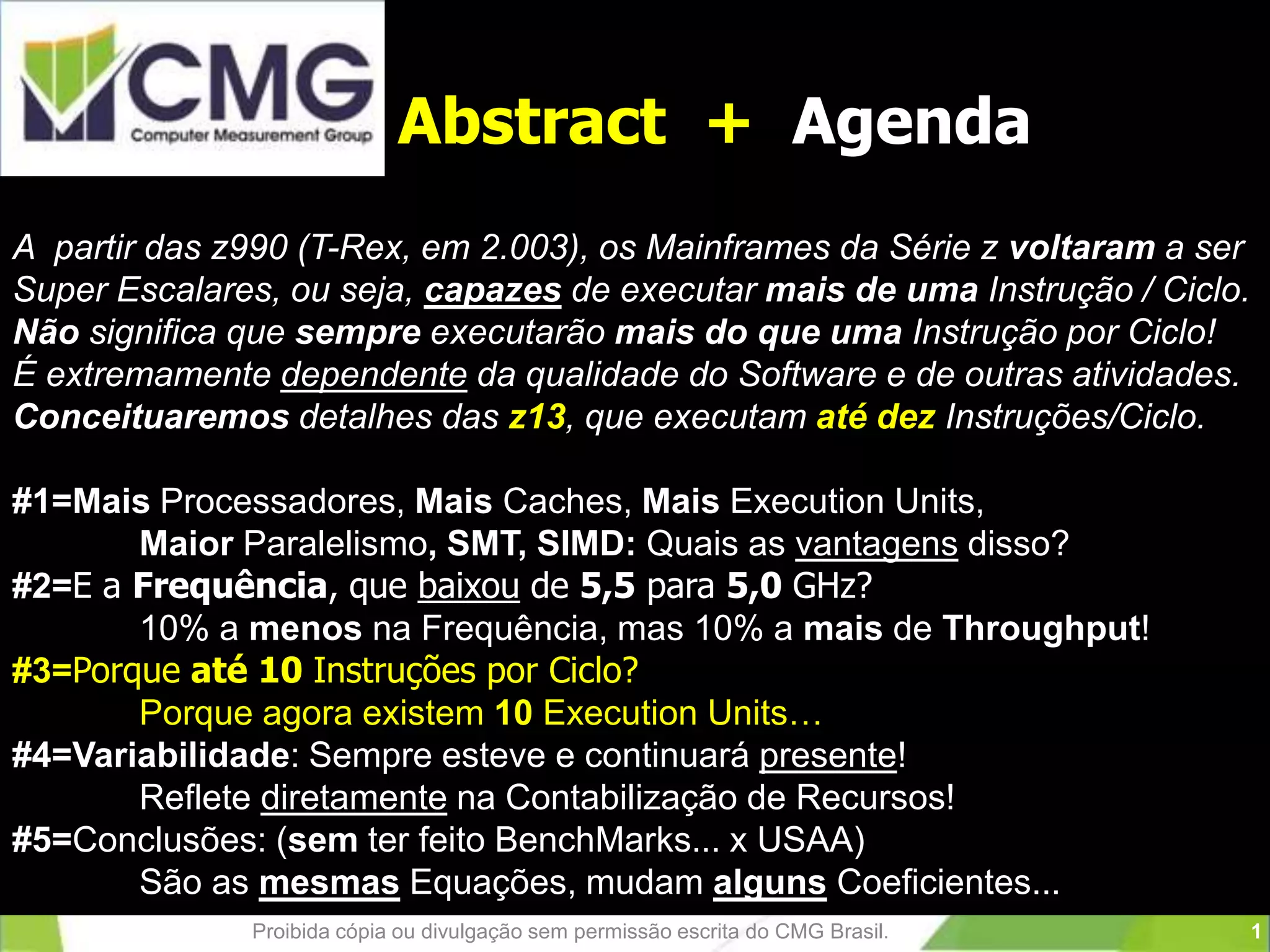

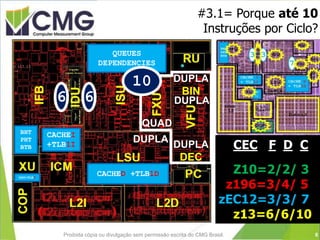

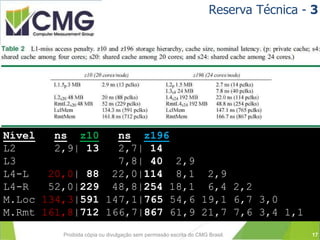

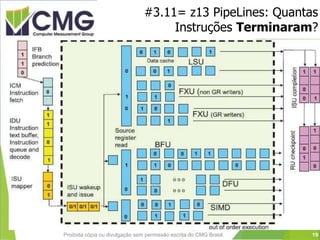

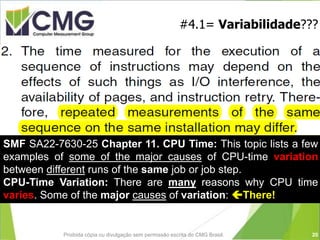

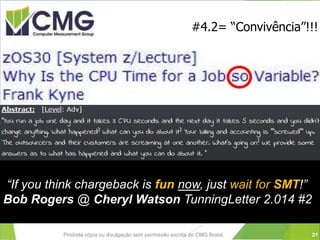

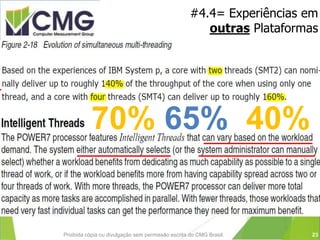

O documento analisa a evolução dos mainframes da série z, destacando melhorias na execução de instruções por ciclo, os impactos na frequência e avanços em unidades de execução e cache. As conclusões enfatizam a importância do entendimento da tecnologia z13 e desafios relacionados à variabilidade e ao uso de multi-threading. O autor menciona que a eficácia depende de muitos fatores, incluindo a qualidade do software e aplicações específicas.

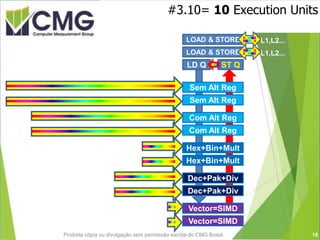

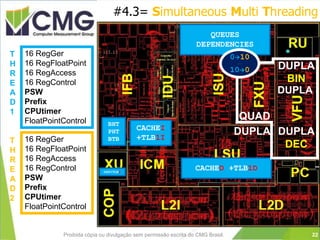

![#3.7= 2 Hex+Bin Floating Point Units+Mult

2 Vector Units (SIMD)

2 Decimal Floating Point Units+Div

Proibida cópia ou divulgação sem permissão escrita do CMG Brasil.

QUAD

DUALICACHE

+TLB1I

DCACHE +TLB1D

BHT

PHT

BTB DUAL

Decimal

DUAL

Binary

V

D e

U c

A t

L o

r

RU

PC

C

O

P

XU

9

6 6

BFU

Binary FloatPoint

HexaDec FltPoint

FxdPnt Multiplication

VXU

Vector (SIMD)

PM, ST, XM, XS

[Non Destructive]

32 128 bit Regs

Shared with 16 FltPt

DFU

Decimal FltPoint

Decimal Packed (DFX)

FxdPnt Division (FPD)

QUEUES

DEPENDENCIES

2 DEC

2 BIN

2 Vector

14](https://image.slidesharecdn.com/quantasinstrucoesporciclov9fundopreto-160520233358/85/Quantas-Instrucoes-por-Ciclo-14-320.jpg)

![#5 = Conclusões:

Proibida cópia ou divulgação sem permissão escrita do CMG Brasil.

[Sem ainda ter feito nenhum Benchmark...]

1 – Conhecer a ‘Tecnologia embarcada’ nas z13

2 – Ficar “de olho” nas Aplicações sensíveis aos GHz!

3 – Preparar-se para Simultaneous Multi Threading

4 – Continuar convivendo com as Variabilidades!

5 – Quantas Instruções? Ora, depende de quase tudo!

24](https://image.slidesharecdn.com/quantasinstrucoesporciclov9fundopreto-160520233358/85/Quantas-Instrucoes-por-Ciclo-24-320.jpg)