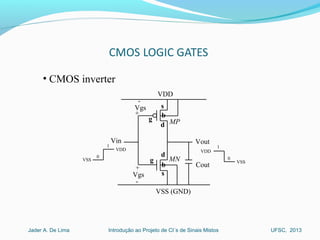

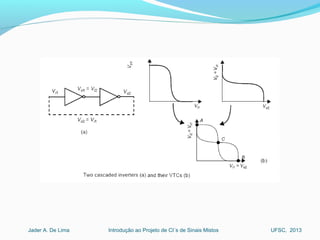

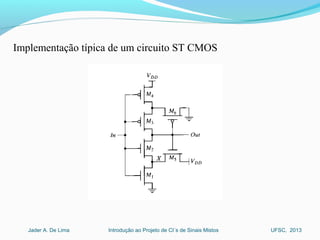

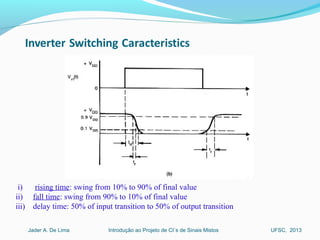

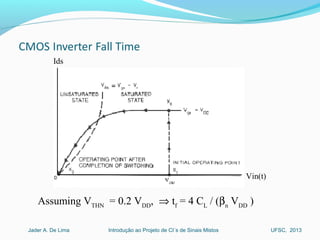

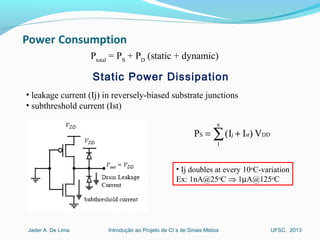

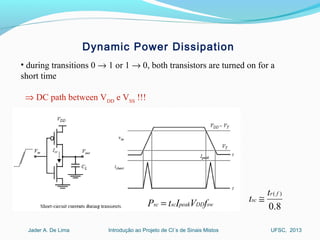

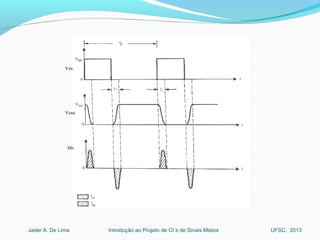

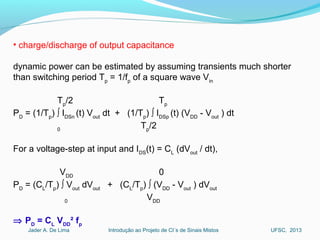

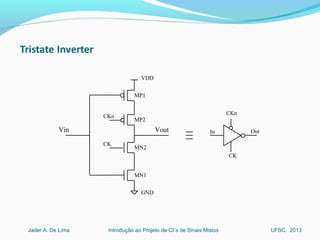

1) O documento discute circuitos lógicos básicos como inversores CMOS, margens de ruído, gatos de Schmitt e dissipação de potência em circuitos digitais.

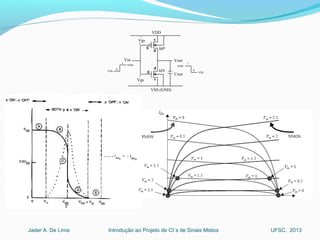

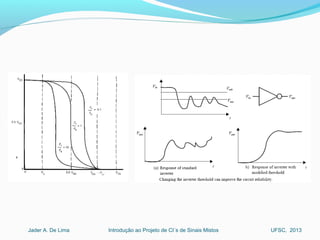

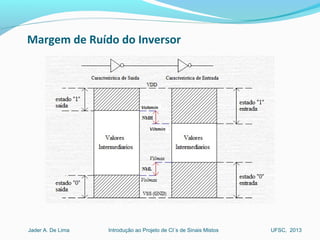

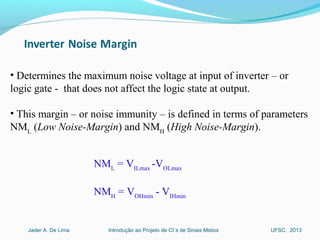

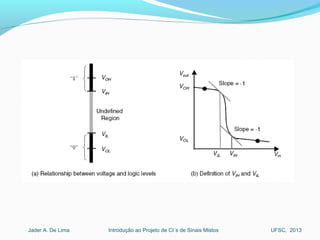

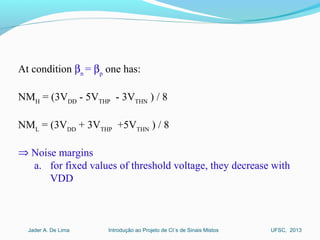

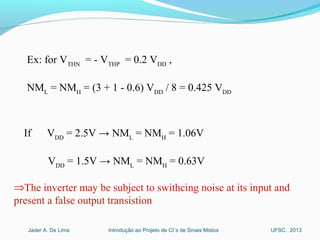

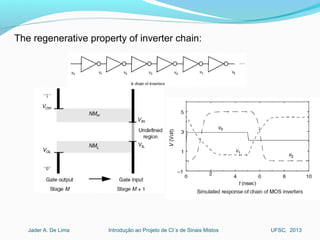

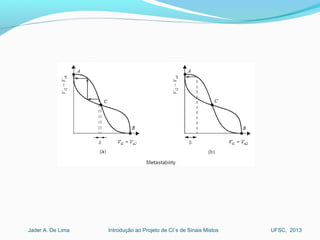

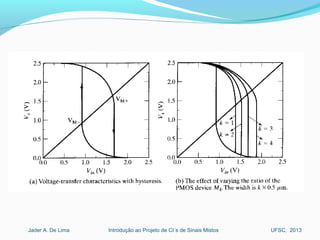

2) É apresentado o conceito de margem de ruído para inversores e como ela afeta a imunidade a ruído.

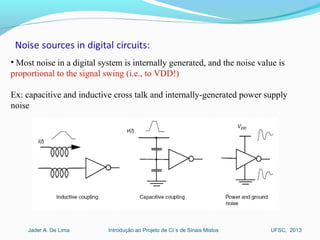

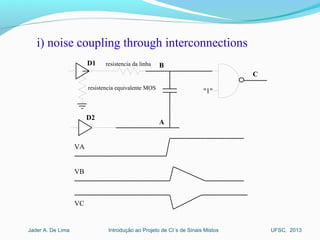

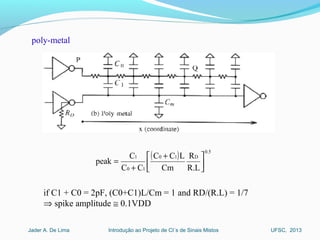

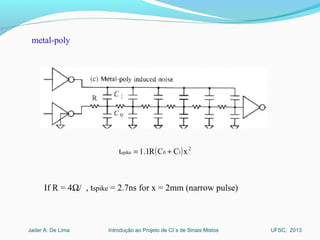

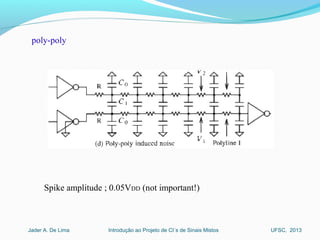

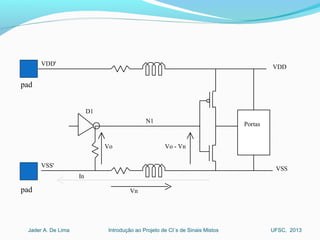

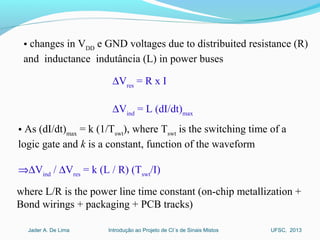

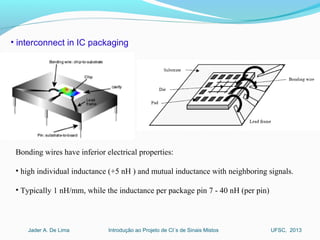

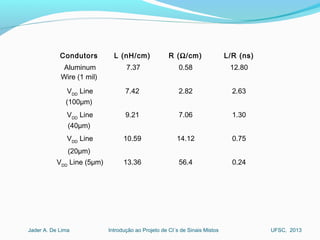

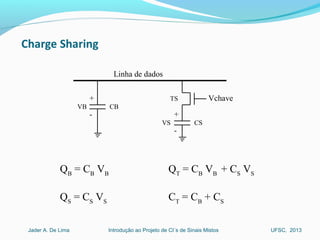

3) São descritas fontes internas de ruído em circuitos digitais, incluindo acoplamento capacitivo e variações na tensão de alimentação.