1. O documento discute a necessidade de memória em sistemas digitais para permitir que eles lidem com variáveis relacionadas ao tempo, como sequências de eventos.

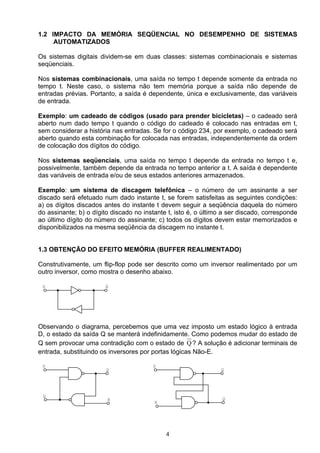

2. É introduzido o conceito de memória e dispositivos biestáveis que podem reter informações.

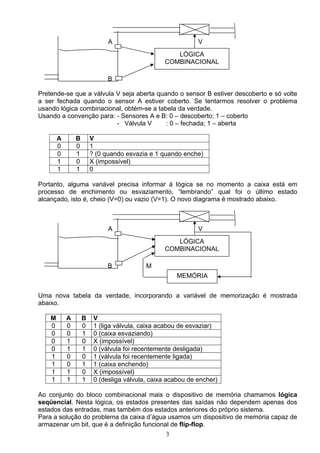

3. É usado o exemplo de um sistema de controle de nível de água para ilustrar como a memória permite que sistemas digitais resolvam problemas que envolvam a noção de tempo.