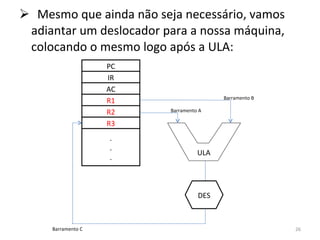

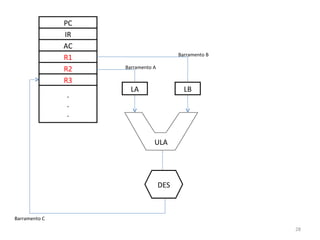

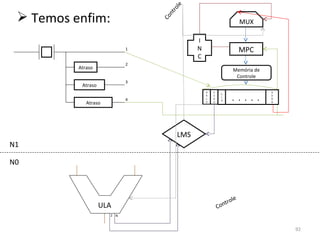

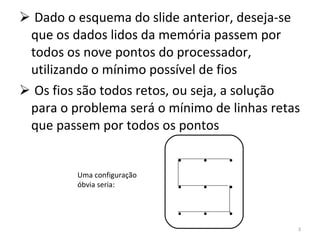

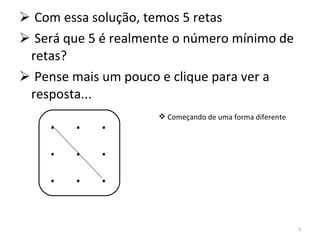

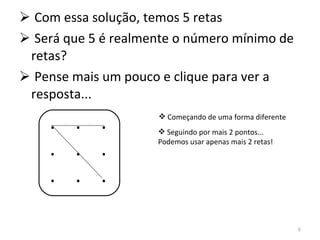

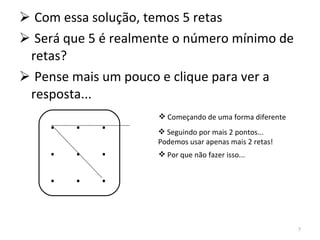

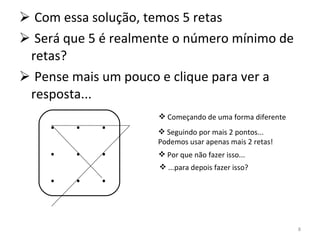

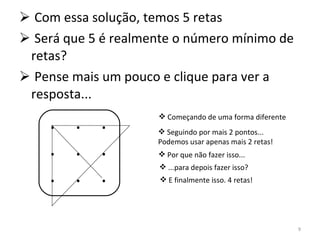

O documento descreve um problema de otimização envolvendo linhas retas que conectam nove pontos. Inicialmente, uma solução com cinco linhas é apresentada, mas é sugerido que pode haver uma solução com menos linhas. Uma solução com quatro linhas é então demonstrada, conectando os pontos de forma diferente da inicial. Em seguida, o texto discute a importância de pensar "fora da caixa" para encontrar soluções não óbvias.

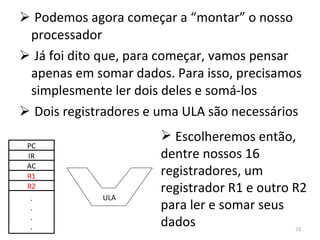

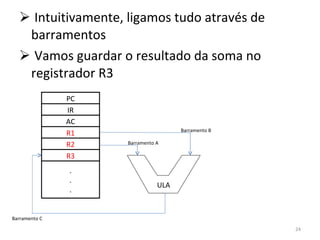

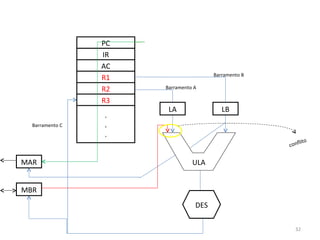

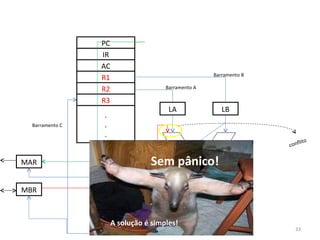

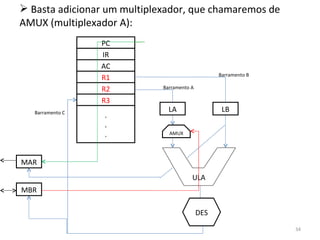

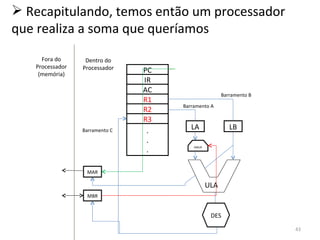

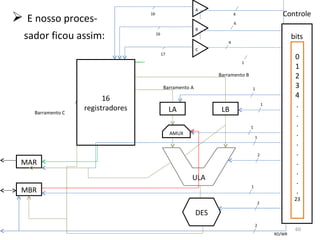

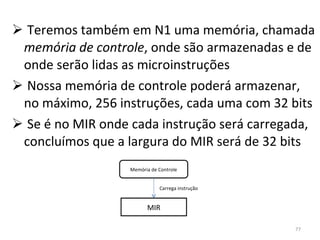

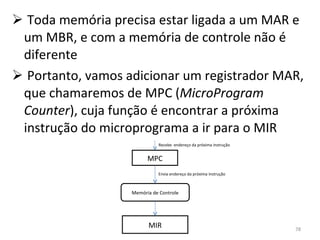

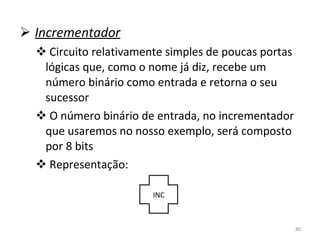

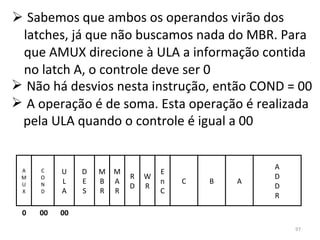

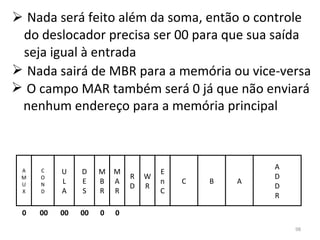

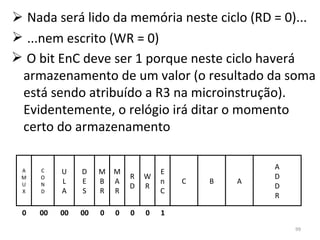

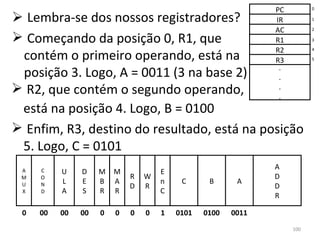

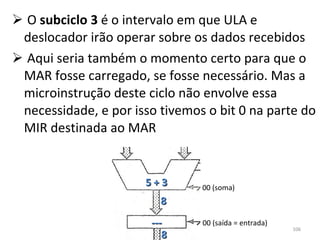

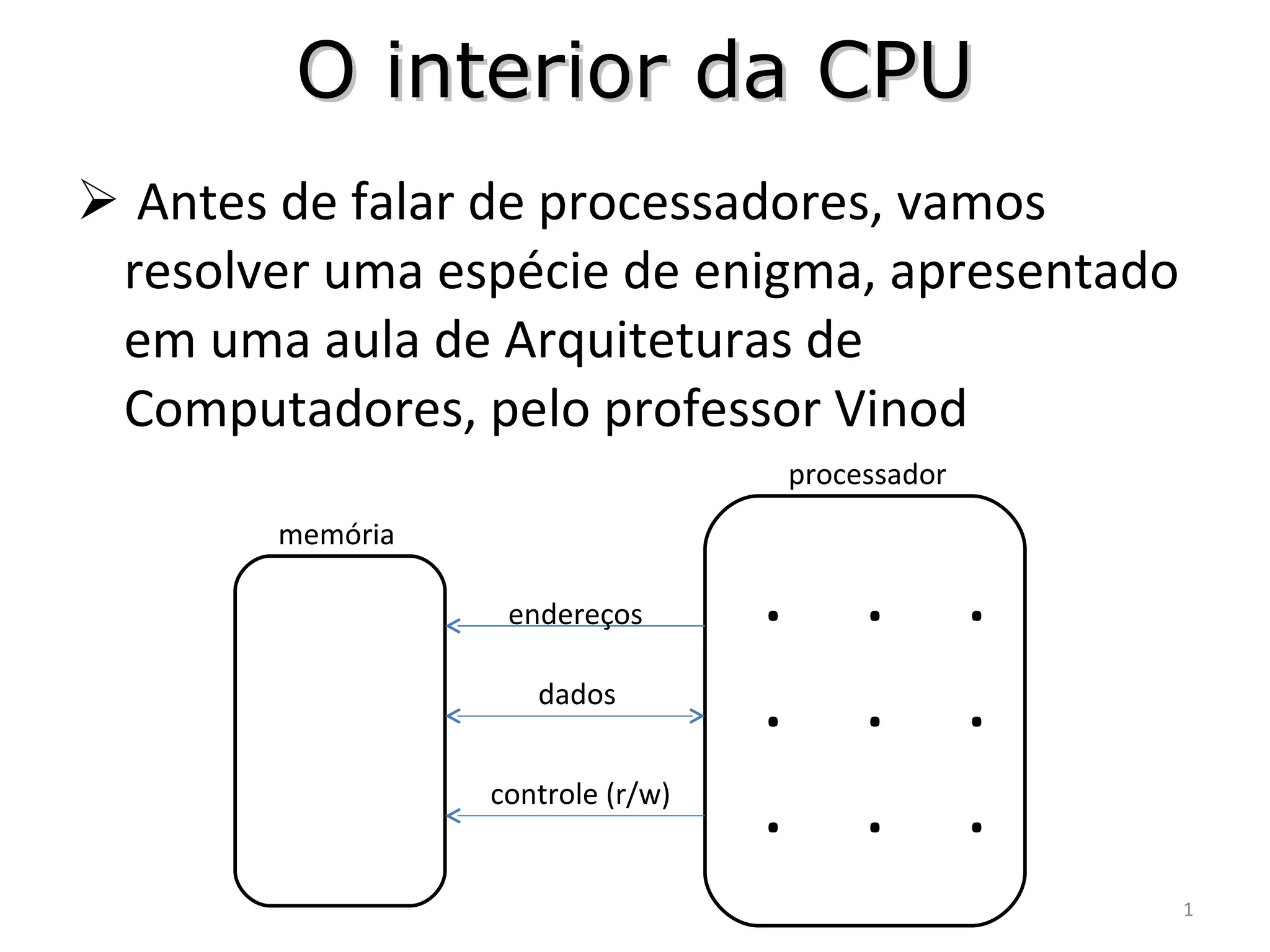

![O Program Counter contém o endereço da próxima instrução a ser buscada na memória principal O Instruction Register armazena a instrução buscada na memória. Ou seja, IR = MP[pc], sendo IR o conteúdo do registrador e pc um endereço da memória principal MP Accumulator é um registrador que armazena valores intermediários, que não seriam úteis ao final da operação Haverá em nossa arquitetura, além dos 16, outros registradores espalhados no processador: dois latches , A e B, o Memory Adress Register (MAR) e o Memory Buffer Register (MBR)](https://image.slidesharecdn.com/microprogramacao-111213052829-phpapp01/85/Microprogramacao-20-320.jpg)