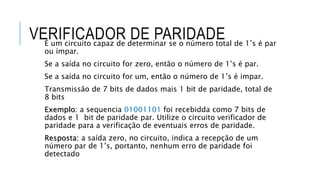

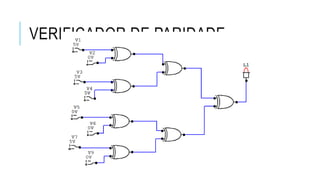

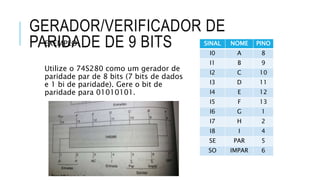

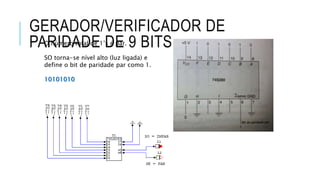

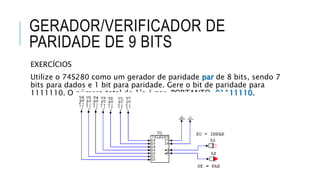

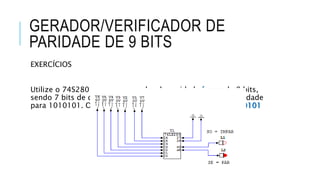

O documento descreve um circuito verificador de paridade capaz de detectar erros em transmissões de dados através da verificação do número total de bits 1. Se a saída for 0, o número de bits 1 é par e não há erro. Se for 1, o número é ímpar e pode haver erro. O circuito integrado 74S280 pode ser usado como gerador ou verificador de paridade para 8 bits de dados e 1 bit de paridade.