O documento discute circuitos lógicos combinacionais, apresentando:

1) Como elaborar tabelas verdade para analisar as saídas de circuitos formados por várias portas lógicas;

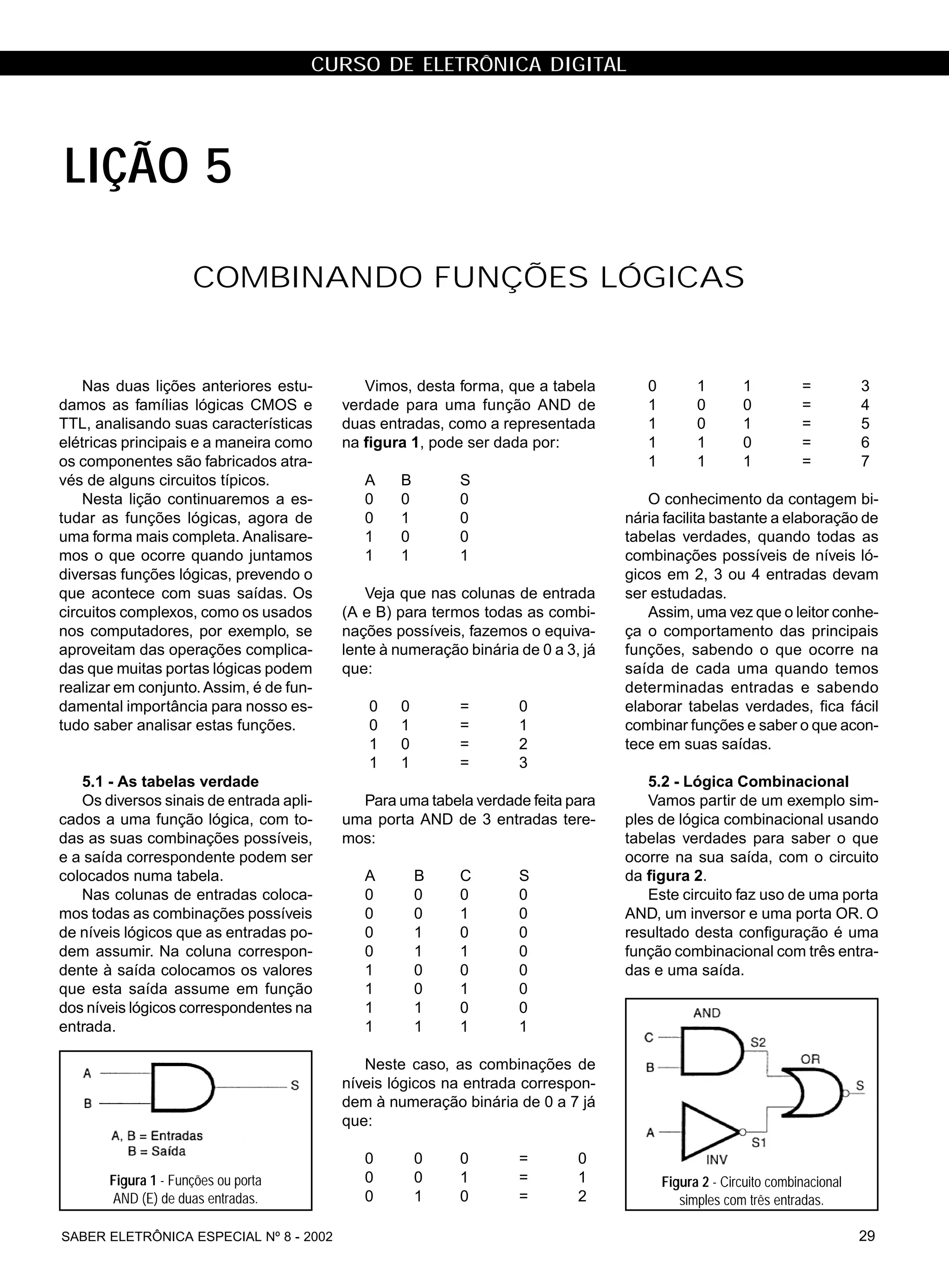

2) Um exemplo de circuito combinacional com três entradas e uma saída;

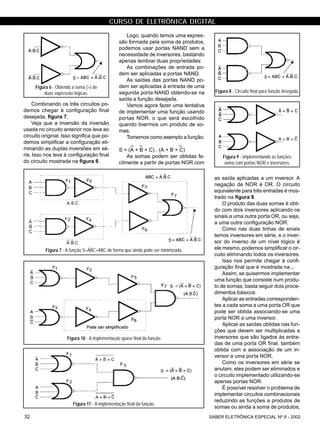

3) Os passos para projetar um circuito combinacional a partir de uma tabela verdade.