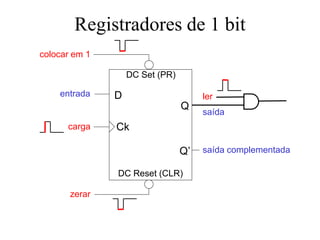

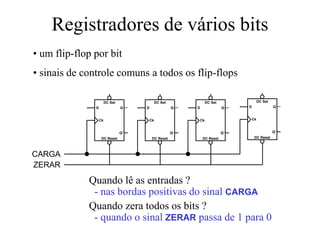

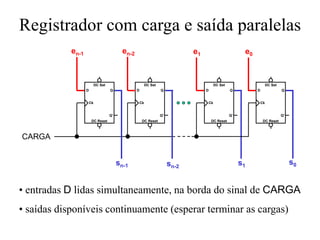

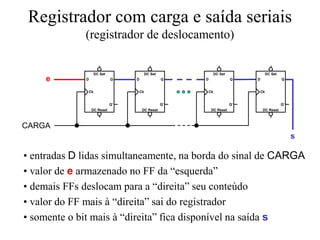

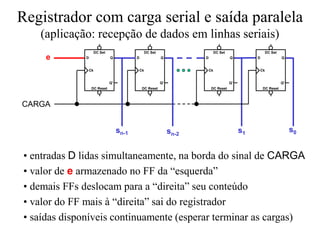

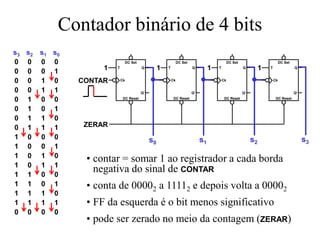

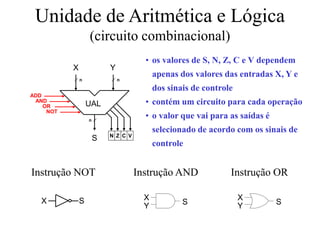

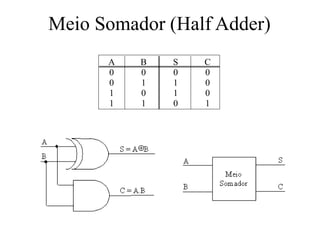

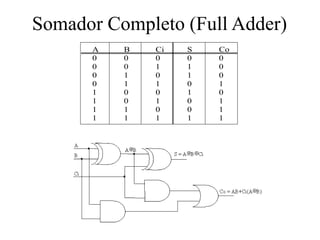

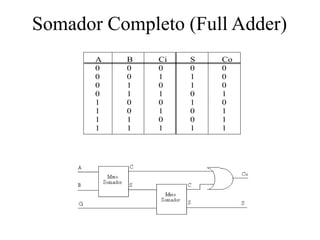

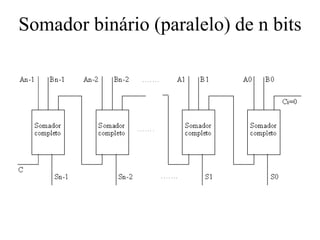

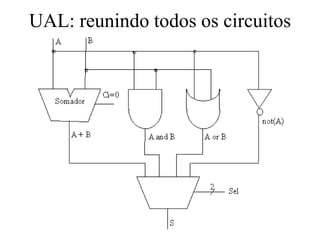

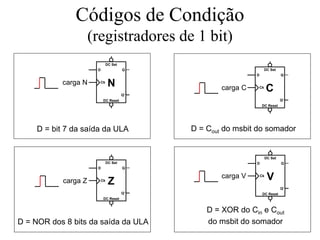

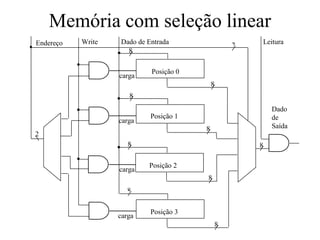

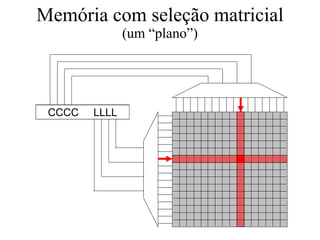

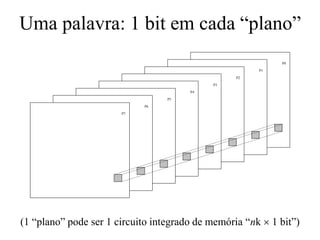

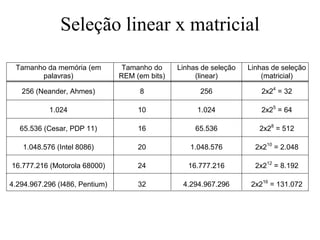

O documento descreve os componentes básicos usados para construir registradores e unidades de processamento digital, incluindo flip-flops, portas lógicas, somadores e memórias. Registradores podem armazenar dados serialmente ou paralelamente e serem usados em contadores ou para armazenar resultados de operações. Unidades aritméticas e lógicas executam operações usando circuitos combinacionais. Memórias armazenam dados usando seleção linear ou matricial.