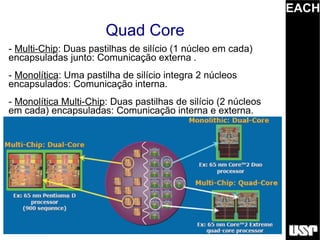

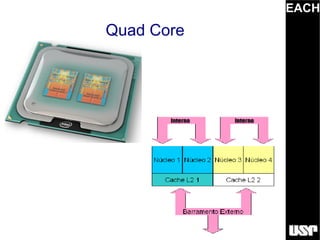

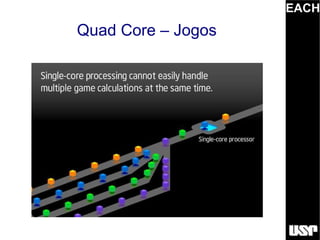

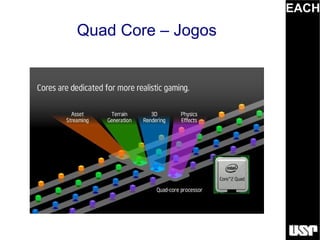

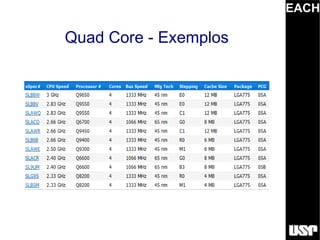

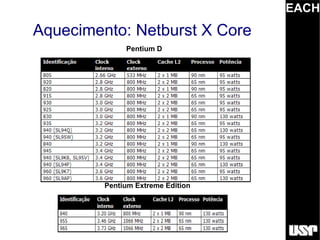

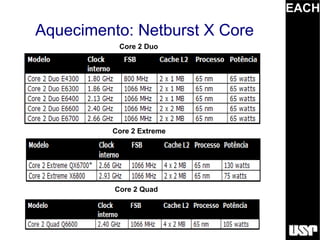

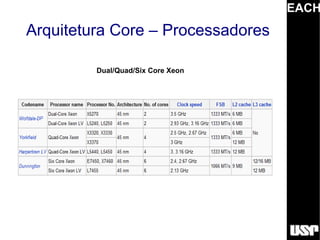

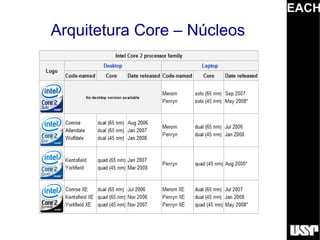

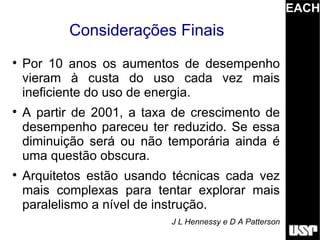

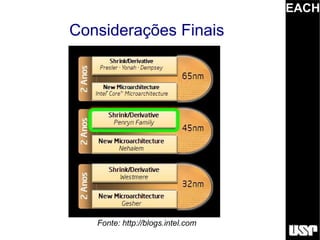

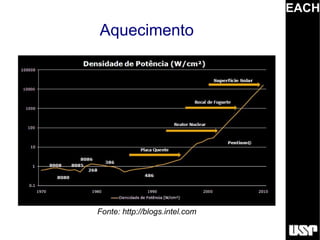

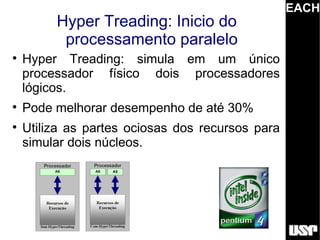

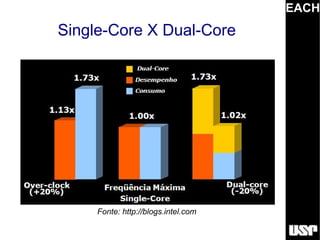

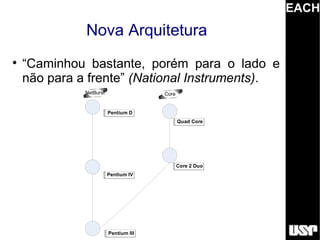

O documento discute a evolução das CPUs de um núcleo único para múltiplos núcleos. A corrida por altas frequências do Pentium IV levou a problemas de aquecimento e consumo excessivo. Isso levou ao desenvolvimento de CPUs com múltiplos núcleos mais eficientes, como o Core 2 Duo e processadores quad core. A arquitetura Core trouxe maior eficiência de execução de instruções por ciclo em comparação com a arquitetura Netburst anterior.

![EACH

Arquitetura Core

Novo conceito: Fusão de instruções

load eax, [mem1]

cmp eax, [mem2]

jne target

load eax, [mem1]

cmp eax, [mem2] + jne target

Graças ao conceito de fusão de instruções o

decodificador de instruções da arquitetura

Core consegue fundir 2 instruçoes enviar 5

por pulso de clock.](https://image.slidesharecdn.com/evoluodascpus-dualequadcore-130131141455-phpapp01/85/Evolucao-das-CPUs-17-320.jpg)