1. Este documento apresenta as referências bibliográficas e sites na internet relacionados ao curso de Eletrônica II ministrado pelo professor Sidney José Montebeller na Faculdade de Engenharia de Sorocaba.

2. O texto está organizado em 16 capítulos que abordam diversos tópicos da eletrônica digital como circuitos combinatórios, famílias lógicas, dispositivos de lógica programável, flip-flops, contadores, registradores e conversão digital-analógica.

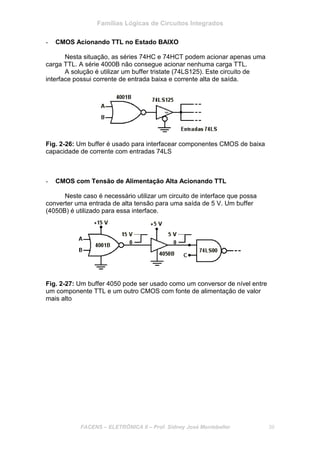

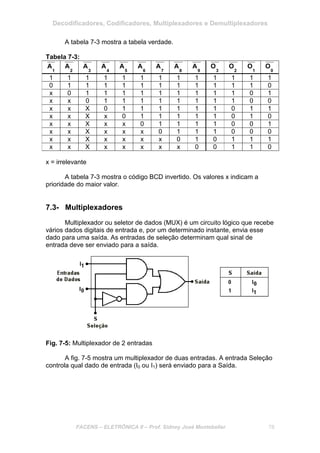

3. As

![Aritmética Digital

FACENS – ELETRÔNICA II – Prof. Sidney José Montebeller 93

Tabela 8-2:

Bit de

entrada da

1ª parcela

Bit de

entrada da

2ª parcela

Bit de

entrada do

carry

Bit de

saída da

soma

Bit de

saída do

carry

A B CIN S COUT

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

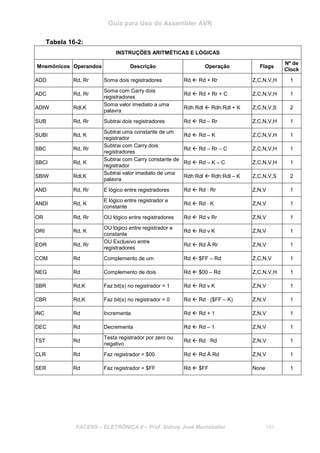

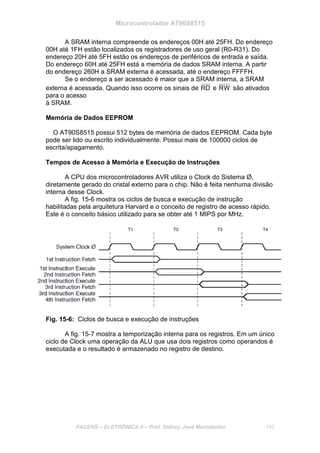

Pelo método do Mapa de Karnaugh podemos encontrar a expressão

para S e COUT:

[ ]CBAC.BA.A.B.CINC.B.A.CB.AS INININ IN ⊕⊕=+++=

A.BB.CA.CC ININOUT ++=

A fig. 8-5 mostra o circuito de um somador completo (SC).

Fig. 8-5: Circuito lógico do somador completo de 1 bit](https://image.slidesharecdn.com/eletronicadigital-140827172456-phpapp01/85/Eletronica-digital-100-320.jpg)

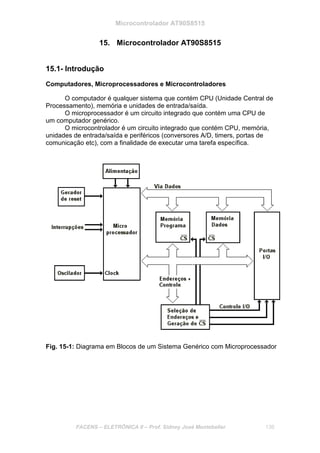

![Microcontrolador AT90S8515

FACENS – ELETRÔNICA II – Prof. Sidney José Montebeller 182

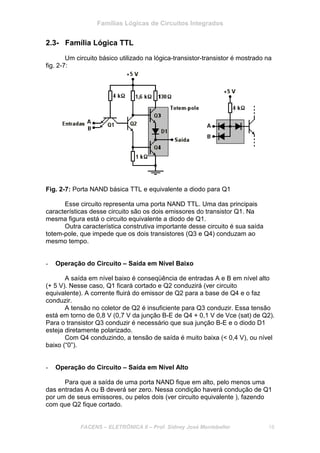

UM quando o pino foi configurado como uma entrada, o resistor de pull-up

MOS é ativado. Para desligar o resistor de pull-up, o PORTBn deve ser zerado

ou o pino deve ser configurado como uma saída. Os pinos do port B estarão

em tri-state quando um reset ocorre, sempre se o clock não está ativo.

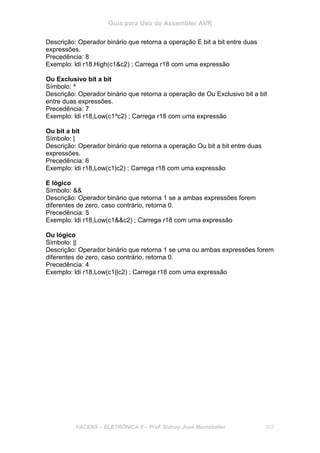

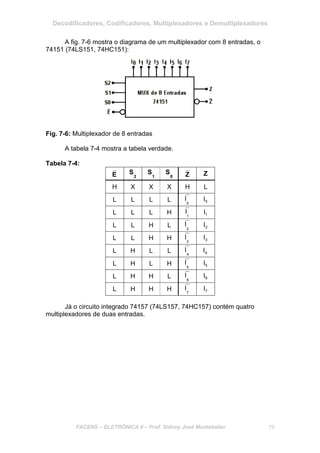

A tabela 15-15 mostra a configuração de DDBn e PORTBn.

Tabela 15-15:

Outras Funções do Port B

As funções alternativas dos pinos do port B são as seguintes:

• SCK – Port B, Bit 7 –

SCK: pino de saída de clock no modo master, pino de entrada de clock no

modo slave da SPI. Quando a SPI é habilitada como slave, esse pino é

configurado como uma entrada, anulando as definições de DDB7. Quando a

SPI é habilitada como master, a direção dos dados desse pino é controlada

por DDB7. Quando o pino é forçado a ser uma entrada, o resistor de pull-up

é controlado pelo bit PORTB7.

• MISO – Port B, Bit 6 –

MISO: pino de entrada de dados no modo master, pino de saída de dados

no modo slave da SPI. Quando a SPI é habilitada como master, esse pino é

configurado como entrada, anulando as definições de DDB6. Quando a SPI

é habilitada como slave, a direção dos dados desse pino é controlada por

DDB6. Quando o pino é forçado a ser uma entrada, o resistor de pull-up é

controlado pelo bit PORTB6.

• MOSI – Port B, Bit 5 –]

MOSI: pino de saída de dados no modo master, pino de entrada de dados

no modo slave da SPI. Quando a SPI é habilitada como slave, esse pino é

configurado como uma entrada, anulando as definições de DDB5. Quando a

SPI é habilitada com o master, a direção dos dados desse pino é controlada

por DDB5. Quando o pino é forçado a ser uma entrada, o resistor de pull-up

é controlado pelo bit PORTB5.

• SS – Port B, Bit 4 –

SS : pino de entrada de seleção do slave. Quando a SPI é habilitada como

slave, esse pino é configurado como uma entrada, anulando as definições

de DDB4. Como slave, a SPI é habilitada quando esse pino é colocado em

BAIXO. Quando a SPI for habilitada como master, a direção dos dados](https://image.slidesharecdn.com/eletronicadigital-140827172456-phpapp01/85/Eletronica-digital-189-320.jpg)

![Guia para Uso do Assembler AVR

FACENS – ELETRÔNICA II – Prof. Sidney José Montebeller 188

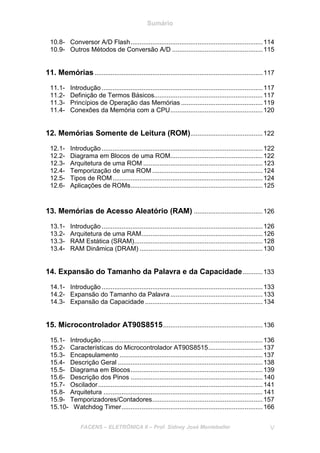

16. Guia para Uso do Assembler AVR

16.1- Introdução

O Assembler AVR converte um código fonte feito em assembly para um

código objeto que será utilizado em microcontroladores da família AT90S

Atmel. Esse código objeto gerado pode ser usado em um simulador ou

emulador (In-Circuit Emulator). O Assembler também gera um código objeto de

programação da memória de programa (FLASH) dos microcontroladores AVR.

16.2- Código Fonte do Assembler

O Assembler utiliza arquivos fonte que contém mnemônicos de

instruções, labels e diretivas. Os mnemônicos de instruções e as diretivas

necessitam de operados.

Cada linha de código é limitada em 120 caracteres. Cada linha pode ter

um label, que é uma seqûência de letras ou números terminada com “:”. Esses

labels são usados como “alvos” para instruções de pulo ou desvio ou como

nome de variáveis na memória de Programa ou na RAM.

Uma linha do código fonte pode ter as seguintes formas:

1. [label:] diretiva [operandos] [Comentários]

2. [label:] instruções [operandos] [Comentários]

3. Comentários

4. Linha em branco

Um comentário é feito da seguinte maneira:

; [texto]

Os itens colocados em colchetes [] são opcionais. O texto colocado entre

o delimitador de comentários (;) e o caracter fim de linha (EOL) é ignorado pelo

Assembler.

Exemplos:

label: .EQU var1=100 ; Faz var1 igual 100 (Diretiva)

.EQU var2=200 ; Faz var2 igual 200

test: rjmp test ; Loop Infinito (Instrução)

; Linha comentada

; Outra linha comentada](https://image.slidesharecdn.com/eletronicadigital-140827172456-phpapp01/85/Eletronica-digital-195-320.jpg)