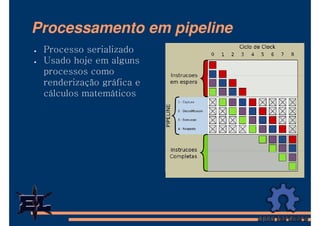

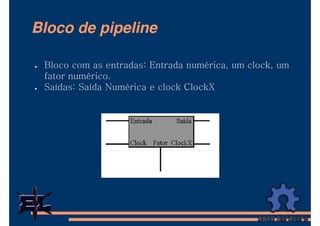

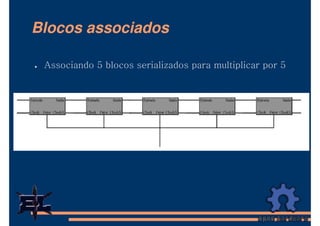

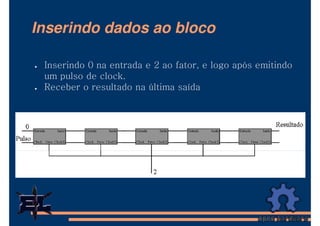

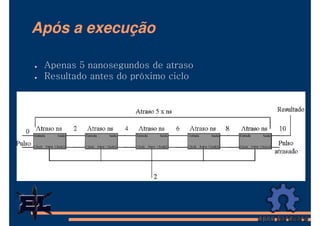

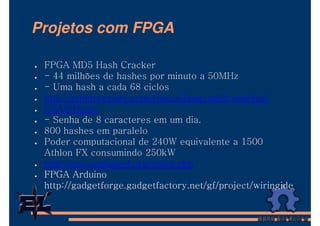

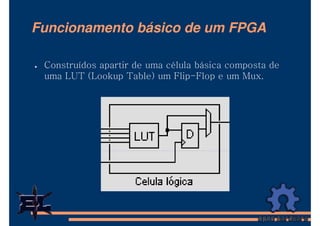

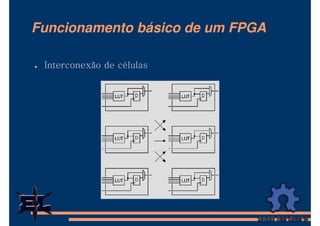

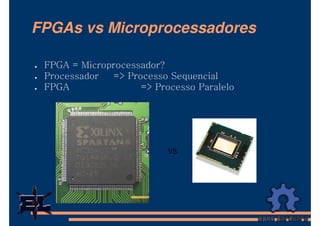

O documento apresenta um resumo sobre lógica programável com FPGA. Ele discute brevemente a questão ambiental do lixo eletrônico, a história da lógica programável desde os anos 1970, e como FPGAs funcionam em comparação a microprocessadores. O documento também mostra exemplos de projetos com FPGA e como processamento em pipeline pode ser implementado.

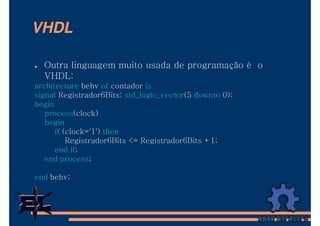

![Verilog

Semelhante ao pascal

reg [5:0] Registrador6bits = 0;

always @(posedge clock)

begin

Registrador6bits <= Registrador6bits + 1;

end](https://image.slidesharecdn.com/opencores-120207140405-phpapp01/85/Open-Cores-Projeto-Open-Hardware-com-FPGA-13-320.jpg)