1) Circuitos aritméticos realizam operações como soma, subtração, multiplicação e divisão usando portas lógicas e flip-flops na unidade lógica e aritmética.

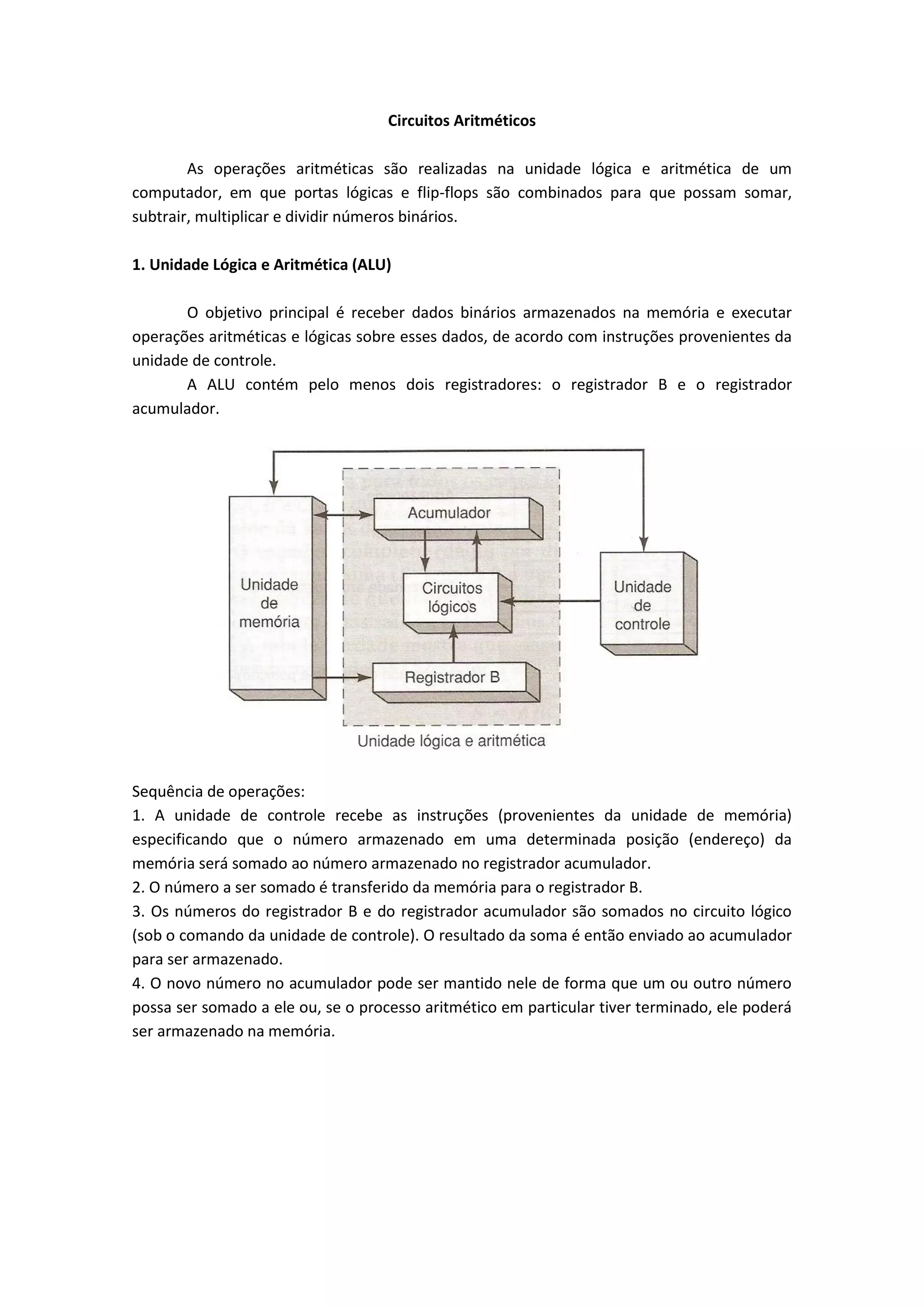

2) A ALU contém registradores B e acumulador para armazenar números binários durante operações.

3) Somadores paralelos em circuitos integrados como o 74HC283 implementam soma binária adicionando bits menos significativos e propagando carry.