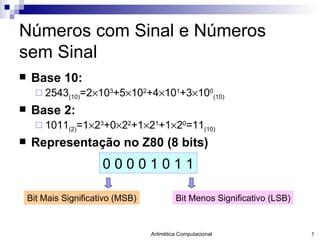

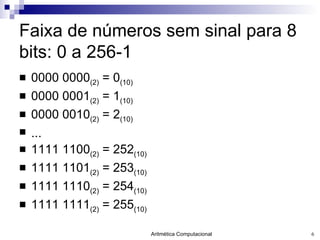

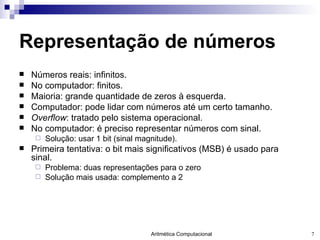

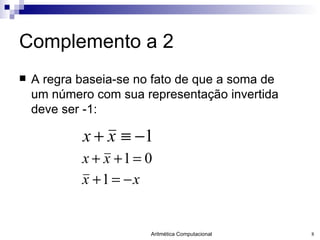

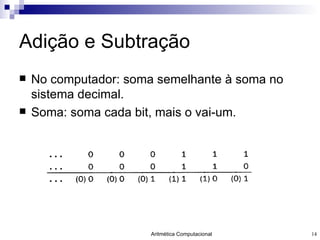

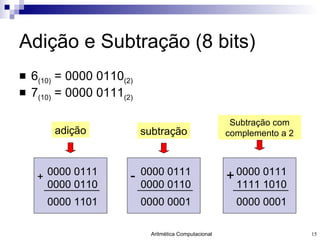

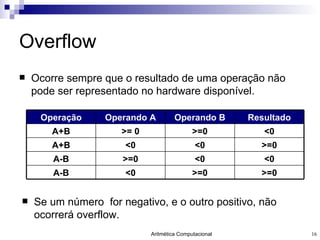

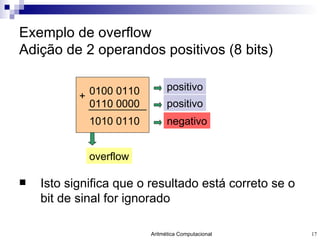

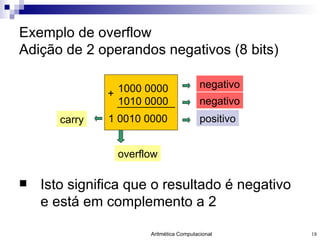

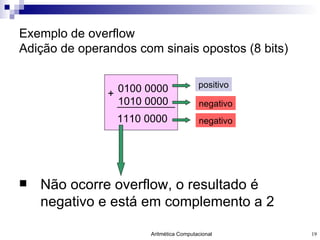

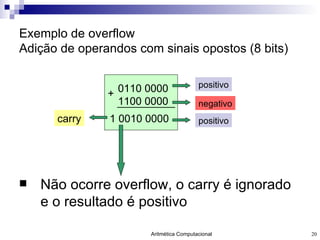

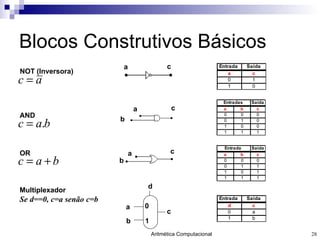

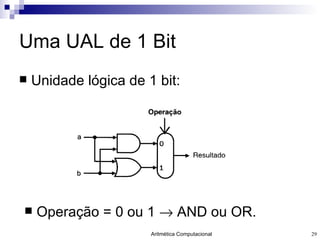

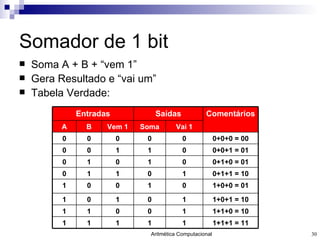

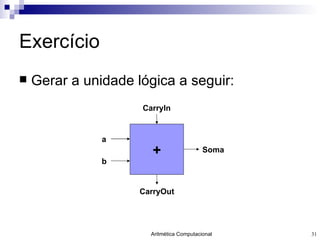

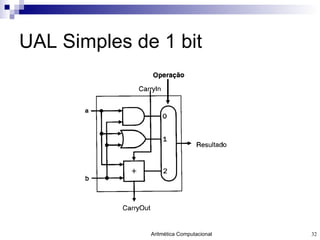

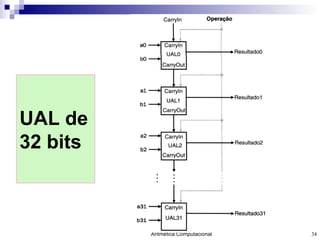

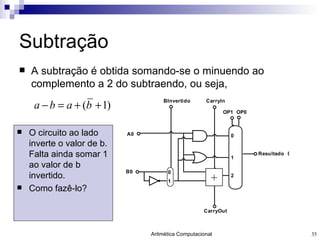

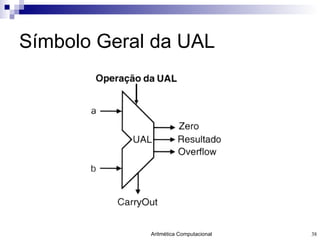

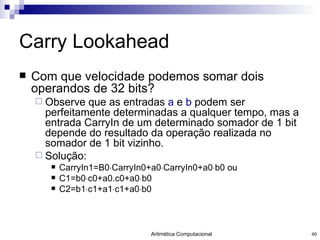

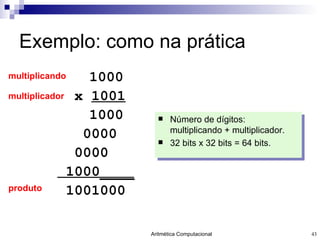

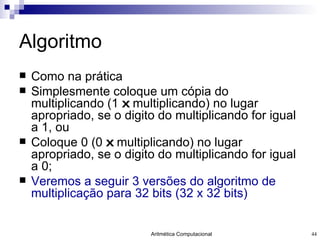

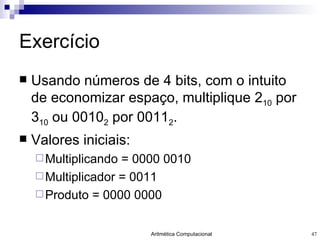

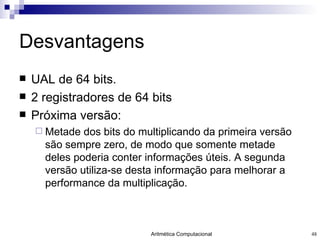

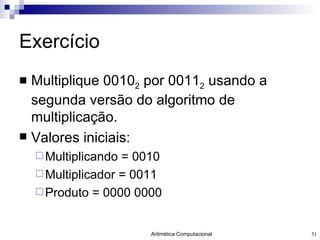

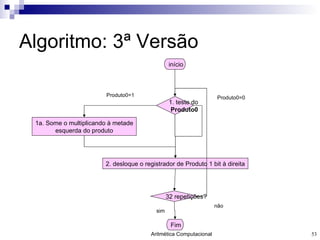

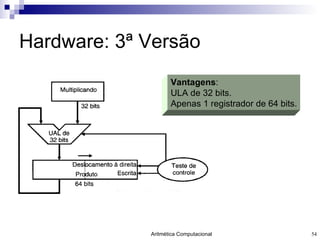

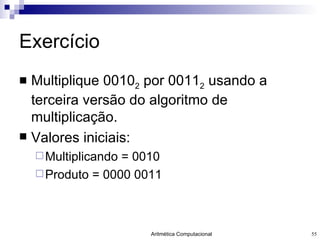

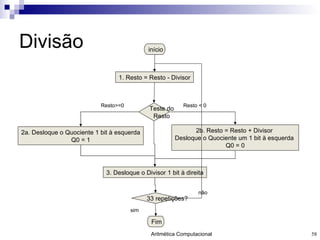

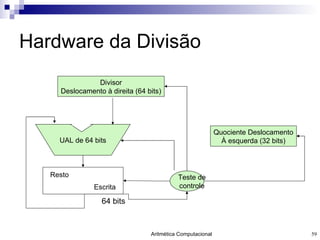

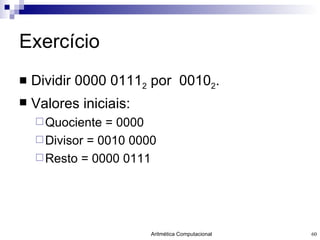

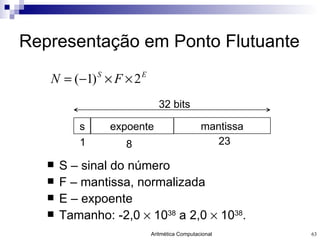

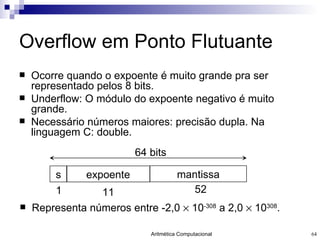

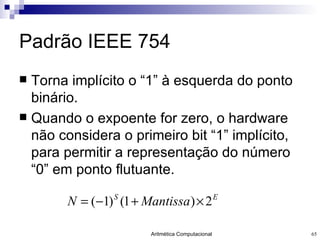

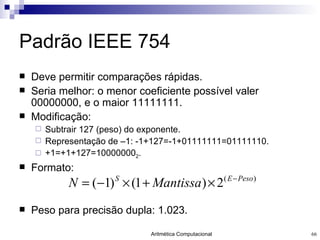

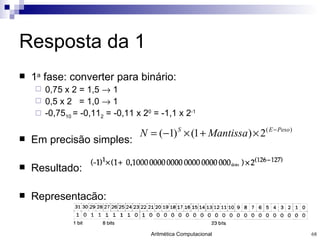

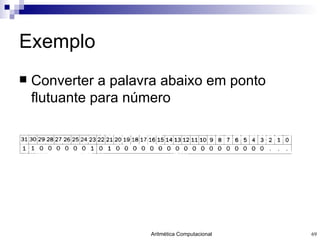

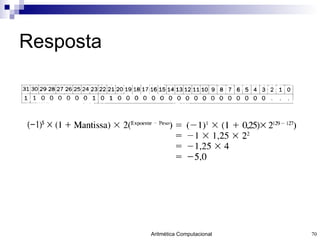

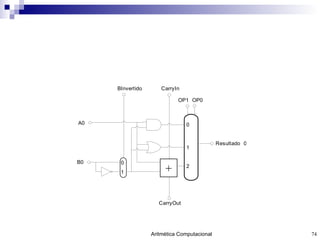

O documento discute a representação de números e operações aritméticas em sistemas binários, incluindo números inteiros e reais, com e sem sinal, adição, subtração, multiplicação e divisão. Aborda também operações lógicas, construção de unidades aritméticas lógicas e tratamento de overflow.