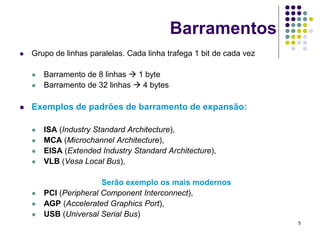

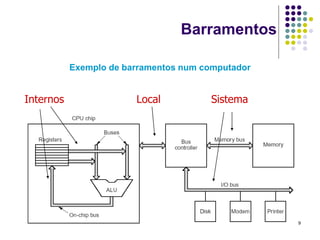

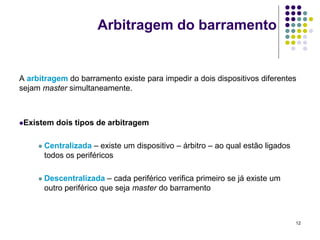

O documento discute a CPU, barramentos e clock interno de um computador. Descreve as definições e constituição interna da CPU e como se liga aos outros componentes através de barramentos. Explica os diferentes tipos de barramentos e como funcionam para transmitir dados entre dispositivos.