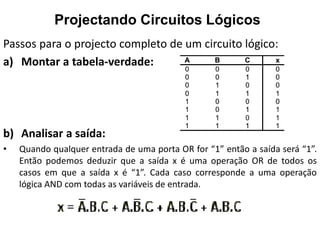

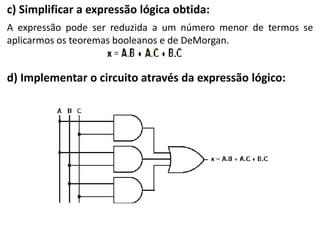

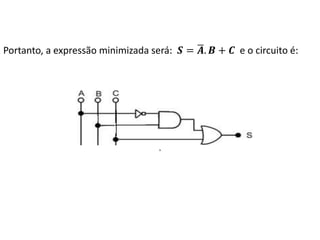

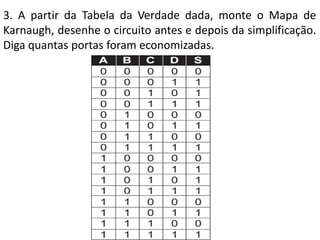

1) O documento descreve os passos para projetar circuitos lógicos, incluindo montar a tabela-verdade, analisar a saída, simplificar a expressão lógica e implementar o circuito.

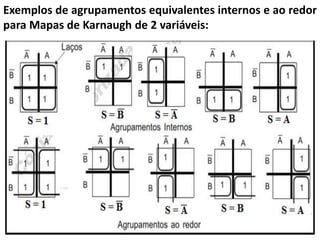

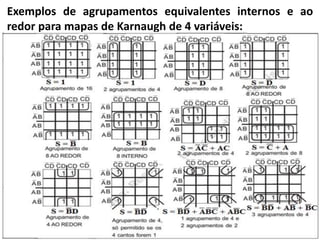

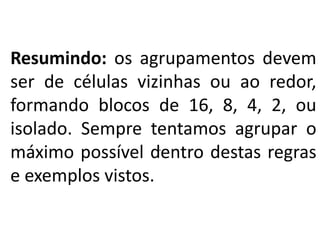

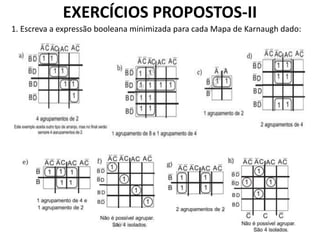

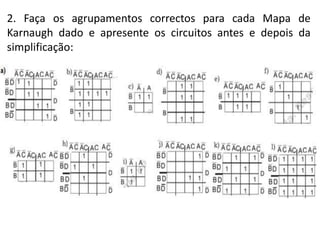

2) É explicado como os diagramas de Veitch-Karnaugh permitem simplificar expressões lógicas com agrupamentos de potências de 2 células vizinhas. Exemplos ilustram agrupamentos válidos.

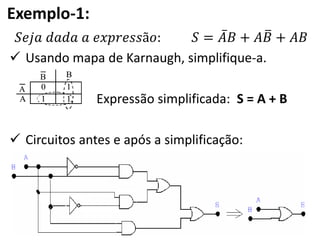

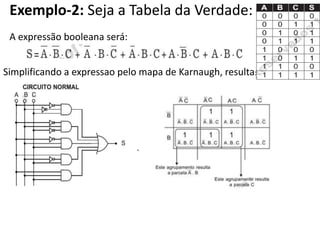

3) Dois exemplos mostram como simplificar expressões lógicas usando mapas de Karnaugh e comparar circuit