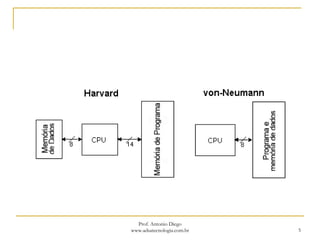

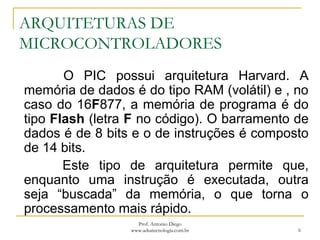

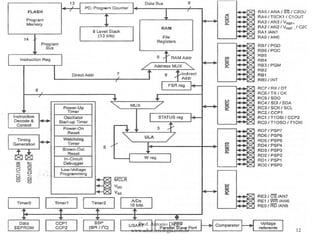

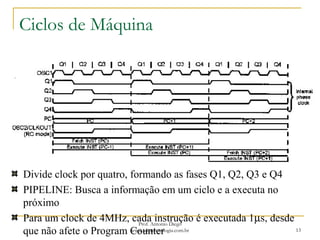

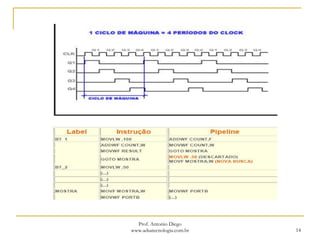

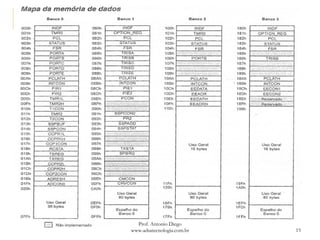

O documento descreve as arquiteturas de microcontroladores. O PIC possui a arquitetura Harvard, com memórias de dados e programa separadas por barramentos distintos de 8 e 14 bits. Isso permite que instruções sejam buscadas enquanto outra é executada, tornando o processamento mais rápido.