Cortex M0+ PIPELINE for data processing and branch instructions - ptbr

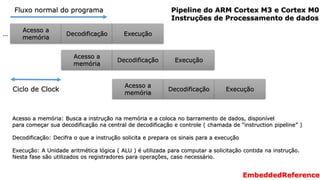

- 1. Acesso a memória Decodificação Execução Fluxo normal do programa … Acesso a memória Decodificação Execução Acesso a memória Decodificação ExecuçãoCiclo de Clock Pipeline do ARM Cortex M3 e Cortex M0 Instruções de Processamento de dados Acesso a memória: Busca a instrução na memória e a coloca no barramento de dados, disponível para começar sua decodificação na central de decodificação e controle ( chamada de “instruction pipeline” ) Decodificação: Decifra o que a instrução solicita e prepara os sinais para a execução Execução: A Unidade aritmética lógica ( ALU ) é utilizada para computar a solicitação contida na instrução. Nesta fase são utilizados os registradores para operações, caso necessário. EmbeddedReference

- 2. Fluxo normal do programa … Ciclo de Clock Acesso a Deco memória dificação Execução Acesso a Deco memória dificação Execução Acesso a Deco memória dificação Execução Pipeline do ARM Cortex M0+ Instruções de Processamento de dados Acesso a memória e começo da decodificação: Busca a instrução na memória, a coloca no barramento de dados, começa sua decodificação na central de decodificação e controle ( chamada de “instruction pipeline” ). Fim da Decodificação e Execução: Prepara os sinais para a execução, acessa os registradores e utiliza a Unidade aritmética lógica ( ALU ) para computar a solicitação contida na instrução. EmbeddedReference

- 3. Minemônico Operandos Descrição Flags que são afetadas ADCS {Rd,} Rn, Rm Add with Carry N,Z,C,V ADD{S} {Rd,} Rn,<Rm|#imm> Add N,Z,C,V ANDS {Rd,} Rn, Rm Bitwise AND N,Z ASRS {Rd,} Rm,<Rs|#imm> Arithmetic Shift Right N,Z,C BICS {Rd,} Rn, Rm Bit Clear N,Z CMN Rn, Rm Compare Negative N,Z,C,V CMP Rn, <Rm|#imm> Compare N,Z,C,V EORS {Rd,} Rn, Rm Exclusive OR N,Z LSLS {Rd,} Rn,<Rs|#imm> Logical Shift Left N,Z,C LSRS {Rd,} Rn,<Rs|#imm> Logical Shift Right N,Z,C MOV{S} Rd, Rm Move N,Z MULS Rd, Rn, Rm Multiply, 32-bit result N,Z MVNS Rd, Rm Bitwise NOT N,Z ORRS {Rd,} Rn, Rm Logical OR N,Z ARM Cortex M0+: Instruções de Processamento de dados EmbeddedReference

- 4. Minemônico Operandos Descrição Flags que são afetadas REV Rd, Rm Byte-Reverse word - REV16 Rd, Rm Byte-Reverse packed halfwords - REVSH Rd, Rm Byte-Reverse signed halfword - RORS {Rd,} Rn, Rs Rotate Right N,Z,C RSBS {Rd,} Rn, #0 Reverse Subtract N,Z,C,V SBCS {Rd,} Rn, Rm Subtract with Carry N,Z,C,V SUB{S} {Rd,} Rn,<Rm|#imm> Subtract N,Z,C,V SXTB Rd, Rm Sign extend byte - SXTH Rd, Rm Sign extend halfword - TST Rn, Rm Logical AND based test N,Z UXTB Rd, Rm Zero extend a byte - UXTH Rd, Rm Zero extend a halfword - ARM Cortex M0+: Instruções de Processamento de dados EmbeddedReference

- 5. Acesso a memória Fluxo normal do programa Ciclo de Clock Pipeline do ARM Cortex M3 e Cortex M0 Instruções de Branch (saltos condicionais) Decodificação Execução Acesso a memória Decodificação Cálculo do Endereço de Branch Acesso a memória Acesso a memória Acesso a memória Decodificação Execução Acesso a memória Decodificação Execução Instruções descartadas I1 Resultado do cálculo: Instrução I1 Em amarelo, instrução de Branch Em vermelho, instruções que serão descartadas EmbeddedReference

- 6. Fluxo normal do programa Ciclo de Clock Instrução descartada I1 Resultado do cáculo: Instrução I1 Pipeline do ARM Cortex M0+ Instruções de Branch (saltos condicionais) … Acesso a Deco memória dificação Execução Acesso a Deco memória Cálculo dificação do end. de branch Acesso a Deco memória Acesso a Deco memória dificação Execução Acesso a Deco memória dificação Execução Em amarelo, instrução de Branch Em vermelho, instrução que será descartada EmbeddedReference

- 7. Fluxo normal do programa Loop1: Decisão Cada Instrução é executada em um ciclo de clock nesse exemplo 1 ciclo de espera … Ciclo de Clock ARM Cortex M3 e M0: Tempo ocioso devido a um branch ADD CMP BLE Loop1 ADD EmbeddedReference

- 8. Fluxo normal do programa Loop1: Decisão Cada Instrução é executada em um ciclo de clock nesse exemplo 1 ciclo de espera … Ciclo de Clock ARM Cortex M0+: Tempo ocioso devido a um branch ADD CMP BLE Loop1 ADD EmbeddedReference

- 9. Minemônico Descrição B{cc} Branch {conditionally} BL Branch with Link BLX Branch indirect with Link BX Branch indirect ARM Cortex M0+: Instruções de Branch EmbeddedReference

- 10. ARM Cortex M0+: Instruções de Branch EmbeddedReference Minemônico Descrição B{cc} Branch {conditionally} BL Branch with Link BLX Branch indirect with Link BX Branch indirect