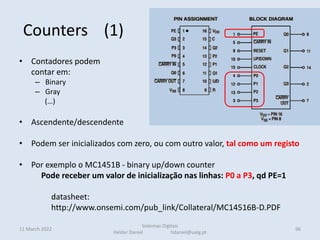

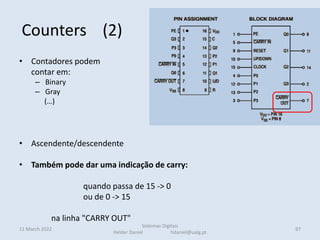

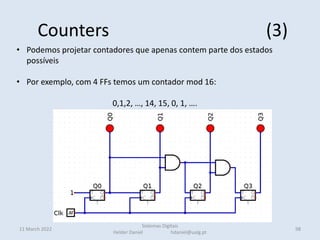

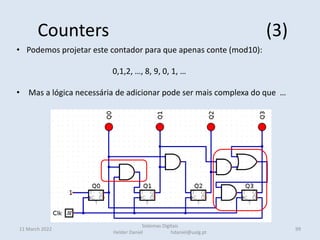

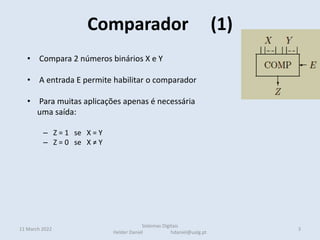

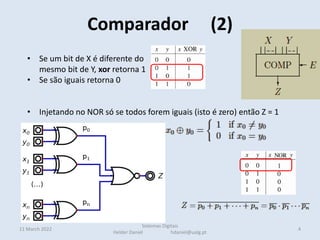

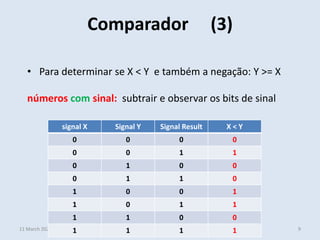

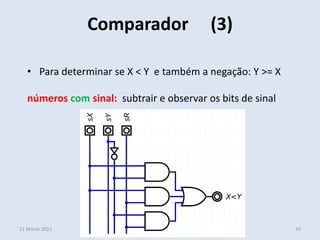

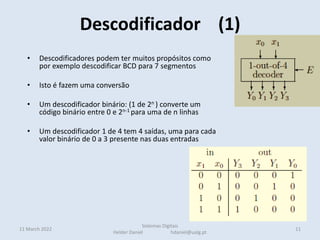

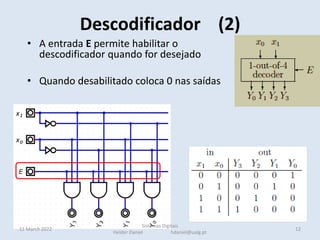

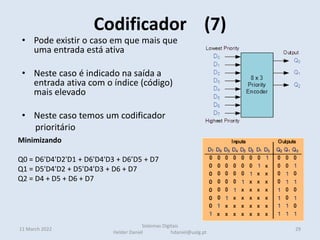

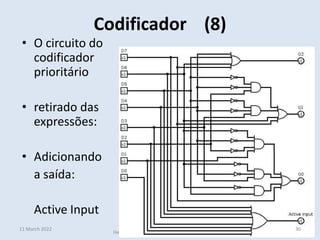

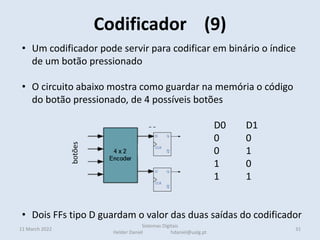

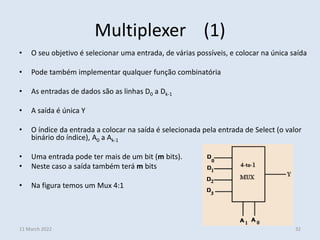

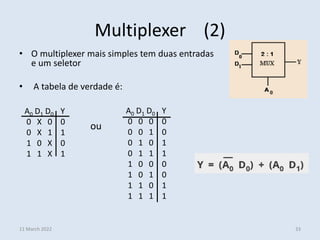

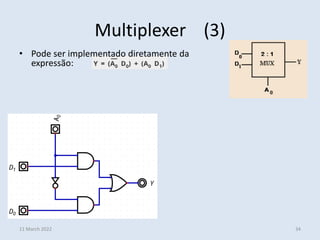

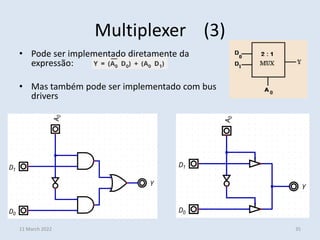

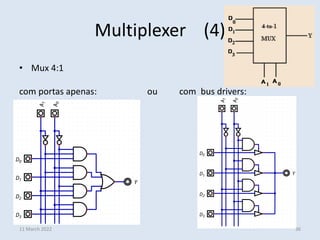

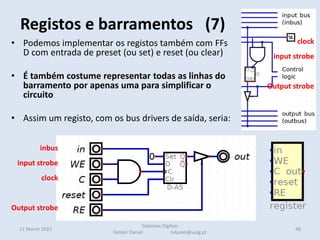

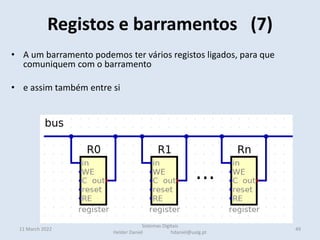

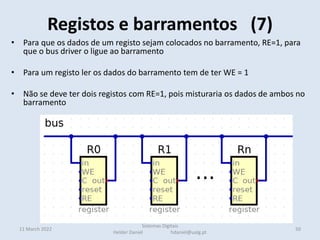

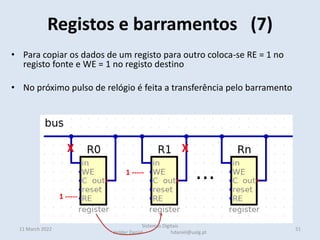

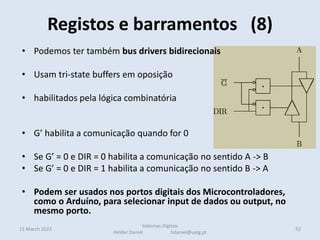

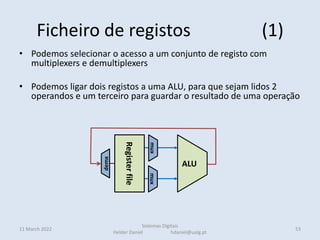

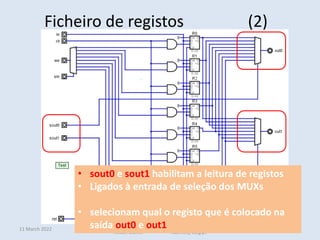

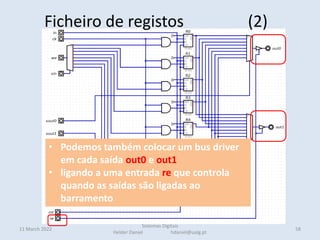

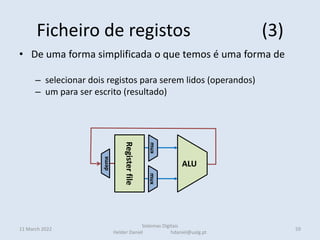

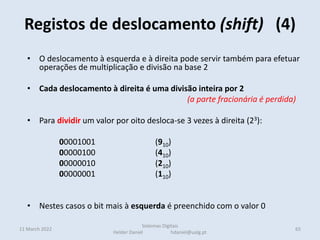

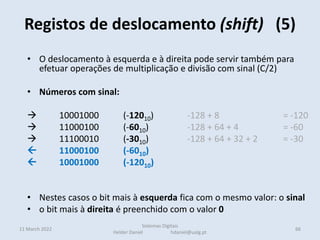

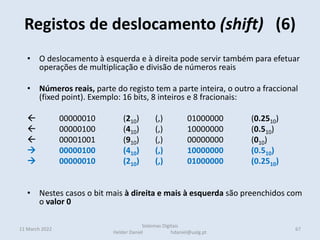

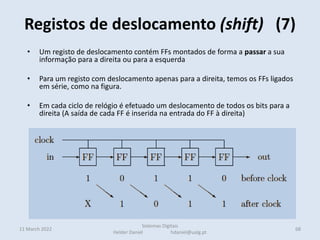

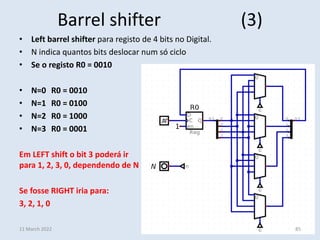

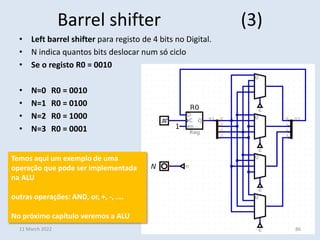

O documento discute elementos funcionais em sistemas digitais, incluindo comparadores, descodificadores, codificadores, multiplexers, demultiplexers, contadores, registros e barramentos. Ele apresenta conceitos fundamentais como operações de comparação de números binários e a estrutura de circuitos lógicos usados para decodificar e codificar informações. Além disso, aborda a implementação de registros e barramentos utilizando flip-flops e a lógica de controle necessária para o armazenamento e transferência de dados.

![Logarithmic shifters

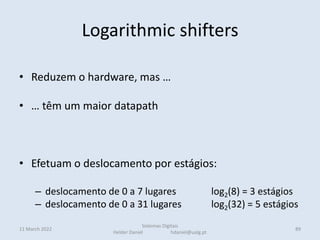

• baseados em Muxs

• Este exemplo permite deslocamento [0, 7], entradas: S0, S1 e S2

• 3 estágios

.

11 March 2022

Sistemas Digitais

Helder Daniel hdaniel@ualg.pt

90

S2

S1

S0

D7 D6 D5 D4 D3 D2 D1 D0

Z7 Z6 Z5 Z4 Z3 Z2 Z1 Z0

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

(7,1) (6,1) (5,1) (4,1) (3,1) (2,1) (1,1) (0,1)

(7,2) (6,2) (5,2) (4,2) (3,2) (2,2) (1,2) (0,2)

(7,3) (6,3) (5,3) (4,3) (3,3) (2,3) (1,3) (0,3)

(7,0) (6,0) (5,0) (4,0) (3,0) (2,0) (1,0) (0,0)](https://image.slidesharecdn.com/07-elementosfuncionais-250111010947-d0ec8bf2/85/07-Elementos-funcionais-pdf-Kkkkkkkk-90-320.jpg)

![Logarithmic shifters

• baseados em DeMux

• Este exemplo permite deslocamento [0, 7], entradas: S0, S1 e S2

• 3 estágios

.

11 March 2022

Sistemas Digitais

Helder Daniel hdaniel@ualg.pt

91

Z7 Z6 Z5 Z4 Z3 Z2 Z1 Z0

D7 D6 D5 D4 D3 D2 D1 D0

S2

S1

S0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

(7,1) (6,1) (5,1) (4,1) (3,1) (2,1) (1,1) (0,1)

(7,2) (6,2) (5,2) (4,2) (3,2) (2,2) (1,2) (0,2)

(7,3) (6,3) (5,3) (4,3) (3,3) (2,3) (1,3) (0,3)

(7,0) (6,0) (5,0) (4,0) (3,0) (2,0) (1,0) (0,0)](https://image.slidesharecdn.com/07-elementosfuncionais-250111010947-d0ec8bf2/85/07-Elementos-funcionais-pdf-Kkkkkkkk-91-320.jpg)