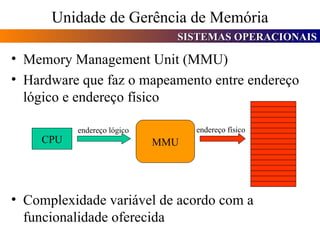

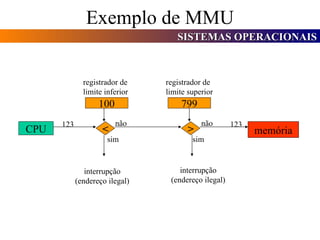

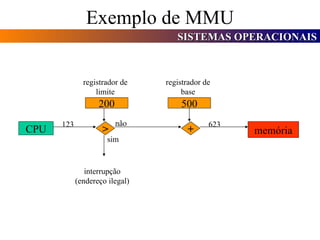

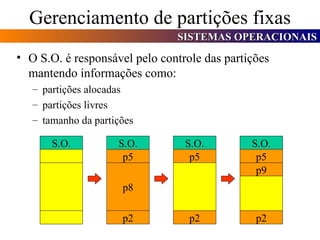

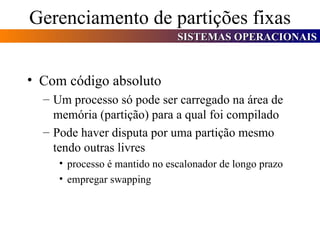

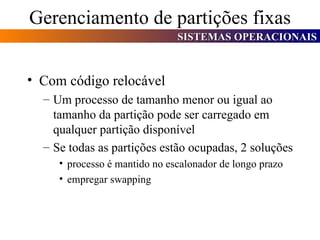

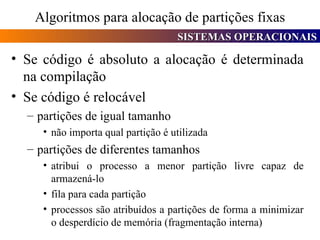

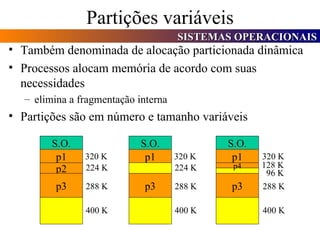

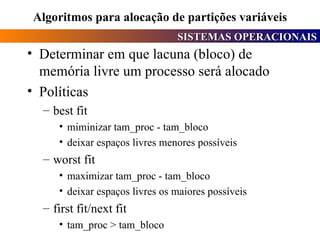

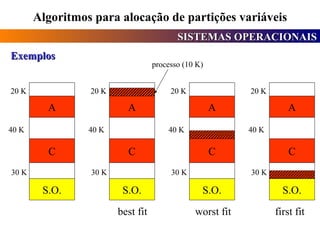

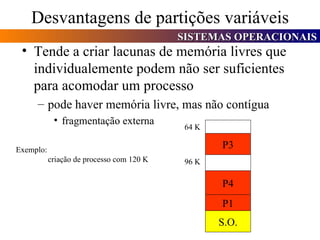

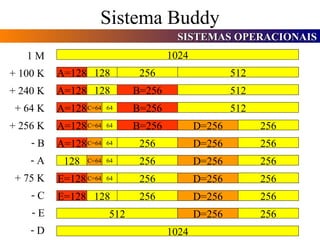

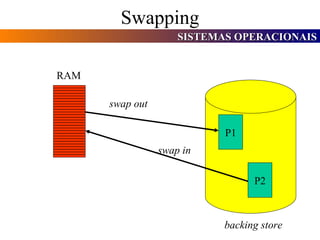

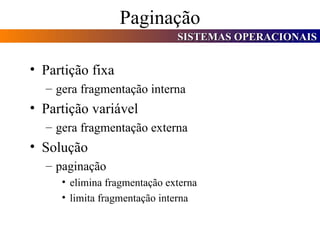

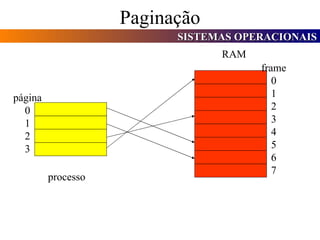

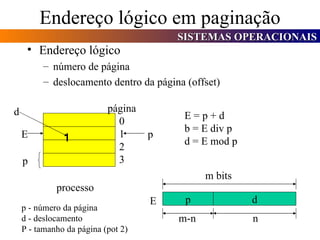

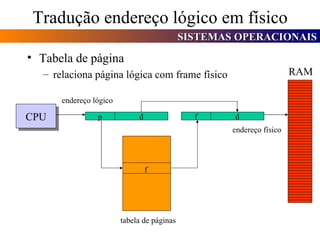

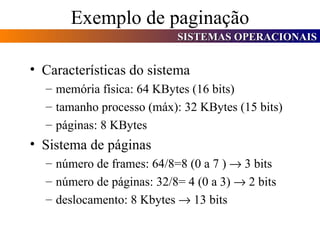

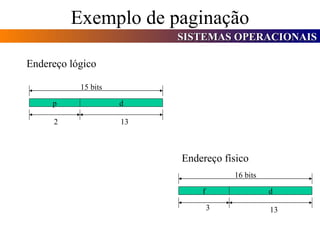

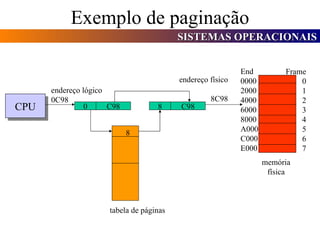

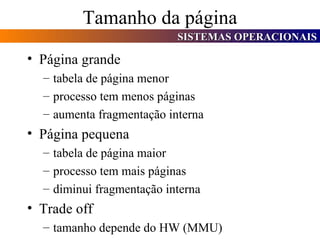

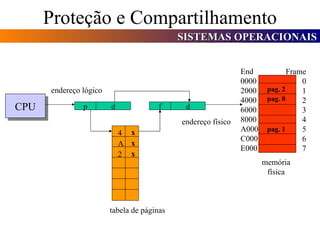

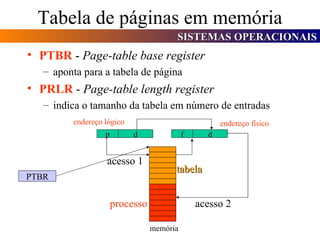

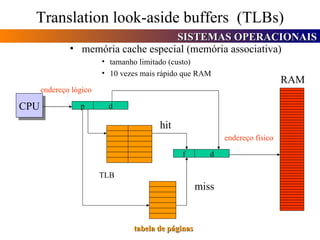

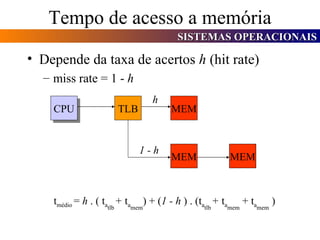

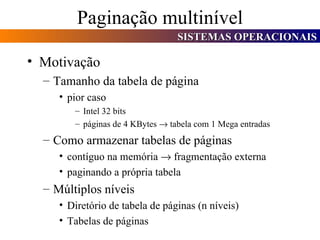

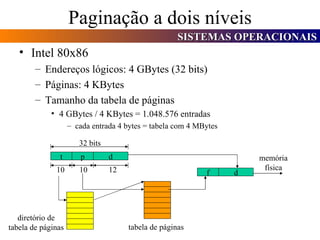

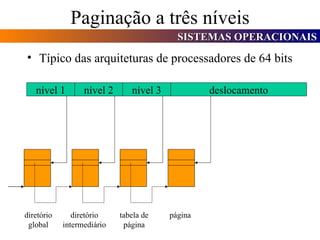

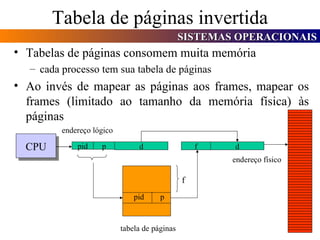

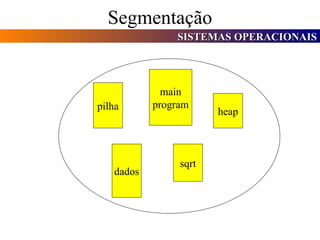

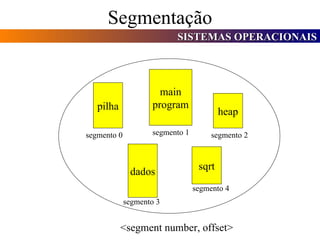

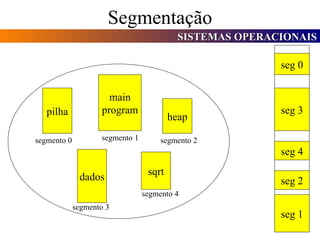

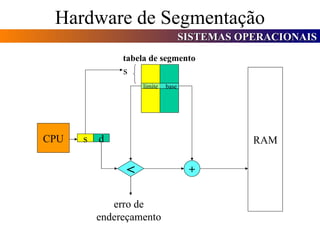

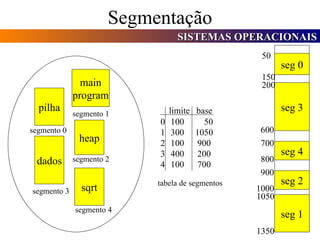

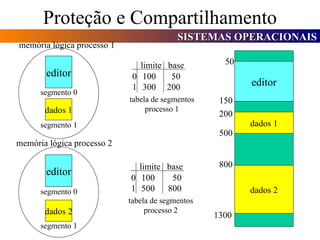

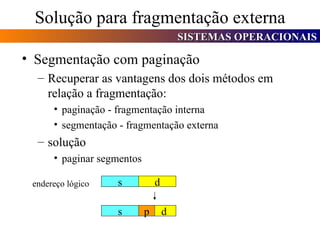

Gerenciamento de memória envolve dividir a memória física entre processos de forma eficiente através de técnicas como partições fixas e variáveis, paginação e segmentação. A unidade de gerenciamento de memória mapeia endereços lógicos para físicos usando tabelas de páginas. Isso permite proteção e compartilhamento de memória entre processos.