1) Este documento é uma apostila sobre eletrônica digital dividida em três unidades, apresentando conceitos básicos de sistemas digitais como portas lógicas, flip-flops, registradores de deslocamento e contadores.

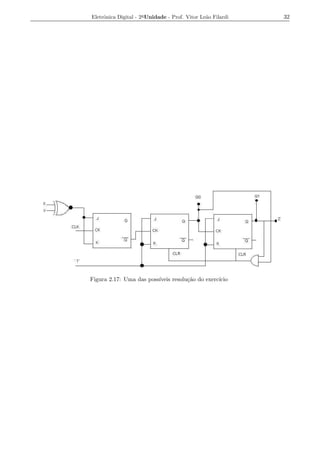

2) A segunda unidade aborda sistemas digitais sequenciais como flip-flops SR, JK, T e D e componentes como registradores de deslocamento e contadores assíncronos e síncronos.

3) A terceira unidade trata de conversores A/D e D/A, multiplexadores

![Referˆncias Bibliogr´ficas

e a

´

IDOETA, I. V.; CAPUANO, F. G. Elementos de Eletrˆnica Digital. [S.l.]: Editora Erica, 1984.

o

´

IDOETA, I. V.; CAPUANO, F. G. Sistemas Digitais-Princ´pios e Aplicacoes. [S.l.]: Editora Erica,

ı

1984.

5](https://image.slidesharecdn.com/apostilacompletadeeletronicadigitafct-120821145637-phpapp02/85/Apostila-completa-de-eletronica-digita-fct-5-320.jpg)