1) O documento apresenta conceitos básicos sobre arquitetura de computadores, incluindo conjuntos de instruções, ciclo de execução de instruções e arquiteturas clássicas.

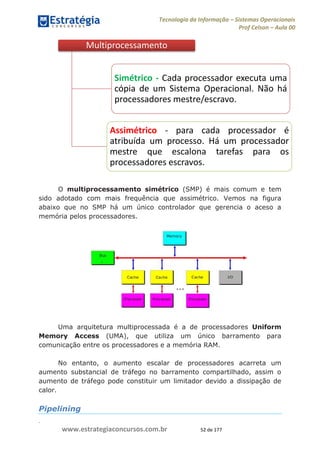

2) É abordada a organização de um computador em unidades funcionais como processamento, armazenamento, transferência e controle de dados.

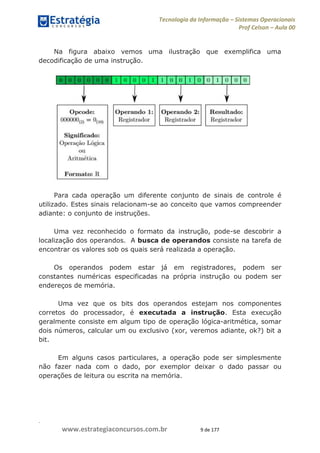

3) Conceitos como CPU, registradores, endereçamento de instruções e barramentos são explicados.