Organização e Características da Memória

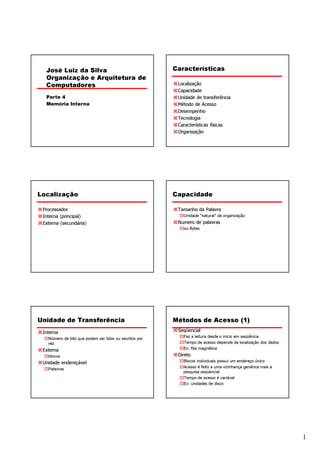

- 1. José Luiz da Silva Características Organização e Arquitetura de Computadores Localização Capacidade Parte 4 Unidade de transferência Memória Interna Método de Acesso Desempenho Tecnologia Características físicas Organização Localização Capacidade Processador Tamanho da Palavra Interna (principal) Unidade “natural” de organização Externa (secundária) Numero de palavras ou Bytes Unidade de Transferência Métodos de Acesso (1) Interna Seqüencial Número de bits que podem ser lidos ou escritos por Faz a leitura desde o início em seqüência vez Tempo de acesso depende da localização dos dados Externa Ex: fita magnética blocos Direto Unidade endereçável Blocos individuais possui um endereço único Acesso é feito a uma vizinhança genérica mais a Palavras pesquisa seqüencial Tempo de acesso é variável Ex: unidades de disco 1

- 2. Métodos de Acesso (2) Hierarquia da Memória Aleatório Endereçamento único identifica a localização exata Registradores Tempo de acesso é independente da localização ou na CPU acessos anteriores Interna ou Memória Principal Ex: RAM Pode incluir um ou mais níveis de cache Associativo “RAM” Os dados são localizados pela comparação com parte Memória Externa de seu conteúdo Armazenamento Tempo de Acesso independe da localização ou acessos anteriores Ex: cache Desempenho Tecnologias Tempo de Acesso Tempo decorrido entre o endereçamento e os dados Semicondutor ficarem disponíveis para utilização RAM Tempo de ciclo de Memória Magnéticas Tempo adicional requerido para a memória se Disco e Fitas “recuperar” antes do próximo acesso Ópticas Tempo de ciclo é o acesso + a recuperação CD e DVD Taxa de Transferência Outras Taxa que os dados podem ser transferidos de/para a Hologramas unidade de memória Características Físicas Organização Volatibilidade Arranjo físico de bits para formar palavras Apagáveis Nem sempre um arranjo óbvio Consumo de energia Ex. intercalado 2

- 3. Lista da Hierarquia Memória de Semicondutor Registradores RAM L1 Cache Toda memória de semicondutor é de acesso aleatório L2 Cache Leitura/escrita Memória principal Volátil Armazenamento temporário Cache de disco Estática ou dinâmica Disco Óptica Fita RAM Dinâmica RAM Estática Bits armazenados com a carga de capacitores Bits armazenados com switches on/off Requer regeneração (refresh) mesmo quando Mais complexa carregada Mais densa Construção simples Mais expansiva Requer refresh dos circuitos Não requer circuitos de refresh Lenta Rápida Memória principal Cache ROM Tipos de ROM Escritas durante a fabricação Armazenamento permanente Muito expansiva para pequenas execuções Microprogramada Programáveis (apenas uma vez) Biblioteca de sub-rotinas PROM Programas de sistemas (BIOS) Requer equipamento especial para gravação Tabelas de funções Leitura Apagável (EPROM) UV Apagável eletricamente (EEPROM) A operação de escrita leva muito tempo em relação a leitura Memória Flash Apagável eletricamente 3

- 4. Organização em detalhes Regeneração (refresh) Uma pastilha de 16Mbits pode ser organizada Circuito de Refresh incluído na pastilha em 1M com palavra de 16bits Desabilitar a pastilha Um sistema de 1 bit por pastilha onde os dados Contador de refresh para todas as linhas são lidos ou gravados 1 bit de cada vez Read & Write back Uma pastilha de 16Mbit pode ser organizada Cronometragem com um 2048 x 4bit elementos Desempenho aparente reduz a velocidade Reduz o número de endereçamento Multiplexa linhas e colunas de endereçamento 11 pinos para endereçamento (211=2048) Adicionando um ou mais pinos dobra a lista de valores x4 da capacidade DRAM Típica de 16 Mb (4M x 4) Empacotamento Organização Organização da Memória da Memória (2) 4

- 5. Correção de Erros Código de correção de erros Falha de hardware Defeitos permanentes Erro de software aleatório, não-destrutivo Não danifica permanentemente a memória Utiliza lógica de detecção e correção de erros Cache Cache operações Pequenas partes de memórias rápida CPU requisita conteúdo da memória Localizada normalmente entre a CPU e a Verifica o cache para estes dados memória principal Se presente, acessa do cache (rápido) Pode ser localizada na CPU ou em módulo Caso contrário, requer leitura de bloco da memória principal para o cache Então entrega do cache para a CPU Cache inclui rótulo para identificar em que bloco da memória principal está armazenado Elementos do projeto de memórias cache Organização típica da cache Tamanho Função de mapeamento Algoritmo de Substituição Políticas de Atualização Tamanho do Bloco Número de Memórias Cache 5

- 6. Função de mapeamento Mapeamento Direto Cache de 64kByte Cada bloco da memória principal mapeia um linha do Cache bloco de 4 bytes cache Ex: se um bloco está no cache, ele precisa estar em um Ex: cache é 16k (214) linhas de 4 bytes específico endereço Memória principal de 16MBytes Endereçamento é em duas partes 24 bit de endereço w bits menos significativos identificam uma única palavra (224=16M) s bits mais significantes especificam um bloco da memória Os MSBs são preenchidos pelo campo da linha de cache (r) e um rótulo de s-r (mais significativo) Mapeamento Direto Mapeamento Direto Estrutura de Endereçamento Tabela de Linha de Cache Linha de Cache Memória Principal mantém Rótulo Linha Palavra o bloco 8 14 2 24 bits de endereço 0 0, m, 2m, 3m…2s-m 1 1,m+1, 2m+1…2s-m+1 2 bits identificam a palavra (4 bytes bloco) 22 bits identificam o bloco 8 bits rótulo (=22-14) m-1 m-1, 2m-1,3m-1…2s-1 14 bits linha Nenhum dos dois bloco na mesma linha tem o mesmo campo de rótulo Verifica conteúdos de cache achando linha e conferindo Rótulo Mapeamento Direto do Cache Organização Mapeamento Direto Exemplo 6

- 7. Mapeamento Direto prós e contras Mapeamento Associativo Simples Um bloco de memória principal pode carregar Não-expansivo em qualquer linha de rótulo Endereço de memória é interpretado como Localização fixa para cada bloco rótulo e palavra Rótulo exclusivo identifica o bloco de memória Se um programa acessar 2 blocos que traçam repetidamente à mesma linha, as perdas de cache são muito altas O rótulo de toda linha é examinado para um acerto Cache procurando fica caro Cache Totalmente Associativo Organização Mapeamento Associativo Exemplo Mapeamento Associativo Conjunto de Mapeamento Estrutura de Endereçamento Associativo Cache é dividido em vários conjuntos Word Cada conjunto contém um número de linhas Tag 22 bit 2 bit 22 bits de rótulo armazenado com cada 32 bits de bloco de dados Um determinado bloco mapeia para qualquer Compara campo rótulo com entrada de rótulo em cache linha em um determinado conjunto conferir ex. Bloco B pode estar em qualquer linha do conjunto i Os 2 bits menos significativos de endereço identificam qual 16 bits da palavra é requerida de 32 bits do bloco ex. 2 linhas por conjunto de dados 2 modos de mapeamento associativo ex. Um determinado bloco pode estar em uma de 2 linhas Address Tag Data Cache line em só conjunto FFFFFC FFFFFC 24682468 3FFF 7

- 8. Conjunto de Mapeamento Associativo Dois modos de conjunto associativo Exemplo Organização da Cache Conjunto de números de 13 bits Número do bloco na memória principal é módulo de 213 000000, 00A000, 00B000, 00C000 … mapeia o mesmo conjunto Mapeamento Associativo – dois Conjunto de Mapeamento Associativo conjuntos de duas linhas Estrutura de Endereçamento Exemplo Word rótulo 9 bit linha 13 bit 2 bit Use o campo da linha para determinar linha de cache para olhar dentro Compare o campo de rótulo para ver se encontrou Ex: Address Tag Data Set number 1FF 7FFC 1FF 12345678 1FFF 001 7FFC 001 11223344 1FFF Algoritmos de Substituição (1) Algoritmos de Substituição (2) Mapeamento Direto Associativo e Conj. Associativo Sem escolha Algoritmo implementado no hardware Cada bloco somente mapeia uma linha Least Recently used (LRU) Substitua a linha First in first out (FIFO) Substitui o bloco que está há mais tempo no cache Menos frequentemente usado (LFU) Substitui o bloco que foi menos utilizado Aleatório 8

- 9. Política de Atualização Write through (escrita direta) Não precisa sobrescrever um bloco na cache se Toda escrita é feita na memória principal e na a memória não foi alterada cache Múltiplas CPUs podem ter caches individuais CPUs múltiplas podem monitorar o tráfego de Dispositivos de E/S podem acessar a memória memória principal para manter a cache local principal diretamente (para CPU) atualizado Muito tráfego Reduz a velocidade de escrita Write back (escrita de volta) Visa minimizar o número de operações de escrita na memória Atualiza inicialmente somente a cache Quando é ocorre a atualização é atribuído 1 ao bit de atualização Se o bloco vai ser substituído, ele apenas é escrito de volta na memória principal se seu bit for igual a 1 E/S tem que acessar a memória principal pela cache NT: 15% das referências à memória são de escrita 9