1) O documento descreve um curso de projeto de sistemas digitais ministrado na FEUP.

2) O curso abrange tópicos como metodologias de projeto, ferramentas de CAD, validação de projetos e implementação de circuitos digitais.

3) O documento fornece uma visão geral dos principais conceitos e etapas envolvidas no projeto de sistemas digitais.

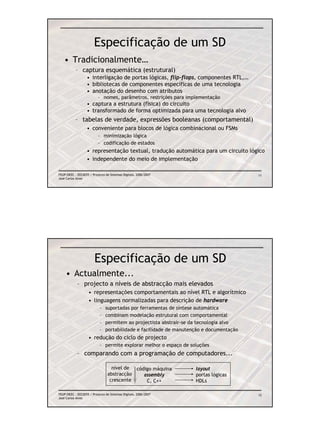

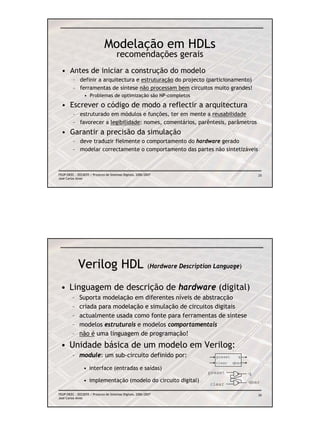

![Verilog - introdução

• Modelo do contador c16

module c16(value, clock, fifteen, ten);

input clock; vector de bits

output [3:0] value;

output fifteen, ten; saídas de 1 bit

Dff D1(value[0], clock, ~value[0]),

D2(value[1], clock, value[1] ^ value[0]),

D3(value[2], clock, value[2] ^ &value[1:0]),

D4(value[3], clock, value[3] ^ &value[2:0]);

assign fifteen = &value; operadores

assign ten = value[3] & ~value[2] & value[1] & ~value[0];

endmodule

saída ten vale 1 quando value = 1010

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 31

José Carlos Alves

Verilog - introdução

• Modelo (comportamental) do Dff

module Dff(q, clock, d);

input clock, d;

output q;

reg q; q é reg porque “segura” um valor

initial

q = 0;

no início da simulação (t=0)

always

@ (negedge clock)

#10 q = d; sempre que clock

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 32

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-16-320.jpg)

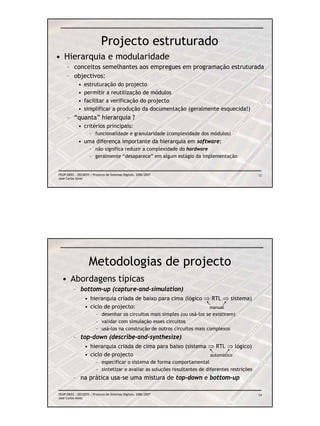

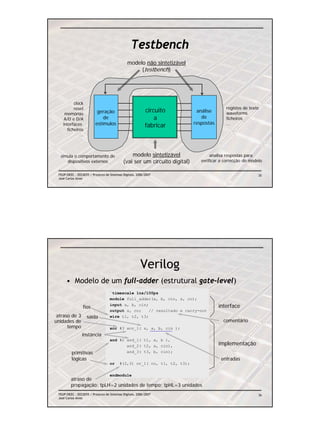

![Verilog - introdução

• Gerador de relógio (clockgen)

module clockgen(clock);

output clock;

reg clock;

initial

#5 clock = 1; para sempre...

always sinal clock gerado:

#50 clock = ~clock;

endmodule

5 50 50

t=0

arredondamento

dos cálculos

unidades de tempo reais: ‘timescale 1ns/100ps

unidade de atraso

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 33

José Carlos Alves

Verilog - introdução

• O circuito completo (módulo counter)

module counter;

wire [3:0] count;

wire clock, ten, fifteen;

c16 contador( count, clock, fifteen, ten);

clockgen clock( clock );

initial

$monitor($time, “ Clk=%b, Count=%d, is_10=%b, is_15=%b”,

clock, count, ten, fifteen);

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 34

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-17-320.jpg)

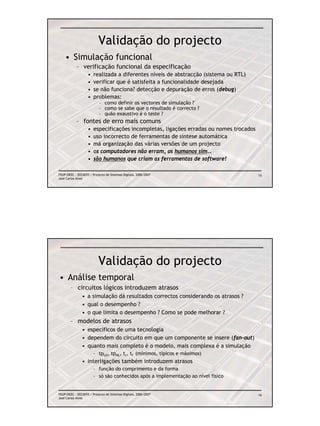

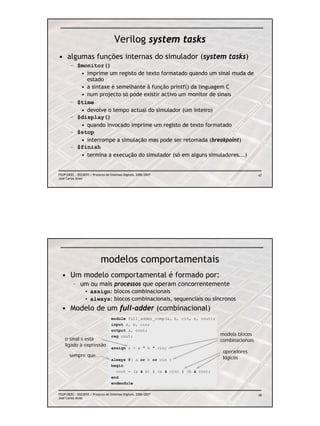

![declaração do interface

• um módulo pode não ter interface

– em módulos usados para teste de outros - testbenches

module myadder_testbench; // sem entradas nem saídas

• declaração de portos de interface:

– portos unidireccionais:

input [7:0] din_a, din_b; // din_a, din_b são entradas de 8 bits

// onde o MSB é din_a[7] e o LSB é din_a[0]

input clock, reset; // clock, reset são entradas de 1 bit

output [0:8] res; // result é uma saída de 9 bits, onde o

// MSB é res[0] e o LSB é res[8]

– portos bidireccionais:

inout [7:0] databus; // databus é um sinal bidireccional de 8 bits:

// pode forçar um nível lógico ou receber um

// sinal do exterior

• todos os sinais declarados como portos de entrada/saída são do tipo wire (fio)

– fios (wires) apenas “propagam” valores lógicos entre uma origem e um destino

– as saídas que “seguram” valores lógicos devem ser declaradas como sinais do tipo reg

• valores lógicos: 1, 0, x (desconhecido) e z (estado de alta impedância)

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 37

José Carlos Alves

declaração de sinais

• sinais do tipo wire representam fios ou barramentos (vários bits)

– servem para transportar um valor lógico desde uma origem que o produz

– um identificador não declarado é considerado um wire de 1 bit

wire en_clock, sel_reg; // fios simples (um bit)

wire [15:0] opr_a, opr_b; // dois barramentos de 16 bits

• sinais do tipo reg representam “registos” (um ou mais bits)

– seguram valores lógicos

reg clock, reset; // registos de 1 bit

reg [7:0] Ra, Rb; // registos de 8 bits

reg [15:0] regfile[0:31]; // vector de 32 registos com 16 bits cada

• campos de vectores de bits

Rb; // todo o registo Rb de 8 bits

opr_a[15:8]; // os 8 bits mais significativos de opr_a

Rb[3]; // o bit 3 do registo Rb

regfile[6]; // o elemento no endereço 6 do vector regfile;

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 38

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-19-320.jpg)

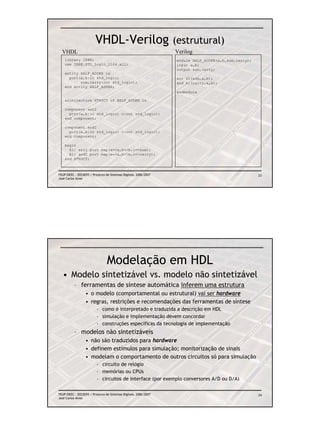

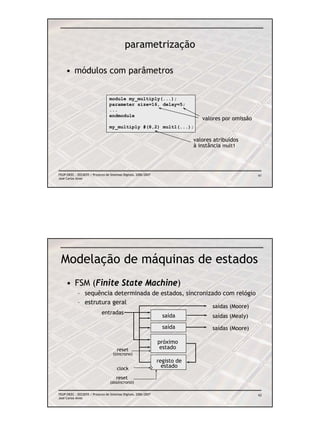

![Verilog – modelos estruturais

• um somador de 4 bits

– usando instâncias do full-adder anterior

a e b são

entradas de

4 bits module four_bit_adder(a, b, cin, s, cout);

input [3:0] a, b;

s é uma input cin;

saída de output [3:0] s;

4 bits output cout; sinais ligados

wire [2:0] cy; por posição

cy é um

bus de 3 bits sinais ligados

full_adder fa_0( a[0], b[0], cin, s[0], cy[0] ),

por nome

fa_1( a[1], b[1], cy[0], s[1], cy[1] ),

nome do

fa_2( a[2], b[2], cy[1], s[2], cy[2] ),

componente

fa_3(.cin(cy[2]),.a(a[3]),.b(b[3]),.s(s[3]),.co(cout));

nomes das

instâncias endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 41

José Carlos Alves

verificação funcional

• um testbench instancia o módulo four_bit_adder.

`timescale 1ns/100ps módulo sem interface (testbench)

module four_bit_adder_testbench;

reg [3:0] a, b;

reg cin; registos (seguram valores)

wire [3:0] s;

wire cout; fios (propagam valores)

o circuito a testar

four_bit_adder adder4(a, b, cin, s, cout);

monitor

initial quando o simulador inicia... de sinais

begin

$monitor($time, “ ci=%b, a=%d, b=%d, s=%d, co=%b”, cin, a, b, s, cout);

estímulos cin=0; a=2; b=4; #30

de b=12; #30 espera 30 unidades de tempo (30ns)

simulação cin=1; #30

a=4'b1110; b=4'b0110; #30

$stop; controlo do simulador (pára)

end

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 42

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-21-320.jpg)

![verificação funcional

• Verificação exaustiva do somador de 4 bits

• e se fosse de 32 bits ? (com 1ns por vector seriam necessários 1170 anos!)

module four_bit_adder_testbench;

reg [3:0] a, b; reg cin;

wire [3:0] s; wire cout;

four_bit_adder adder4(a, b, cin, s, cout);

initial

begin

$monitor($time, “ ci=%b, a=%d, b=%d, s=%d, co=%b", cin, a, b, s, cout);

cin = 0; $display(“Verificacao com carry-in = %b”, cin);

for(a=0;a<15;a=a+1) for(b=0;b<15;b=b+1) #40;

cin = 1; $display(“Verificacao com carry-in = %b”, cin);

for(a=0;a<15;a=a+1) for(b=0;b<15;b=b+1) #40;

$display(“Fim da simulação”); $stop;

end

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 45

José Carlos Alves

constantes

• por omissão: decimal, 32 bits em complemento para dois

– são truncadas se forem atribuídas a sinais com menos bits (a partir do LSB):

reg [3:0] a;

...

initial

begin

a = 28; // 28=11100 -> a fica com 1100=1210

...

end

• pode-se (deve-se) definir o número de bits e a base de

representação:

5’d10; // a constante decimal 10 com 5 bits

10’b1010_0011_11; // constante com 10 bits, em binário

16’h1E_C6; // 16 bits em em hexadecimal

valor (pode-se usar o separador “_” entre dígitos)

base de representação

nº de bits

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 46

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-23-320.jpg)

![modelos comportamentais

• Modelo comportamental do somador de 4 bits

module four_bit_adder_c(a, b, cin, s, cout);

input [3:0] a, b;

input cin;

output [3:0] s;

output cout;

reg cout, s;

reg [5:0] ta, tb, ts; // “registos” temps.

sempre que...

always @( a or b or cin or ta or tb or ts )

begin concatenação de bits

ta = { 1’b0, a, 1’b1 };

tb = { 1’b0, b, cin }; somador

ts = ta + tb;

cout = ts[5]; extrair os resultados

s = ts[4:1];

end

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 49

José Carlos Alves

operadores (semelhantes aos da linguagem C)

operador #opr observações

aritméticos + - * / % 2 operandos são estendidos com zeros

lógicos ! negação lógica 1 zero é falso, não-zero é verdadeiro

&& E lógico 2 retorna 1-verdadeiro ou 0-falso

|| OU lógico 2

relacionais > < >= <= 2 operandos considerados unsigned

igualdade == != 2 comparam apenas zeros e uns

=== !== 2 comparam também os valores z e x

bitwise ~ & | ^ 2 operandos são estendidos com zeros

shift >> << 2 desloca bits e preenche sempre com zeros

concatenação { } N {3’b101,1’b0,3’b111}=7’b1010111

replicação {{ }} N {N{A}} replica N vezes o valor A

condicional ? : 3 igual à expressão condicional de C

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 50

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-25-320.jpg)

![modelação de blocos combinacionais

• assign sinal = expressao;

– Liga permanentemente sinal ao resultado da expressao:

assign #10 opa = { a<<7, ( IR[7:4] & 4’b1010 ? (a+b) : (a-b) ) };

atraso de transporte (não pode ser usado em modelos sintetizáveis)

• always @(a or b or c or ...) begin ... end

– sempre que um sinal da lista muda de estado avalia o bloco:

always @(a or IR or b)

lista de sensibilidades

begin

if ( IR[7:4] & 4’b1010 )

a

opa = { a<<7, (a+b) };

else IR opa

opa = { a<<7, (a-b) }; b

end

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 51

José Carlos Alves

latches em blocos combinacionais

• Num modelo de um circuito combinacional

– as saídas devem ter um valor atribuído para todas as condições das

entradas

– se essa condição não for satisfeita são criadas latches transparentes

– a ocorrência de latches num bloco que se pretendia combinacional

é geralmente FATAL (a ver mais tarde)

always @(a or b or sel)

begin always @(a or b or sel)

if ( sel ) begin

y = a; if ( sel )

else y = a;

y = b; end

end

uma latch transparente

um multiplexer 2÷1

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 52

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-26-320.jpg)

![construções condicionais

if (a[2:0]==3’b010 && cy)

if (condition) ...

statement1

else

statement2 if (a[2:0]===3’b01z && cy)

...

case (expression) case (ir[7:4])

expr1: statement1; 4’b0001: ...

expr2: statement2; 4’b0010: ...

default: statement3; default: ...

endcase; endcase

casez casex (ir[7:4])

(z é don’t care) 4’bxx01: ...

4’bxx10: ...

casex default: ...

(z e x são don’t care) endcase

(expression)?(true):(false) acc=(ir[7:0]==4’b0011) ? 0 : 255;

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 53

José Carlos Alves

ciclos

(utilização restrita em modelos sintetizáveis)

for(start;end_expr;update)

for(i=0;i<8;i=i+1)

statement; x[i] = x[i+1]

while(condition) while(i<8)

statement; begin

...

end

repeat(10)

repeat(fixed_loop_count) begin

statement; a[i]=a[i+1];

i=i+1;

end;

forever statement; forever #10 clock = ~clock;

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 54

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-27-320.jpg)

![modelação de circuitos síncronos

• acumulador de 8 bits

module acc(clk, reset, a, reg_sum);

input clk, reset;

input [7:0] a;

output [7:0] reg_sum;

reg [7:0] reg_sum;

reg_sum “segura” um

valor lógico

always @( negedge clk )

if ( reset )

processo

reg_sum <= 8’d0;

síncrono com clk sempre que clk

else

reg_sum <= a + reg_sum;

endmodule

reset

D Q reg_sum

a

0

clk

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 55

José Carlos Alves

contador up/down

module updown_counter(clk, reset, enable, down, dout, end_count);

input clk, reset, enable, down;

output [3:0] dout;

reg [3:0] dout; processo combinacional

output end_count;

assign end_count = enable & (down ? (dout==0) : (dout==15) );

always @( posedge clk or posedge reset)

begin

if ( reset )

dout <= 0

else processo síncrono

begin com o flanco ascendente

if ( enable ) de clk e reset assíncrono

if ( down )

dout <= dout – 1;

a avaliação do sinal de reset

else

tem de ocorrer no início do

dout <= dout + 1;

bloco begin...end

end

end

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 56

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-28-320.jpg)

![testbench para o contador up/down

`timescale 1ns/100ps

module updown_counter_testbench;

reg clk, reset, enable, down;

wire [3:0] dout; instância do contador

wire end_count;

updown_counter count_1(clk, reset, enable, down, dout, end_count);

initial

begin

down = 0; reset = 0; enable = 1;

#2 reset = 1; // apply reset estímulos

#6 reset = 0; // release reset

#300 // count up 300ns

enable = 0; #40 // disable counter

down = 1; #100 // count down

enable = 1; #300 // enable counter, wait 300ns

$stop; // stop simulation

end

initial clk = 1’b0; sinal de

always #5 clk = ~clk; // 10ns clock period relógio

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 57

José Carlos Alves

atribuições blocking/nonblocking

• Atribuições procedimentais – avaliadas em sequência

Admitindo que in0=4,in1=4,acc=1

begin a1=4, b1=4, y1=8

a1=in0+in1-acc;

y1=a1+b1; a1 = 4+4-1 = 7;

z1=y1+a1; y1 = 7+4 = 11;

end z1 = 11+7 = 18;

• Atribuições non-blocking – avaliadas em paralelo

begin

a1<=in0+in1-acc; a1 = 7;

y1<=a1+b1; y1 = 4+4 = 8;

z1<=y1+a1; z1 = 8+4 = 12;

end

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 58

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-29-320.jpg)

![Máquinas de estados - especificação

• Tabela de transição de estados

entradas estado próximo saídas

i1 i2 corrente estado Yme Ymo

0 X 00 (S0) 00 (S0) 1 0

1 X 00 (S0) 01 (S1) 0 0

X 1 01 (S1) 00 (S0) 0 1

X 0 01 (S1) 10 (S2) 1 1

X X 10 (S2) 00 (S0) 1 1

• Diagrama de transição de estados

Ymo 0 1 Ymo

1X/0 i1/Yme

00 01 i1/Yme S1

S0

0X/1

X1/0 i2/Yme

X0/1 i2/Yme

XX/1

Yme

i1 i2/Yme 10 saídas Mealy S2

1 saídas Moore Ymo

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 65

José Carlos Alves

Máquinas de estados - modelação em Verilog

module FSM_mal(clock, i1, i2, Yme, Ymo);

• Modelo incorrecto input clock, i1, i2;

output Yme, Ymo;

reg Yme, Ymo;

reg [1:0] state;

always @(posedge clock)

Ymo 0 1 case (state)

1X/0 2’b00: begin

00 01

Ymo<=0;

0X/1 if (i1)

X1/0

X0/1 begin

XX/1

state<=2’b01; Yme<=0;

end

i1 i2/Yme 10 else

1 Yme<=1;

end

2’b01: begin

Ymo<=1;

if (i2)

begin

state<=2’b00; Yme<=0;

end

else

begin

state<=2’b10; Yme<=1;

Onde estão os erros ? end

end

2’b10: begin

Ymo<=1; state<=2’b00; Yme<=1;

end

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 66

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-33-320.jpg)

![Máquinas de estados - modelação em Verilog

module FSM_mal(clock, i1, i2, Yme, Ymo);

• Modelo incorrecto input clock, i1, i2;

output Yme, Ymo;

reg Yme, Ymo;

reg [1:0] state;

always @(posedge clock)

case (state)

Ymo 0 1 2’b00: begin

1X/0 Ymo<=0;

00 01 if (i1)

0X/1 begin

X1/0 state<=2’b01; Yme<=0;

X0/1

end

XX/1 else

i1 i2/Yme 10 Yme<=1;

1 end

2’b01: begin

Ymo<=1;

if (i2)

begin

state<=2’b00; Yme<=0;

• falta de reset (síncrono e/ou assíncrono) end

else

• todas as saídas são registadas begin

state<=2’b10; Yme<=1;

• Yme não é saída Mealy end

end

• não é definido o estado inicial 2’b10: begin

• falta o estado 2’b11 Ymo<=1; state<=2’b00; Yme<=1;

end

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 67

José Carlos Alves

Máquinas de estados - modelação em Verilog

always @(state or i1 or i2)

• Modelo correcto begin

case (state)

2’b00: begin

nextstate=2’b00;

Ymo 0 1 Ymo=0;

1X/0 if (i1)

00 01

begin

0X/1 nextstate=2’b01; Yme=0;

X1/0

X0/1 end

else

XX/1 Yme=1;

i1 i2/Yme 10 end

1 2’b01: begin

Lógica de geração Ymo=1;

if (i2)

Memória de estado do próximo estado begin

e das saídas nextstate=2’b00; Yme=0;

end

else

module FSM_bem(reset, clock, begin

i1, i2, Yme, Ymo); nextstate=2’b10; Yme=1;

input reset, clock, i1, i2; end

output Yme, Ymo; end

reg Yme, Ymo; 2’b10: begin

reg [1:0] state, nextstate; Ymo=1; nextstate=2’b00; Yme=1;

end

always @(posedge clock) default: begin

if (reset) Ymo=0; nextstate=2’b00; Yme=1;

state<=2’b00; end

else end

state<=nextstate; endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 68

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-34-320.jpg)

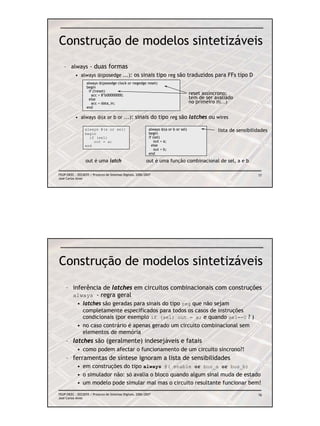

![Construção de modelos sintetizáveis

– inferência de buffers de 3-estados

• atribuindo z a um sinal (do tipo reg)

module three_state(in, out, en);

input in, en;

output out;

reg out;

always @( in or en)

if (en)

out = in;

else assign out = en ? in : 1’bz;

out = 1’bz;

endmodule

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 79

José Carlos Alves

Construção de modelos sintetizáveis

– ciclos

• for(...): só são suportadas 4 formas:

– crescente ou decrescente de passo constante (...;index=index±step)

– condição de terminação com <, >, <= ou >=

always @( a or b or carry )

for(i=0;i<=31;i=i+1)

begin

s[i] = a[i]^b[i]^carry;

carry = a[i]&b[i] | a[i]&carry | b[i]&carry;

end

• while (...): cria um ciclo combinacional;

deve ser quebrado com @(posedge clock)

always @( posedge clock )

while (x<y)

begin

@(posedge clock);

x=x+z;

end

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 80

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-40-320.jpg)

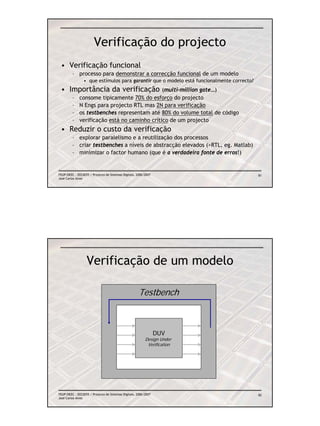

![Sincronização de estímulos

initial // apply reset

begin // for 2 clocks

rst <= 1’b0; clk

clk <= 1’b0;

repeat (2)

#50 clk <= ~clk; rst

rst <= 1’b1;

repeat (4)

#50 clk <= ~clk; não ocorre competição

rst <= 1’b0;

reset muda ao mesmo tempo que clk;

forever #50 clk <= ~clk; quando clk troca, rst ainda tem o estado

end anterior (atribuições non-blocking)

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 109

José Carlos Alves

Entrada de dados de ficheiro

• leitura de dados de um ficheiro de texto para um vector

mem é um vector de registos, por exemplo: reg [15:0] mem[0:127]

filename é o nome do ficheiro de texto que contém os dados

os dados são em ASCII, representando números em binário ou hexadecimal

podem ser incluídos comentários; posições não lidas ficam com ‘xxxx’

$readmemb( “filename”, mem, start_index, end_index); // binário

//ficheiro de dados em binario

@00 // endereço 0x00 (zero, em hexadecimal)

0000_0000_0000_0001 // dado, o caracter ‘_’ é um separador

0000_0000_0000_1000

@10 // os dados seguintes sao colocados a partir do endereço 0x10

0000000000001011

$readmemh( “filename”, mem, start_index, end_index); // hex

//ficheiro de dados em hexadecimal

@00 // endereço 0x00 (zero, em hexadecimal)

00_01 // dado, o caracter ‘_’ é um separador

0AFE

@10 // os dados seguintes sao colocados a partir do endereço 0x10

FF_0B

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 110

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-55-320.jpg)

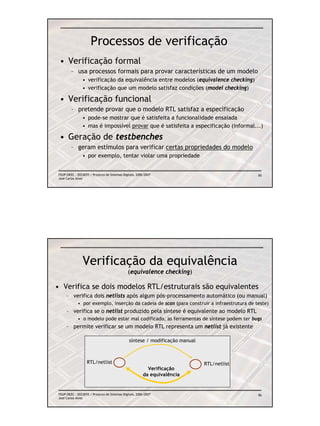

![Saída de dados para ficheiros de texto

• $fopen, $fclose, $fmonitor, $fwrite, $fdisplay

integer HI, HQ; // File handlers

initial // open output files

begin

HI = $fopen(“dout_I.dat”);

HQ = $fopen(“dout_Q.dat”);

// simulate ... close files

$fclose(HI); $fclose(HQ);

end

initial

$fmonitor(fh,...); // $monitor para ficheiro

always @(posedge clock)

begin

$fdisplay( HI, “%d”, HI); // inclui newline

$fwrite( HQ, “%dn”, HQ); // nao inclui newline

end

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 111

José Carlos Alves

Monitorização de valores

• nomes hierárquicos – operador . (ponto)

task dump_regfile; // dump CPU registers

integer i;

begin

for(i=0;i<8;i=i+1)

$display(“R%d=%d (%h)”, i, mycpu.regfile_1.regs[i],

mycpu.regfile_1.regs[i] )

end

initial

begin

// apply reset and check initial state

$display(“Ctrl unit initial state: %b”, mycpu.ctrl_1.state);

end

mycpu

sinal da instância ctrl_1 dentro de mycpu ctrl_1

reg [4:0] state;

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 112

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-56-320.jpg)

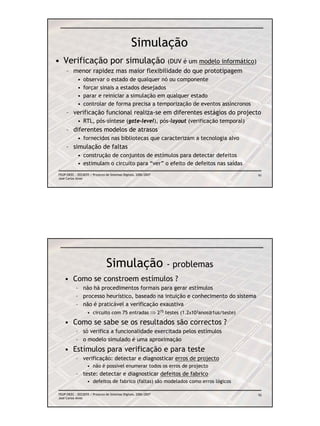

![Geração de números aleatórios

• geração de estímulos aleatórios (valor ou tempo)

$random(seed); // inicia o gerador de números aleatórios

x = $random; // retorna um inteiro aleatório (32 bits)

x = $random / 32’h0fff_ffff; // inteiro entre [0..15]

• especificação de atrasos não constantes: #( expressão )

integer x;

reg [15:0] y;

reg [7:0] cmd;

x = $random / 32’h00ff_ffff; y = $random / 32’h0fff_fffa;

cmd = $random / 32’h3fff_ffff;

for(i=0; i<MAXLOOP; i=i+1)

begin

#(x) apply_initcommand;

#(x*y/3) send_command( cmd, data);

end

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 113

José Carlos Alves

tasks

• Sub-rotinas em Verilog

– Interesse particular para a construção de testbenches

– Podem conter atrasos, chamadas a outras tasks

task writecommand;

input [15:0] data; // data to write

input [1:0] address; // address of output port

begin

din = {4'b0010, 2’b00, address}; // compose and write

command

load = 1; #10 load = 0; #10 // ld for 1 clock

din = data[15:8]; // send MS byte

load = 1; #10 load = 0; #20 // ld for 2 clocks

din = data[7:0]; // send LS byte

load = 1; #10 load = 0; #30 load = 0;

end initial

endtask begin

…

writecommand(16'h39A6, 2'b00 );

FEUP/DEEC : EEC0055 / Projecto de Sistemas Digitais, 2006/2007 114

José Carlos Alves](https://image.slidesharecdn.com/vhdlmux-111020143251-phpapp02/85/Vhdl-mux-57-320.jpg)