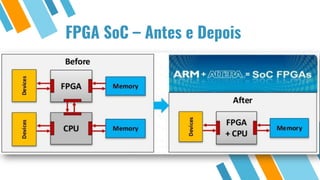

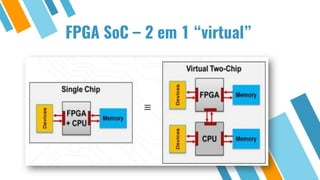

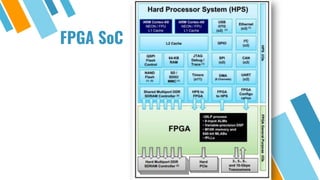

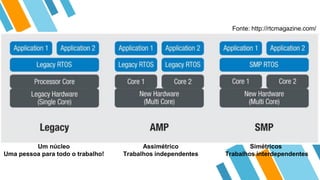

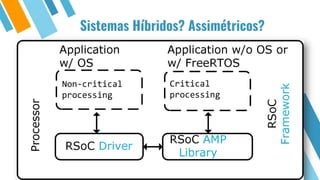

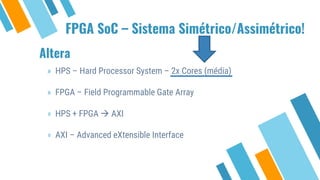

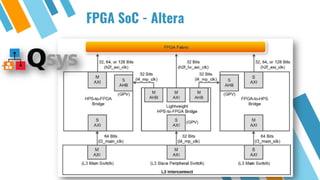

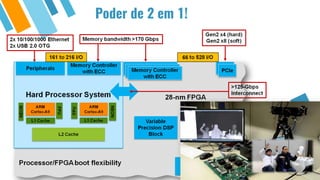

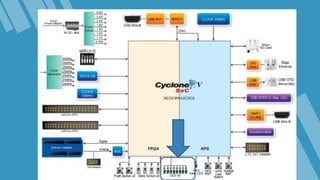

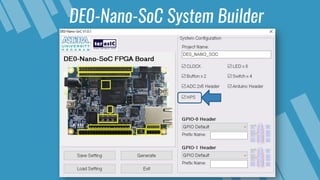

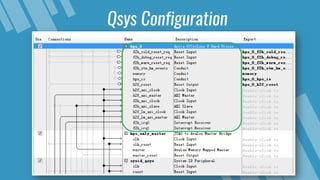

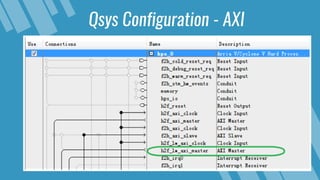

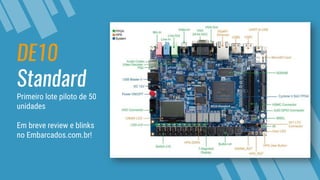

O documento discute sistemas híbridos que combinam processadores ARM e FPGA. Esses sistemas podem dividir tarefas entre o ARM para execução do sistema operacional e a FPGA para funções personalizadas como DSP. Isso permite aproveitar as vantagens de ambos os mundos com desempenho e flexibilidade. O documento apresenta um exemplo prático usando uma placa DE0-Nano-SoC.