Ec ii lab manual

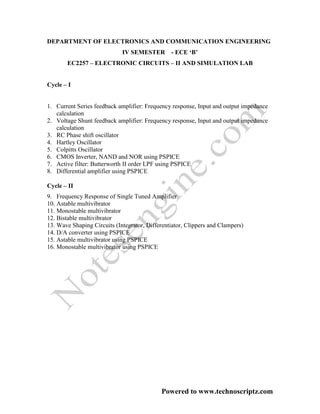

- 1. DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING IV SEMESTER - ECE ‘B’ EC2257 – ELECTRONIC CIRCUITS – II AND SIMULATION LAB Cycle – I 1. Current Series feedback amplifier: Frequency response, Input and output impedance calculation 2. Voltage Shunt feedback amplifier: Frequency response, Input and output impedance calculation 3. RC Phase shift oscillator 4. Hartley Oscillator 5. Colpitts Oscillator 6. CMOS Inverter, NAND and NOR using PSPICE 7. Active filter: Butterworth II order LPF using PSPICE 8. Differential amplifier using PSPICE Cycle – II 9. Frequency Response of Single Tuned Amplifier 10. Astable multivibrator 11. Monostable multivibrator 12. Bistable multivibrator 13. Wave Shaping Circuits (Integrator, Differentiator, Clippers and Clampers) 14. D/A converter using PSPICE 15. Astable multivibrator using PSPICE 16. Monostable multivibrator using PSPICE Powered to www.technoscriptz.com

- 2. Expt No: 1 CURRENT-SERIES FEEDBACK AMPLIFIER Aim: To design and test the current-series feedback amplifier and to calculate the following parameters with and without feedback. 1. Mid band gain. 2. Bandwidth and cut-off frequencies. 3. Input and output impedance. Components & Equipment required: Range / Sl. No. Components / Equipment Quantity Specifications 1 Power supply (0-30)V 1 2 Function generator (0-20M)Hz 1 3 CRO 1 4 Transistor BC107 1 5 Resistors 6 Capacitors 7 Connecting wires Accordingly Circuit diagram: (i) Without feedback: Vcc = +12V R1 RC Cout C Cin RL B BC107 CRO E Vin=50mV f=(1-3M)Hz R2 RE CE 0 2

- 3. (ii) With feedback: Vcc = +12V R1 RC Cout C Cin RL B BC107 CRO E Vin=50mV f=(1-3M)Hz R2 RE 0 Theory: The current series feedback amplifier is characterized by having shunt sampling and series mixing. In amplifiers, there is a sampling network, which samples the output and gives to the feedback network. The feedback signal is mixed with input signal by either shunt or series mixing technique. Due to shunt sampling the output resistance increases by a factor of ‘D’ and the input resistance is also increased by the same factor due to series mixing. This is basically transconductance amplifier. Its input is voltage which is amplified as current. Design: (i) Without feedback: VCC = 12V; IC = 1mA; fL = 50Hz; S = 2; RL = 4.7K; hfe = re = 26mV / IC = 26; hie = hfe re = VCE= Vcc/2 (transistor Active) = VE = IERE = Vcc/10 Applying KVL to output loop, we get VCC = ICRC + VCE + IERE 3

- 4. RC = Since IB is very small when compare with IC, IC IE RE = VE / IE = S = 1+ RB / RE = 2 RB = VB = VCC R2 / (R1 + R2) RB = R1 || R2 R1 = R2 = XCi = Zi / 10 = (hie || RB) / 10 = Ci = 1 / (2f XCi) = Xco = (RC || RL)/10 = Co = 1 / (2f XCo) = XCE = RE/10 = CE = 1 / (2f XCE) = (ii) With feedback (Remove the Emitter Capacitor, CE): Feedback factor, = -RE = Gm = -hfe / (hie + RE) = Desensitivity factor, D = 1 + Gm = Transconductance with feedback, Gmf = Gm / D = Input impedance with feedback, Zif = Zi D Output impedance with feedback, Z0f = Z0 D Procedure: 1. Connect the circuit as per the circuit diagram. 2. Keeping the input voltage constant, vary the frequency from 50Hz to 3MHz in regular steps and note down the corresponding output voltage. 3. Plot the graph: Gain (dB) Vs Frequency 4. Calculate the bandwidth from the graph. 5. Calculate the input and output impedance. 6. Remove Emitter Capacitance, and follow the same procedures (1 to 5). 4

- 5. Tabular column: (i) Without feedback: Vi = Frequency Output Voltage Gain = 20 log(V0/Vi) Sl. No Gain = V0/Vi (Hz) (V0) (volts) (dB) (ii) With feedback: Vi = Frequency Output Voltage Gain = 20 log(V0/Vi) Sl. No Gain = V0/Vi (Hz) (V0) (volts) (dB) Model graph: (frequency response) Gain in dB Without feedback With feedback Frequency in Hz Result: Thus the current series feedback amplifier is designed and constructed and the following parameters are calculated. Theoretical Practical With feedback Without feedback With feedback Without feedback Input impedance Output impedance Gain (midband) Bandwidth 5

- 6. Expt. No. 2 VOLTAGE SHUNT FEEDBACK AMPLIFIER Aim: To design and test the voltage-shunt feedback amplifier and to calculate the following parameters with and without feedback. 1. Mid band gain. 2. Bandwidth and cut-off frequencies. 3. Input and output impedance. Components & Equipment required: Range / Sl. No. Components / Equipment Quantity Specifications 1 Power supply (0-30)V 1 2 Function generator (0-20M)Hz 1 3 CRO 1 4 Transistor BC107 1 5 Resistors 6 Capacitors 7 Connecting wires Circuit Diagram: (i) Without Feedback: Vcc = +12V R1 RC Cout C Cin B BC107 E CRO Vin=50mV f=(1-3M)Hz R2 RE CE 0 6

- 7. (ii) With Feedback: Vcc = +12V R1 RC Rf Cf Cout C Cin BC107 B CRO E Vin=50mV f=(1-3M)Hz R2 RE CE 0 Theory: In voltage shunt feedback amplifier, the feedback signal voltage is given to the base of the transistor in shunt through the base resistor RB. This shunt connection tends to decrease the input resistance and the voltage feedback tends to decrease the output resistance. In the circuit RB appears directly across the input base terminal and output collector terminal. A part of output is feedback to input through RB and increase in IC decreases IB. Thus negative feedback exists in the circuit. So this circuit is also called voltage feedback bias circuit. This feedback amplifier is known an transresistance amplifier. It amplifies the input current to required voltage levels. The feedback path consists of a resistor and a capacitor. Design (i) Without Feedback: VCC = 12V; IC = 1mA; AV = 30; Rf = 2.5K; S = 2; hfe = ; =1/ Rf = 0.0004 re = 26mV / IC = 26; hie = hfe re = VCE= Vcc/2 (transistor Active) = VE = IERE = Vcc/10 = 7

- 8. Applying KVL to output loop, we get VCC = ICRC + VCE + IERE RC = Since IB is very small when compare with IC, IC IE RE = VE / IE = S = 1+ RB / RE RB = VB = VCC R2 / (R1 + R2) RB = R1 || R2 R1 = R2 = (ii) With feedback: RO = RC || Rf = Ri = (RB || hie ) Rf = Rm = -(hfe (RB || Rf) (RC || Rf)) / ((RB || Rf) + hie) = Desensitivity factor, D = 1 + Rm Rif = Ri / D = Rof = Ro / D = Rmf = Rm / D = XCi = Rif /10 = Ci = 1 / (2f XCi) = Xco = Rof /10 = Co = 1 / (2f XCo) = RE’ = RE || ((RB + hie) / (1+hfe)) XCE = RE’/10 = CE = 1 / (2f XCE) = XCf = Rf/10 Cf = 1 / (2f XCf) = Procedure: 1. Connect the circuit as per the circuit diagram. 2. Keeping the input voltage constant, vary the frequency from 50Hz to 3MHz in regular steps and note down the corresponding output voltage. 3. Plot the graph: Gain (dB) Vs Frequency 8

- 9. 4. Calculate the bandwidth from the graph. 5. Calculate the input and output impedance. 6. Remove Emitter Capacitance, and follow the same procedures (1 to 5). Tabular Column: (i) Without Feedback: Vi = 10 mV Frequency V0 Gain = V0/Vi Gain (dB) = 20 log(V0/Vi) (volts) (ii) With Feedback: Vi = 10 mV Frequency V0 Gain = V0/Vi Gain (dB) = 20 log(V0/Vi) (volts) Model graph: (frequency response) Gain in dB Without feedback With feedback Frequency in Hz Result: Thus the current series feedback amplifier is designed and constructed and the following parameters are calculated. Theoretical Practical With feedback Without feedback With feedback Without feedback Input impedance Output impedance Gain (midband) Bandwidth 9

- 10. Expt. No. 3 RC PHASE SHIFT OSCILLATOR Aim: To design and construct a RC phase shift oscillator for the given frequency (f0). Components & Equipment required: Range / Sl. No. Components / Equipment Quantity Specifications 1 Power supply (0-30)V 1 2 Function generator (0-20M)Hz 1 3 CRO 1 4 Transistor BC107 1 5 Resistors 6 Capacitors 7 Connecting wires Accordingly Circuit Diagram: Vcc = +12V R1 RC Cout C Cin B BC107 E RL CRO R2 RE CE 0 C C C R R R 0 10

- 11. Theory: In the RC phase shift oscillator, the required phase shift of 180˚ in the feedback loop from the output to input is obtained by using R and C components, instead of tank circuit. Here a common emitter amplifier is used in forward path followed by three sections of RC phase network in the reverse path with the output of the last section being returned to the input of the amplifier. The phase shift Ф is given by each RC section Ф=tanˉ1 (1/ωrc). In practice R-value is adjusted such that Ф becomes 60˚. If the value of R and C are chosen such that the given frequency for the phase shift of each RC section is 60˚. Therefore at a specific frequency the total phase shift from base to transistor’s around circuit and back to base is exactly 360˚ or 0˚. Thus the Barkhausen criterion for oscillation is satisfied Design: VCC = 12V; IC = 1mA; C = 0.01F; fo = ; S = 2; hfe = re = 26mV / IC = 26; hie = hfe re = VCE= Vcc/2 (transistor Active) = VE = IERE = Vcc/10 Applying KVL to output loop, we get VCC = ICRC + VCE + IERE RC = Since IB is very small when compare with IC, IC IE RE = VE / IE = S = 1+ RB / RE = 2 RB = VB = VBE + VE = VB = VCC R2 / (R1 + R2) RB = R1 || R2 R1 = R2 = Gain formula is given by, h fe R Leff AV = (Av = -29, design given) h ie Effective load resistance is given by, Rleff = Rc || RL RL = 11

- 12. XCi = {[hie+(1+hfe)RE] || RB}/10 = Ci = 1 / (2f XCi) = Xco = Rleff /10 = Co = 1 / (2f XCo) = XCE = RE/10 = CE = 1 / (2f XCE) = Feedback Network: f0 = ; C = 0.01f; 1 fo = 2 6RC R= Procedure: 1. Connections are made as per the circuit diagram. 2. Switch on the power supply and observe the output on the CRO (sine wave). 3. Note down the practical frequency and compare with its theoretical frequency. Model Graph: Vout (Voltage) Time(ms) Result: Thus RC phase shift oscillator is designed and constructed and the output sine wave frequency is calculated as Theoretical Practical Frequency 12

- 13. Expt. No.4 HARTELY OSCILLATOR Aim: To design and construct the given oscillator for the given frequency (fO). Components & Equipment required: Range / Sl. No. Components / Equipment Quantity Specifications 1 Power supply (0-30)V 1 2 Function generator (0-20M)Hz 1 3 CRO 1 4 Transistor BC107 1 5 Resistors 6 Capacitors 7 DIB 8 DCB 9 Connecting wires Accordingly Circuit Diagram: Vcc = +12V R1 RC Cout C Cin B BC107 CRO E RL R2 RE CE 0 C L1 L2 0 13

- 14. Theory: Hartley oscillator is a type of sine wave generator. The oscillator derives its initial output from the noise signals present in the circuit. After considerable time, it gains strength and thereby producing sustained oscillations. Hartley Oscillator have two major parts namely – amplifier part and feedback part. The amplifier part has a typically CE amplifier with voltage divider bias. In the feedback path, there is a LCL network. The feedback network generally provides a fraction of output as feedback. Design: VCC = 12V; IC = 1mA; fo = ; S = 2; hfe = re = 26mV / IC = 26; hie = hfe re = VCE= Vcc/2 (transistor Active) = VE = IERE = Vcc/10 Applying KVL to output loop, we get VCC = ICRC + VCE + IERE RC = Since IB is very small when compare with IC, IC IE RE = VE / IE = S = 1+ RB / RE = 2 RB = VB = VBE + VE = VB = VCC R2 / (R1 + R2) RB = R1 || R2 R1 = R2 = Gain formula is given by, h fe R Leff AV = (Av = -29, design given) h ie Effective load resistance is given by, Rleff = Rc || RL RL = XCi = {[hie+(1+hfe)RE] || RB}/10 = Ci = 1 / (2f XCi) = Xco = Rleff /10 = 14

- 15. Co = 1 / (2f XCo) = XCE = RE/10 = CE = 1 / (2f XCE) = Feedback Network: f0 = ; L1 = 1mH; L2 = 10mH 1 L A= = 1 L2 1 f= 2 L1 L 2 C C= Procedure: 1. Connections are made as per the circuit diagram. 2. Switch on the power supply and observe the output on the CRO (sine wave). 3. Note down the practical frequency and compare with its theoretical frequency. Model Graph: Vout (Voltage) Time(ms) Result: Thus Hartley oscillator is designed and constructed and the output sine wave frequency is calculated as Theoretical Practical Frequency 15

- 16. Expt. No.5 COLPITTS OSCILLATOR Aim: To design and construct the given oscillator at the given operating frequency. Equipments required: Range / Sl. No. Components / Equipment Quantity Specifications 1 Power supply (0-30)V 1 2 Function generator (0-20M)Hz 1 3 CRO 1 4 Transistor BC107 1 5 Resistors 6 Capacitors 7 DIB 8 DCB 9 Connecting wires Circuit Diagram: Vcc = +12V R1 RC Cout C Cin B BC107 CRO E RL R2 RE CE 0 L C1 C2 0 16

- 17. Theory: A Colpitts oscillator is the electrical dual of a Hartley oscillator. In the Colpitts circuit, two capacitors and one inductor determine the frequency of oscillation. The oscillator derives its initial output from the noise signals present in the circuit. After considerable time, it gains strength and thereby producing sustained oscillations. It has two major parts namely – amplifier part and feedback part. The amplifier part has a typically CE amplifier with voltage divider bias. In the feedback path, there is a CLC network. The feedback network generally provides a fraction of output as feedback. Design: VCC = 12V; IC = 1mA; fo = ; S = 2; hfe = re = 26mV / IC = 26; hie = hfe re = VCE= Vcc/2 (transistor Active) = VE = IERE = Vcc/10 Applying KVL to output loop, we get VCC = ICRC + VCE + IERE RC = Since IB is very small when compare with IC, IC IE RE = VE / IE = S = 1+ RB / RE = 2 RB = VB = VBE + VE = VB = VCC R2 / (R1 + R2) RB = R1 || R2 R1 = R2 = Gain formula is given by, h fe R Leff AV = (Av = -29, design given) h ie Effective load resistance is given by, Rleff = Rc || RL RL = XCi = {[hie+(1+hfe)RE] || RB}/10 = Ci = 1 / (2f XCi) = Xco = Rleff /10 = 17

- 18. Co = 1 / (2f XCo) = XCE = RE/10 = CE = 1 / (2f XCE) = Feedback Network: f0 = ; C1 = ; C2 = 1 C A= = 2 C1 1 C1 C 2 f= 2 LC1C 2 L= Procedure: 1. Rig up the circuit as per the circuit diagrams (both oscillators). 2. Switches on the power supply and observe the output on the CRO (sine wave). 3. Note down the practical frequency and compare with its theoretical frequency. Model Graph: Vout (Voltage) Time(ms) Result: Thus Colpitts oscillator is designed and constructed and the output sine wave frequency is calculated as Theoretical Practical Frequency 18

- 19. Expt. No. 6 CMOS Inverter, NAND and NOR using PSPICE Aim: To plot the transient characteristics of output voltage for the given CMOS inverter, NAND and NOR from 0 to 80s in steps of 1s. To calculate the voltage gain, input impedance and output impedance for the input voltage of 5V. Parameter Table: Parameters PMOS NMOS L 1 1 W 20 5 VTO -2 2 KP 4.5E-4 2 CBD 5p 5p CBS 2p 2p RD 5 5 RS 2 2 RB 0 0 RG 0 0 RDS 1Meg 1Meg CGSO 1p 1p CGDO 1p 1p CGBO 1p 1p Circuit Diagram: (i) Inverter: VDD = +5V 3 S G Q1 D 1 Vin 2 Vout D Q2 RL = 100K G S 0 19

- 20. (ii) NAND VDD = +5V 2 S S G G Q2 Q1 D D 4 Vout D Q3 G Vin1 S 1 RL = 100K D Q4 G Vin2 3 S (iii) NOR VDD = +5V 3 Vin1 1 G S Q1 D 2 G S Vin2 Q2 D 4 Vout D D Q3 Q4 G G RL = 100K S S 20

- 21. Theory: (i) Inverter CMOS is widely used in digital IC’s because of their high speed, low power dissipation and it can be operated at high voltages resulting in improved noise immunity. The inverter consists of two MOSFETs. The source of p-channel device is connected to +VDD and that of n-channel device is connected to ground. The gates of two devices are connected as common input. (ii) NAND It consists of two p-channel MOSFETs connected in parallel and two n-channel MOSFETs connected in series. P-channel MOSFET is ON when gate is negative and N- channel MOSFET is ON when gate is positive. Thus when both input is low and when either of input is low, the output is high. (iii) NOR It consists of two p-channel MOSFETs connected in series and two n-channel MOSFETs connected in parallel. P-channel MOSFET is ON when gate is negative and N-channel MOSFET is ON when gate is positive. Thus when both inputs are high and when either of input is high, the output is low. When both the inputs are low, the output is high. Truth Table: (i) Inverter Input Output 0 1 1 0 (ii) NAND V1 V2 Output 0 0 1 0 1 1 1 0 1 1 1 0 (iii) NOR V1 V2 Output 0 0 1 0 1 0 1 0 0 1 1 0 21

- 22. Model Graph: (i) Inverter Voltage Input Waveform 5V time (s) 0 10 20 30 40 50 60 70 80 Output Waveform 5V time (s) 0 10 20 30 40 50 60 70 80 (ii) NAND Voltage Input Waveform time (s) 0 10 20 30 40 50 60 70 80 Output Waveform time (s) 0 10 20 30 40 50 60 70 80 time (s) 0 10 20 30 40 50 60 70 80 22

- 23. (iii) NOR Voltage Input Waveform time (s) 0 10 20 30 40 50 60 70 80 Output Waveform 0 10 20 30 40 50 60 70 80 time (s) time (s) 0 10 20 30 40 50 60 70 80 Output: (i) Inverter Gain = V(2)/Vin = Input Resistance at Vin = Output Resistance at V(2) = (ii) NAND Gain = V(4)/Vin1 = V(4)/Vin2 = Input Resistance at Vin1 = Input Resistance at Vin2 = Output Resistance at V(4) = (iii) NOR Gain = V(4)/Vin1 = V(4)/Vin2 = Input Resistance at Vin1 = Input Resistance at Vin2 = Output Resistance at V(4) = Result: Thus the transient characteristics of output voltage for the given CMOS inverter, NAND and NOR is plotted and the voltage gain, input impedance and output impedance are calculated. 23

- 24. Expt. No.7 SECOND ORDER BUTTERWORTH - LOW PASS FILTER Aim: To design and implement the second order butterworth Low pass filter using PSPICE. Circuit Diagram: RIN 1K RF 586 ohm 2 0 V+ 7 2 - R1 R2 6 6 VOUT 5 3 3 + 1 LM741 1.59K 1.59K 4 RL V- VIN C2 0.1u 10K C1 0.1u 1V (100 - 10K)Hz 0 Theory: A Low pass filter has a constant gain from 0 to fH. Hence the bandwidth of the filter is fH. The range of frequency from 0 to fH is called pass band. The range of frequencies beyond fH is completely attenuated and it is called as stop band. Design: fH = 1000HZ C1= C2 =0.1F RIN=1000 fH = 1 / 2RC R = 1 / 2CfH R = R1 = R2 = 1592 24

- 25. Gain = 1.586 1.586 = 1 + (RF / RIN) RF = 586 Model Graph: Gain (dB) 3dB Frequency (HZ) fH Result: Thus Low pass filter is designed and implemented using PSPICE. 25

- 26. Expt. No.8 DIFFERENTIAL AMPLIFIER Aim: To implement the differential amplifier using PSPICE. Circuit Diagram: RF 10K V+ RIN 10K 7 VIN 1 2 2 - 6 1 LM741 6 3 + Vout VIN 2 5 R2 10K 3 4 RCOMP V- 10K Theory: A differential amplifier amplifies the difference between two voltages V1 and V2. The output of the differential amplifier is dependent on the difference between two signals and the common mode signal since it finds the difference between two inputs it can be used as a subtractor. The output of differential amplifier is RF VO = (V2 – V1) R1 26

- 27. Model Graph: Voltage V1 time V2 time V3 time Calculation: V1 = 5V V2 = 10V RF 10K VO = (V2 – V1) = (10 – 5) R1 10K VO = 5V Output: VO = 5V Result: Thus a differential amplifier is implemented using operational amplifier. 27

- 28. Expt. No.9 FREQUENCY RESPONSE OF SINGLE TUNED AMPLIFIER Aim: To design and construct a single tuned amplifier and to plot the frequency response. Equipment Required: Range / Sl. No. Components / Equipment Quantity Specifications 1 Power supply (0-30)V 1 2 Function generator (0-20M)Hz 1 3 CRO 1 4 Transistor BC107 1 5 Resistors 6 Capacitors 7 DIB 8 DCB 9 Connecting wires Circuit Diagram: VCC = +10V R1 L C Cout C Cin B BC107 E RL CRO V=50mV R2 RE f=(1-3M)Hz CE 28

- 29. Design: VCC = 12V; IC = 1mA; fo = ; S = 2; hfe = Q = 5; L = 1mH re = 26mV / IC = 26; hie = hfe re = VCE= Vcc/2 (transistor Active) = VE = IERE = Vcc/10 Applying KVL to output loop, we get VCC = ICRC + VCE + IERE RC = Since IB is very small when compare with IC, IC IE RE = VE / IE = S = 1+ RB / RE = 2 RB = VB = VBE + VE = VB = VCC R2 / (R1 + R2) RB = R1 || R2 R1 = R2 = RL = XCi = {[hie+(1+hfe)RE] || RB}/10 = Ci = 1 / (2f XCi) = Xco = (RC||RL) /10 = Co = 1 / (2f XCo) = XCE = RE/10 = CE = 1 / (2f XCE) = Q = RL / L RL = 1 f0 = 2 LC C= 29

- 30. Procedure: 1. Connect the circuit as per the circuit diagram. 2. Set Vi = 50 mV (say), using the signal generator. 3. Keeping the input voltage constant, vary the frequency from 0Hz to3MHz in regular steps and note down the corresponding output voltage. 4. Plot the graph: Gain (dB) Vs Frequency Tabular Column: Vi = 50 mV Frequency V0 (volts) Gain (dB) = 20 log(V0/Vi) Model Graph: (Frequency Response) GAIN (dB) |A| (dB) fc FREQUENCY Result: Thus single tuned amplifier is designed and constructed for the given operating frequency and the frequency response is plotted. 30

- 31. Expt. No.10 ASTABLE MULTIVIBRATOR Aim: To design and construct an astable multivibrator using transistor and to plot the output waveform. Components / Equipments Required: Range / Sl. No. Item name Quantity Specification 1 Transistor BC107 2 2 Resistors 4.9K, 1.6M 2 each 3 Capacitors 0.45nF 2 4 CRO (0-20M)Hz 1 5 Power Supply (0-30)V 1 6 Connecting Wires Accordingly Circuit Diagram: Vcc = +12V RC R R RC 5.9K 1.5M 1.5M 5.9K C Vo1 C 0.48nF Vo2 0.48nF C B C BC107 BC107 B E E 0 31

- 32. Theory: Astable multivibrator is also known as free running multivibrator. It is rectangular wave shaping circuit having non-stable states. This circuit does not need an external trigger to change state. It consists of two similar NPN transistors. They are capacitor coupled. It has 2 quasi-stable states. It switches between the two states without any applications of input trigger pulses. Thus it produces a square wave output without any input trigger. The time period of the output square wave is given by, T = 1.38RC. Design Procedure: VCC = 10V; IC = 2mA; VCE (sat) = 0.2V; f = 1KHz; hfe = VCC - VCE (sat) 12 – 0.2 RC = = = 5.9K IC 0.002 R hfe RC = 315 * 5.9 * 103 = 1.85M R = 1.5M T = 1.38RC C = T / (1.38R) = (1 * 10-3) / (1.38 * 1.5 * 106)= 0.48nF Procedure: 1. Connections are made as per the circuit diagram. 2. Switch on the power supply. 3. Note down the output TON, TOFF and output voltage from CRO. 4. Plot the output waveform in the graph. Tabular Column: Amplitude TON TOFF Frequency (in volts) (ms) (ms) (in Hz) Vo1 Vo2 32

- 33. Model Graph: Vo1 (Volts) Time (ms) Vo2 (Volts) Time (ms) RESULT: Thus the astable multivibrator is designed and constructed using transistor and its output waveform is plotted. 33

- 34. Expt. No.11 MONOSTABLE MULTIVIBRATOR Aim: To design and construct monostable multivibrator using transistor and to plot the output waveform. Components / Equipments Required: Sl. No. Item name Range / Specification Quantity 1 Transistor BC107 2 2 Resistors 4.9K, 1.6M 2 each 3 Capacitors 0.45nF 2 4 CRO (0-20M)Hz 1 5 Power Supply (0-30)V 1 6 Connecting Wires Accordingly Circuit Diagram: VCC = +12V RC 5.9K RC R 5.9K 1.13M 10K R1 Vo1 C D1 C1 1N4007 1.28nF Vo2 25nF C C B B BC107 BC107 E E R2 100K VBB = -2V 0 34

- 35. Theory: Monostable multivibrator has two states which are (i) quasi-stable state and (ii) stable state. When a trigger input is given to the monostable multivibrator, it switches between two states. It has resistor coupling with one transistor. The other transistor has capacitive coupling. The capacitor is used to increase the speed of switching. The resistor R2 is used to provide negative voltage to the base so that Q1 is OFF and Q2 is ON. Thus an output square wave is obtained from monostable multivibrator. Design Procedure: VCC = 12V; VBB = -2V; IC = 2mA; VCE (sat) = 0.2V; f = 1KHz; hfe = VCC - VCE (sat) 12 – 0.2 RC = = = 5.9K IC 0.002 IB2(min) = IC2 / hfe = Select IB2 > IB2(min) IB2 = VCC – VBE (sat) R= = I B2 T = 0.69RC C = T / 0.69R = -VBBR1 VCE (sat) R2 VB1 = + R1 + R2 R1 + R2 VBBR1 VCE (sat) R2 = (since, V B1 is very less) R1 + R2 R 1 + R2 VBBR1 = VCE (sat) R2 R2 =10R1 (since, VBB = 2V and VCE (sat) = 0.2V) Let R1 = 10K, then R2 = 100K Choose C1 = 25pF. Procedure: 1. Connections are made as per the circuit diagram. 2. Switch on the power supply. 35

- 36. 3. Observe the output at collector terminals. 4. Trigger Monostable with pulse and note down the output TON, TOFF and voltage from CRO. 5. Plot the waveform in the graph. Tabular Column: Width Input Output (ms) TON TOFF Voltage TON TOFF Voltage (ms) (ms) (Volts) (ms) (ms) (Volts) Model Graph: Vo1 (Volts) Time (ms) Vo2 (Volts) Time (ms) Result: Thus the monostable multivibrator is designed and constructed using transistor and its output waveform is plotted. 36

- 37. Expt. No.12 BISTABLE MULTIVIBRATOR Aim: To design a bistable multivibrator and to plot its output waveform. Components / Equipments Required: Sl. No. Item name Range / Specification Quantity 1 Transistor BC107 2 2 Resistors 4.9K, 1.6M 2 each 3 Capacitors 0.45nF 2 4 CRO (0-20M)Hz 1 5 Power Supply (0-30)V 1 6 Connecting Wires Accordingly Circuit Diagram: VCC = +10V RC RC Pulse Trigger 5.9K (VT < VCC) 5.9K D1 1N4007 1N4007 D2 C 50pF C 50pF R1 10K R1 10K Vo1 Vo2 C C B B BC107 BC107 E E R2 R2 1.8M 1.8M VBB=-2V 0 37

- 38. Theory: The bistable multivibrator has two stable states. The multivibrator can exist indefinitely in either of the twostable states. It requires an external trigger pulse to change from one stable state to another. The circuit remains in one stable state until an external trigger pulse is applied. The bistable multivibrator is used for the performance of many digital operations such as counting and storing of binary information. The multivibrator also finds an applications in generation and pulse type waveform. Design: VCC =12V; VBB = -12V; IC = 2mA; VCE (sat) = 0.2V; VBE (sat) = 0.7V VCC - VCE (sat) 12 – 0.2 RC = = = 5.9K IC 0.002 R2 hfe RC = 315 * 5.9 * 103 = 1.85M R2 = 1.8M Let R1 = 10K, C1 = C2 = 50pF Procedure: 1. Connections are made as per the circuit diagram. 2. Set the input trigger using trigger pulse generator. 3. Note the output waveform from CRO and plot the graph. Tabular Column: Input Width Input Output Voltage (ms) TON TOFF Voltage TON TOFF Voltage (Volts) (ms) (ms) (Volts) (ms) (ms) (Volts) 38

- 39. Model Graph: Vo1 (Volts) Time (ms) Vo2 (Volts) Time (ms) Result: Thus bistable multivibrator has been constructed and its output waveforms are studied. 39

- 40. Expt. No. 13 WAVE SHAPING CIRCUITS (Differentiator, Integrator, Clipper and Clamper) Aim: To design and implement different wave shaping circuits (Differentiator, Integrator, Clipper and Clamper). Components / Equipments Required: Range / Sl. No. Components / Equipment Quantity Specifications 1 Function / Pulse generator (0 – 3M)Hz 1 2 CRO (0-20M)Hz 1 3 Resistor 1K / 100K 1 4 Capacitor 0.1F 1 5 Connecting wires Accordingly Circuit Diagram: (i) Differentiator: C 0.1uF Vin=5V R f= 1KHz 1K / CRO 100K 0 (ii) Integrator: R 1K / 100K Vin=5V f= 1KHz C 0.1uF CRO 0 40

- 41. (iii) Clipper: (a) Series Positive Clipper: D 1N4007 CRO Vin=5V R f=1KHz 10K 0 (b) Shunt Positive Clipper: R 10K D Vin=5V f=1KHz 1N4007 CRO 0 (c) Series Negative Clipper: D 1N4007 CRO Vin=5V R f=1KHz 10K 0 (d) Shunt Negative Clipper: R 10K CRO D Vin=5V f=1KHz 1N4007 0 41

- 42. (e) Positive Biased Series Positive Clipper: D 1N4007 R 10K CRO Vin=5V f=1KHz VB 2V 0 (f) Positive Biased Shunt Positive Clipper: R 10K 1N4007 D Vin=5V CRO f=1KHz VB 2V 0 (g) Positive Biased Series Negative Clipper: D 1N4007 R 10K CRO Vin=5V f=1KHz VB 2V 0 42

- 43. (h) Positive Biased Shunt Negative Clipper: R 10K 1N4007 D Vin=5V CRO f=1KHz VB 2V 0 (i) Negative Biased Series Positive Clipper: D 1N4007 R 10K CRO Vin=5V f=1KHz VB 2V 0 (j) Negative Biased Shunt Positive Clipper: R 10K D 1N4007 Vin=5V CRO f=1KHz VB 2V 0 43

- 44. (k) Negative Biased Series Negative Clipper: D 1N4007 R 10K CRO Vin=5V f=1KHz VB 2V 0 (l) Negative Biased Shunt Negative Clipper: R 10K D 1N4007 Vin=5V CRO f=1KHz VB 2V 0 (m) Combinational Clipper R 10K D D 1N4007 1N4007 Vin=5V CRO f=1KHz VB VB 2V 2V 0 44

- 45. (iv) Clamper: (a) Positive Clamper: C 0.1uF R CRO Vin=5V D 1N4007 10K f=1KHz 0 (b) Negative Clamper: C 0.1uF D R CRO Vin=5V 1N4007 10K f=1KHz 0 Theory: (i) Differentiator: The high pass RC network acts as a differentiator whose output voltage depends upon the differential of input voltage. Its output voltage of the differentiator can be expressed as, d Vout = Vin dt 45

- 46. (ii) Integrator: The low pass RC network acts as an integrator whose output voltage depends upon the integration of input voltage. Its output voltage of the integrator can be expressed as, Vout = Vin dt (iii) Clipper: This circuit is basically a rectifier circuit, which clips the input waveform according to the required specification. The diode acts as a clipper. There are several clippers like positive clipper, negative clipper, etc. Depending upon the connection of diode it can be classified as series and shunt. (iv) Clamper: The clamper circuit is a type of wave shaping circuit in which the DC level of the input signal is altered. The DC voltage is varied accordingly and it is classified as positive clamper or negative clamper accordingly. Design: (i) Differentiator: f = 1KHz = RC = 1ms If C = 0.1F Then R = 10K For T << , Choose R = 1K and For T >> , Choose R = 100K (ii) Integrator: f = 1KHz = RC = 1ms If C = 0.1F Then R = 10K For T << , Choose R = 1K and For T >> , Choose R = 100K Procedure: 1. Connect the circuit as per the circuit diagram. 2. Set Vin = 5V and f = 1KHz. 3. Observe the Output waveform and plot the graph. 46

- 47. Model Graph: (i) Differentiator Vin (Volts) Time (ms) Vout (Volts) Time (ms) Time (ms) (ii) Integrator Vin (Volts) Time (ms) Vout (Volts) Time (ms) Time (ms) 47

- 48. (iii) Clipper: Vin (Volts) Time (ms) Vout (Volts) Series Positive Clipper Time (ms) Shunt Positive Clipper Time (ms) Series Negative Clipper Time (ms) Shunt Negative Clipper Time (ms) Positive Biased Series Positive Clipper 2V Time (ms) 48

- 49. Positive Biased Shunt Positive Clipper 2V Time (ms) Positive Biased Series Negative Clipper 2V Time (ms) Positive Biased Shunt Negative Clipper 2V Time (ms) Negative Biased Series Positive Clipper Time (ms) -2V Negative Biased Shunt Positive Clipper Time (ms) -2V Negative Biased Series Negative Clipper Time (ms) -2V 49

- 50. Negative Biased Shunt Negative Clipper Time (ms) -2V Combinational Clipper 2V Time (ms) -2V (iv) Clamper: Positive Clamper: Time (ms) Negative Clamper: Time (ms) Result: Thus different wave shaping circuits are studied and their output waveforms are plotted. 50

- 51. EXPT NO.14 DIGITAL TO ANALOG CONVERTER (R – 2R LADDER TYPE) Aim: To construct a 8 – bit digital to analog converter using R – 2R ladder type. Circuit Diagram: 20K V+ 10K 10K 10K 7 4 - 1 2 3 6 VOUT LM741 5 + 20K 20K 20K 20K 8 V- 0 0 0 0 0 9 -10V Theory: A DAC accepts an n – bit input word b1, b2, ……, bn in binary and produces an analog signal that is proportional to the input. In this type of DAC, reference voltage is applied to one switch and the other switches are grounded. It is easier to build and number of bits can be expanded by adding more R – 2R sections. The circuit slow down due to stray capacitance. Observation: Output Voltage d1 (MSB) d2 d3 (LSB) VO (Volts) 0 0 0 0 0 0 1 1.25 0 1 0 2.5 0 1 1 3.75 1 0 0 5 1 0 1 6.25 1 1 0 7.5 1 1 1 8.75 51

- 52. Calculation: Output Voltage, VO = VR (d12-1 + d22-2 + d32-3 ) For 100, VO = 5V Output: VO = 5V Model Graph: Voltage 5V time Result: Thus R – 2R ladder type digital to analog converter is implemented. 52

- 53. EXPT NO.15 ASTABLE MULTIVIBRATOR Aim: To plot the transient response of voltages at collector terminals of the two transistors Q1 and Q2. Initial node voltages at collector and base are zero. Circuit Diagram: VCC = +10V 5 R2 R1 R3 R4 4.9K 850K 850K 4.9K C1 C2 2 4 3 1 Vo1 Vo2 0.9nF 0.9nF C C B Q2 Q1 B BC107 BC107 E E 0 Theory: It has two quasi stable states. The transition between the two states occurs automatically due to charging and discharging of the capacitors and not due to any external trigger. Thus none of the transistor is allowed to remain in ON or OFF state. Design: VCC = 10V; IC = 2mA; VCE = 0.2V; C = 0.9nF VCC – VCE (sat) 10 – 0.2 RC = = = 4.9K IC 0.002 R hfe RC = 850K 53

- 54. T = 1.38 R C T = 1ms C = T / (1.38R) = 0.9nF Model Graph: Voltage V01 Time (ms) 0 0.5 1 1.5 V02 Time (ms) 0 0.5 1 1.5 Result: Thus astable multivibrator is designed and transient response is plotted. 54

- 55. EXPT NO. 16 MONOSTABLE MULTIVIBRATOR Aim: To plot the transient response of voltages at collector terminals of Q1 and Q2. Initial voltages of base and collector of Q1 transistor is zero. Circuit Diagram: VCC = +12V 5 R4 5.9K R2 R3 5.9K 452K 10K R5 Vo1 C1 D1 7 2 C2 3 1 4 1N4007 3.2nF Vo2 25nF C C B Q2 Q1 B BC107 BC107 E E R1 100K 6 VBB = -2V 0 Theory: Monostable multivibrator has two states which are (i) quasi-stable state and (ii) stable state. When a trigger input is given to the monostable multivibrator, it switches between two states. It has resistor coupling with one transistor. The other transistor has capacitive coupling. The capacitor is used to increase the speed of switching. The resistor R2 is used to provide negative voltage to the base so that Q1 is OFF and Q2 is ON. Thus an output square wave is obtained from monostable multivibrator. 55

- 56. Model Graph: Vo1 (Volts) Time (ms) Vo2 (Volts) Time (ms) Result: Thus monostable multivibrator is designed and transient response is plotted. 56

- 57. 13. WEIN BRIDGE OSCILLATOR AIM: To study and calculate frequency of. Wein Bridge Oscillator. APPARATUS: Transistor (BC 107) 2 No Resistors 10K 4 No 1 K 3 No 2.2 K 2 No 33 K 6.8 K Capacitors 10 F 2 No 100 F 0.01 F 2 No RPS (0 – 30 V) Potentiometer Bread Boar CRO Connecting wires CIRCUITDIAGRAM: THEORY: 57

- 58. The wein bridge oscillator is a standard circuit for generating low frequencies in the range of 10 Hz to about 1MHz.The method used for getting +ve feedback in wein bridge oscillator is to use two stages of an RC-coupled amplifier. Since one stage of the RC-coupled amplifier introduces a phase shift of 180 deg, two stages will introduces a phase shift of 360 deg. At the frequency of oscillations f the +ve feedback network shown in fig makes the input & output in the phase. The frequency of oscillations is given as f =1/2π√R1C1R2C2 In addition to the positive feedback PROCEDURE: 1. Connections are made as per the circuit diagram 2. Feed the output of the oscillator to a C.R.O by making adjustments in the Potentiometer connected in the +ve feedback loop, try to obtain a stable sine Wave. 3. Measure the time period of the waveform obtained on CRO. & calculate the Frequency of oscillations. 4. Repeat the procedure for different values of capacitance. OBSERVATION: Given R=10kΩ, C=0.01μF fT = 1/ 2RC 1 fP = = T Amplitude,V0 = MODEL WAVE FORM: 58

- 59. RESULT: The frequency of the wein bridge oscillator is calculated and is verified VIVA QUESTIONS: 1. Give the formula for frequency of oscillations? 2. What is the condition for wien bridge oscillator to generate oscillations? 3. What is the total phase shift provided by the oscillator? 4. What is the function of lead-lag network in Wein bridge oscillator? 5. which type of feedback is used in Wein bridge oscillator 6. What is gain of Wein bridge oscillator? 7. what are the application of Wein bridge oscillator 8. What is the condition for oscillations? 9. What is the difference between damped oscillations undamped Oscillations? Wein bridge oscillator is either LC or RC oscillator. 59