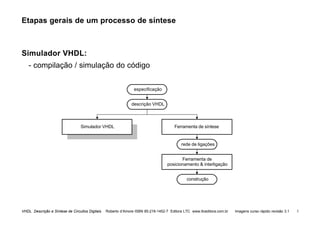

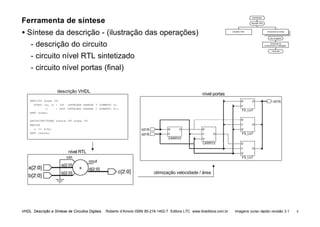

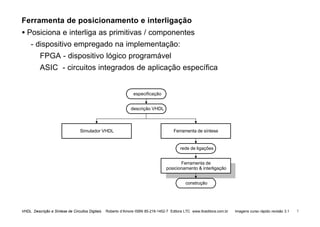

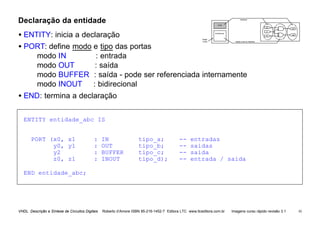

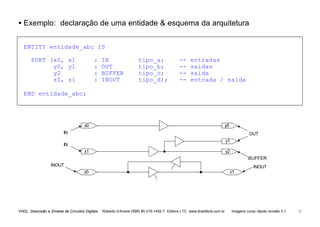

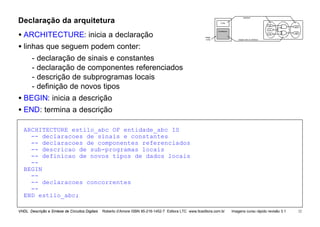

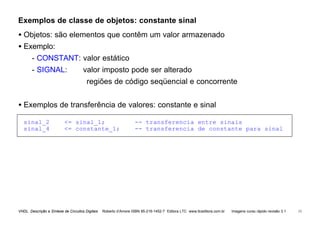

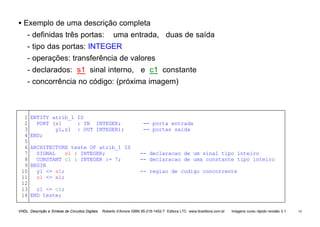

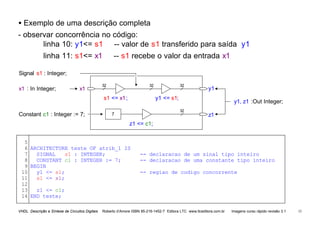

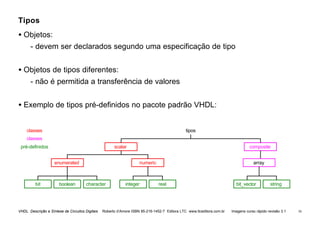

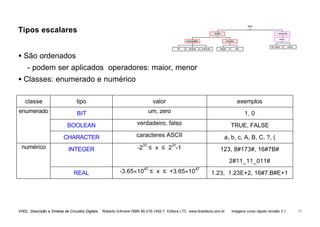

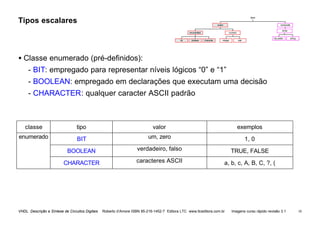

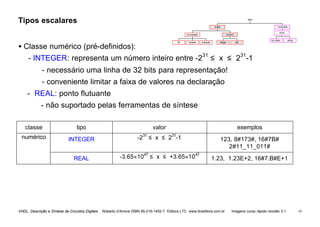

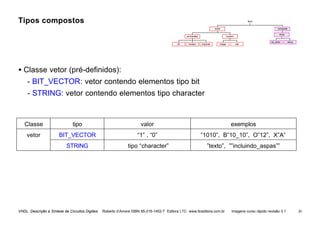

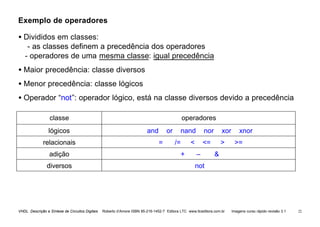

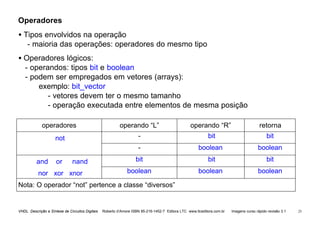

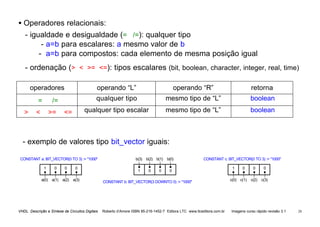

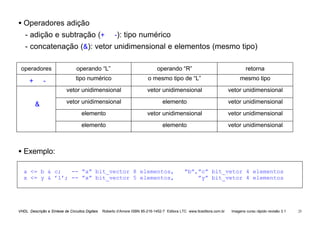

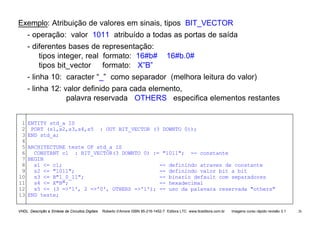

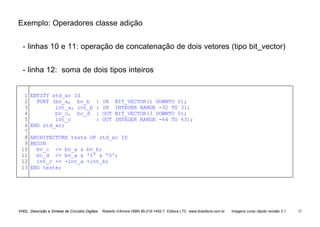

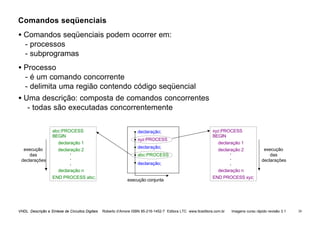

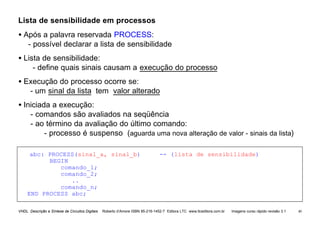

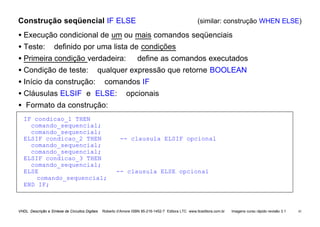

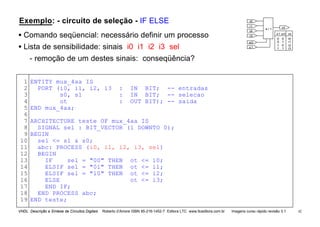

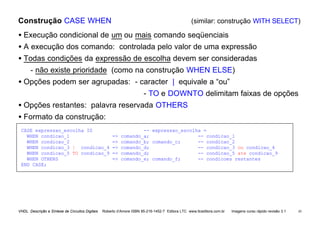

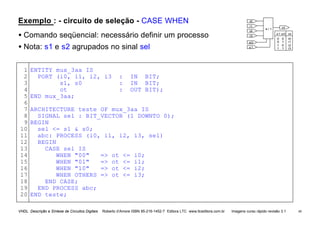

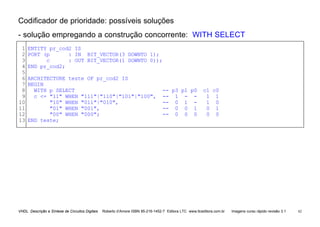

O documento descreve um livro sobre VHDL que inclui tópicos como aspectos gerais da linguagem VHDL, síntese de circuitos, entidade de projeto, classes de objetos, tipos, operadores e construções concorrentes e sequenciais para descrição de circuitos digitais.