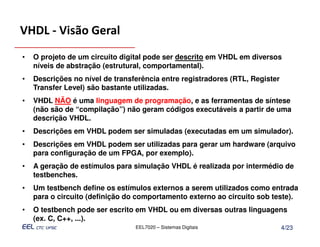

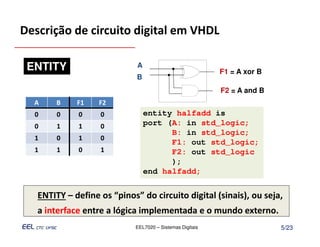

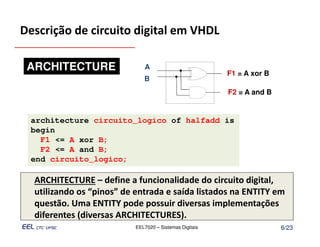

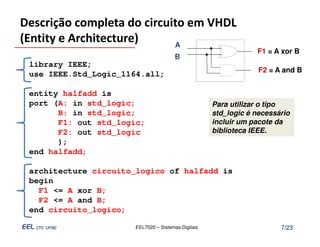

1) O documento apresenta um plano de aula sobre sistemas digitais com a linguagem VHDL.

2) Inclui uma visão geral de VHDL, exemplo de descrição, ferramentas de desenvolvimento e um estudo de caso a ser realizado.

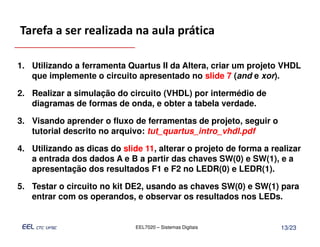

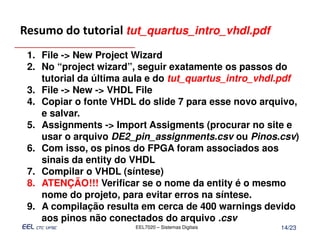

3) Na aula prática, os alunos irão implementar um circuito lógico em VHDL usando a ferramenta Quartus II, simular e testar o circuito na placa DE2.

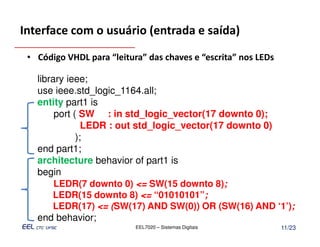

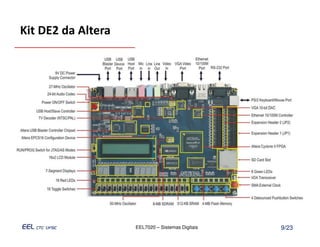

![Interface com o usuário (entrada e saída)

• Placa DE2 possui 18 LEDs vermelhos denominados LEDR17-0 e

18 chaves denominadas SW17-0

• As conexões entre esses componentes e os pinos do FPGA da

placa estão definidas no arquivo DE2_pin_assignments.csv

• São utilizados “vetores” para facilitar o acesso aos LEDs e

chaves da placa

• Exemplo: SW[0] é o elemento 0 do vetor SW, e está conectado

ao pino PIN_N25 do FPGA

• No código em VHDL, usar sempre os nomes definidos no

arquivo DE2_pin_assignments.csv (ver Pinos.csv no site da disciplina)

EEL7020 – Sistemas Digitais 10/23](https://image.slidesharecdn.com/lab2vhdlfluxoquartus-121212050446-phpapp02/85/Lab2-vhdl-fluxo_quartus-10-320.jpg)