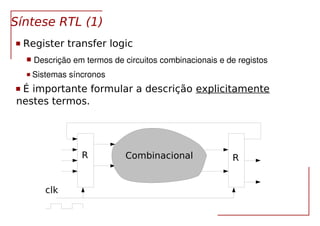

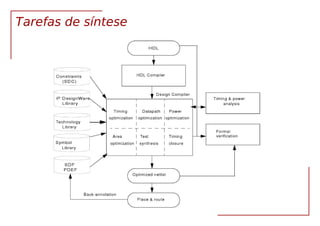

O documento descreve o processo de síntese RTL, incluindo a tradução de HDL para uma representação interna, otimização genérica e lógica, e mapeamento para uma biblioteca-alvo. O sistema Design Compiler é discutido como um exemplo de ferramenta de síntese que realiza estas etapas para gerar um circuito otimizado a nível de portas lógicas.

![VLSI Síntese RTL 7

Síntese RTL (2)

[Tradução] HDL → representação interna do fluxo de dados

e do sequenciamento (controlo)

[Optimização genérica] Processamento:

expansão de funções

propagação de constantes

desdobramento de ciclos

[Optimização lógica] Síntese lógica

Optimização dos circuitos combinacionais](https://image.slidesharecdn.com/synhelp-150610173101-lva1-app6891/85/Logic-Synthesys-help-7-320.jpg)

![VLSI Síntese RTL 16

Resumo das etapas de síntese

Preparação da descrição do circuito (HDL/VHDL)

[Síntese] Tradução para componentes sintéticos

(DesignWare) e para tecnologia genérica (GTECH)

GTECH: portas lógicas e flipflops

DesignWare: somadores, comparadores, ...

Optimização e mapeamento para biblioteca-alvo

processo orientado por restrições

Síntese de infra-estrutura de teste (scan)

Re-síntese após síntese física](https://image.slidesharecdn.com/synhelp-150610173101-lva1-app6891/85/Logic-Synthesys-help-16-320.jpg)

![VLSI Síntese RTL 22

Exemplo MD4: .synopsys_dc.setup

• set datadir "/home/cdsmgr/cad/libs/amis/ads2002.4/cmos035/v1.9"

• lappend search_path $datadir/syn99.10 $datadir/syn99.10/3.3V

• set link_library {MTC45000_WL_TYP.db MTC45000.db MTC45005.db

MTC45100.db}

• set target_library $link_library

• set symbol_library { MTC45000.db MTC45005.sdb }

• set link_library [linsert $link_library 0 "*" ]](https://image.slidesharecdn.com/synhelp-150610173101-lva1-app6891/85/Logic-Synthesys-help-22-320.jpg)

![VLSI Síntese RTL 25

Especificação do “ambiente eléctrico”

set OPERATING_CONDITIONS "WCCOM"

set REF_LOAD "MTC45000/ND2/A"

set OUTPUT_LOAD [ expr 1.2 * [load_of $REF_LOAD] ]

set_load $OUTPUT_LOAD [all_outputs]

set_operating_conditions $OPERATING_CONDITIONS](https://image.slidesharecdn.com/synhelp-150610173101-lva1-app6891/85/Logic-Synthesys-help-25-320.jpg)

![VLSI Síntese RTL 26

Definição de “regras de projecto”

set DEFAULT_MAX_TRANSITION 2

set REF_LOAD "MTC45000/ND2/A"

# maximum load for the input pin

set_max_capacitance [ expr 316 * [ load_of $REF_LOAD ] ] $CLOCK_NAME

set CAP_LOAD [ expr 80 * [load_of $REF_LOAD] ]

set_max_capacitance $CAP_LOAD ctrl[0]

# for all nets of design

set_max_transition $DEFAULT_MAX_TRANSITION [find design "*"]](https://image.slidesharecdn.com/synhelp-150610173101-lva1-app6891/85/Logic-Synthesys-help-26-320.jpg)

![VLSI Síntese RTL 27

Mais conceitos...

Tempo de transição: tempo necessário para “driver”

mudar de estado.

Cada pino de entrada pode ter associado o valor

máximo da sua “carga” [max_capacitance]

As unidades estão definidas nas bibliotecas (usar o

comando report_libs)](https://image.slidesharecdn.com/synhelp-150610173101-lva1-app6891/85/Logic-Synthesys-help-27-320.jpg)

![VLSI Síntese RTL 28

Restrições de optimização

create_clock $CLOCK_NAME -period $CLOCK_PERIOD

# define maximum allowed clock skew

set_propagated_clock $CLOCK_NAME

set_clock_uncertainty 0.1 $CLOCK_NAME

# input timing parameters

set_input_delay $DEFAULT_INPUT_DELAY -clock $CLOCK_NAME [all_inputs]

# remove input delay attribute for clock:

remove_input_delay $CLOCK_NAME -clock $CLOCK_NAME](https://image.slidesharecdn.com/synhelp-150610173101-lva1-app6891/85/Logic-Synthesys-help-28-320.jpg)