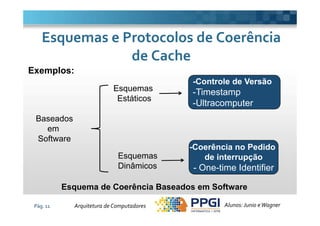

O documento discute o problema da coerência de memória cache em sistemas multiprocessados e formas de resolvê-lo. É apresentado o problema da coerência de cache e como ele pode ser resolvido através de esquemas baseados em software ou hardware. Protocolos comuns como snoopy e directory são explicados.

![Coerência:

Qualidade, estado ou atitude de coerente [Aurélio]

Coerência de Cache:

É garantir qualquer processador sempre receba o dado

IntroduçãoIntrodução

Pág. 3

É garantir qualquer processador sempre receba o dado

mais atual contido em qualquer cache para um mesmo

endereço.

Alunos: Junio eWagnerArquitetura de Computadores](https://image.slidesharecdn.com/coerncia-memoria-130714223908-phpapp02/85/Coera-ncia-memoria-3-320.jpg)

![Problemas de coerência de cache aparecem mais

comumente em sistemas que possuem mais de um

processador. [1]

Apresentação do ProblemaApresentação do Problema

Pág. 4 Alunos: Junio eWagnerArquitetura de Computadores](https://image.slidesharecdn.com/coerncia-memoria-130714223908-phpapp02/85/Coera-ncia-memoria-4-320.jpg)

![Controle Versão (Estáticas)

Cada nova escrita de um dado compartilhado gera uma

nova versão de conteúdo. Os processadores incrementam o

novo número a cada escrita que ocorra.[2]

Esquemas e Protocolos de CoerênciaEsquemas e Protocolos de Coerência

de Cachede Cache

Pág. 12

novo número a cada escrita que ocorra.[2]

Para todo acesso ao dado compartilhado, os números da

cache e o corrente processador são comparados.[3]

Caso a versão do processador seja maior que o da versão

na cache. O processador esta trabalhando com o Dado

corrento.[1]

Alunos: Junio e WagnerArquitetura de Computadores](https://image.slidesharecdn.com/coerncia-memoria-130714223908-phpapp02/85/Coera-ncia-memoria-12-320.jpg)

![Coerência no Pedido de Interrupção (Dinâmicas)

Solução que utiliza a mesma idéia de memória virtual.

Esquemas e Protocolos de CoerênciaEsquemas e Protocolos de Coerência

de Cachede Cache

Pág. 13

Ao se detectar um page fault, o hardware interrompe a

execução chamando o sistema operacional para fazer o

tratamento adequado.[3]

Alunos: Junio eWagnerArquitetura de Computadores](https://image.slidesharecdn.com/coerncia-memoria-130714223908-phpapp02/85/Coera-ncia-memoria-13-320.jpg)

![Protocolos de Coerência Baseados em Hardware:

Utilizados principalmente em sistemas multiprocessadores

.

Tais protocolos lidam com a coerência em tempo de

Esquemas e Protocolos de CoerênciaEsquemas e Protocolos de Coerência

de Cachede Cache

Pág. 14

Tais protocolos lidam com a coerência em tempo de

execução, sendo assim considerados dinâmicos. [2]

São mais complexos de implementar, pois são

caracterizados pelo uso de recursos de baixo nível de

arquitetura.[1]

São Classificados em Snoopy e Directory

Alunos: Junio eWagnerArquitetura de Computadores](https://image.slidesharecdn.com/coerncia-memoria-130714223908-phpapp02/85/Coera-ncia-memoria-14-320.jpg)

![Protocolos de Coerência Baseados em Hardware:

Protocolo Snoopy: (Protocolo de Monitoramento)[4]

Responsabilidade de manter a coerência entre todos os caches;

Esquemas e Protocolos de CoerênciaEsquemas e Protocolos de Coerência

de Cachede Cache

Pág. 15

Responsabilidade de manter a coerência entre todos os caches;

Protocolo Singles Bus

Utiliza duas Política:

Write-Invalidade;

Write-update;

Alunos: Junio eWagnerArquitetura de Computadores](https://image.slidesharecdn.com/coerncia-memoria-130714223908-phpapp02/85/Coera-ncia-memoria-15-320.jpg)