High performance nb-ldpc decoder with reduction of message exchange

•Transferir como DOCX, PDF•

0 gostou•4,974 visualizações

High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange High performance nb-ldpc decoder with reduction of message exchange

Denunciar

Compartilhar

Denunciar

Compartilhar

Recomendados

Recomendados

Mais conteúdo relacionado

Mais procurados

Mais procurados (20)

Iaetsd pipelined parallel fft architecture through folding transformation

Iaetsd pipelined parallel fft architecture through folding transformation

Transpose Form Fir Filter Design for Fixed and Reconfigurable Coefficients

Transpose Form Fir Filter Design for Fixed and Reconfigurable Coefficients

Iaetsd vlsi architecture for exploiting carry save arithmetic using verilog hdl

Iaetsd vlsi architecture for exploiting carry save arithmetic using verilog hdl

Performance Analysis of OFDM Transceiver with Folded FFT and LMS Filter

Performance Analysis of OFDM Transceiver with Folded FFT and LMS Filter

A novel area efficient vlsi architecture for recursion computation in lte tur...

A novel area efficient vlsi architecture for recursion computation in lte tur...

Design and Implementation of Low-Power and Area-Efficient 64 bit CSLA using VHDL

Design and Implementation of Low-Power and Area-Efficient 64 bit CSLA using VHDL

Modified montgomery modular multiplier for cryptosystems

Modified montgomery modular multiplier for cryptosystems

IJERD (www.ijerd.com) International Journal of Engineering Research and Devel...

IJERD (www.ijerd.com) International Journal of Engineering Research and Devel...

HIGH SPEED MULTIPLE VALUED LOGIC FULL ADDER USING CARBON NANO TUBE FIELD EFFE...

HIGH SPEED MULTIPLE VALUED LOGIC FULL ADDER USING CARBON NANO TUBE FIELD EFFE...

International Journal of Engineering Research and Development (IJERD)

International Journal of Engineering Research and Development (IJERD)

IRJET- Low Complexity Pipelined FFT Design for High Throughput and Low Densit...

IRJET- Low Complexity Pipelined FFT Design for High Throughput and Low Densit...

Semelhante a High performance nb-ldpc decoder with reduction of message exchange

In this paper, low linear architectures for analyzing the first two maximum or minimum values are of paramount importance in several uses, including iterative decoders. The min-sum giving out step is to that it produces only two diverse output magnitude values irrespective of the number of incoming bit-to check communication. These new micro-architecture structures would utilize the minimum number of comparators by exploiting the concept of survivors in the search. These would result in reduced number of comparisons and consequently reduced energy use. Multipliers are complex units and play an important role in finding the overall area, speed and power consumption of digital designs. By using the multiplier we can minimize the parameters like latency, complexity and power consumption. The decoding algorithms we propose generalize and unify the decoding schemes originally presented the product codes and those of low-density parity-check codes.Reduced Complexity Maximum Likelihood Decoding Algorithm for LDPC Code Correc...

Reduced Complexity Maximum Likelihood Decoding Algorithm for LDPC Code Correc...Associate Professor in VSB Coimbatore

Semelhante a High performance nb-ldpc decoder with reduction of message exchange (20)

Reduced Energy Min-Max Decoding Algorithm for Ldpc Code with Adder Correction...

Reduced Energy Min-Max Decoding Algorithm for Ldpc Code with Adder Correction...

PERFORMANCE COMPARISON DCM VERSUS QPSK FOR HIGH DATA RATES IN THE MBOFDM UWB ...

PERFORMANCE COMPARISON DCM VERSUS QPSK FOR HIGH DATA RATES IN THE MBOFDM UWB ...

Reduced Complexity Maximum Likelihood Decoding Algorithm for LDPC Code Correc...

Reduced Complexity Maximum Likelihood Decoding Algorithm for LDPC Code Correc...

Implementation of High Speed OFDM Transceiver using FPGA

Implementation of High Speed OFDM Transceiver using FPGA

Analysis of Women Harassment inVillages Using CETD Matrix Modal

Analysis of Women Harassment inVillages Using CETD Matrix Modal

One minimum only trellis decoder for non binary low-density parity-check codes

One minimum only trellis decoder for non binary low-density parity-check codes

DESIGN OF DELAY COMPUTATION METHOD FOR CYCLOTOMIC FAST FOURIER TRANSFORM

DESIGN OF DELAY COMPUTATION METHOD FOR CYCLOTOMIC FAST FOURIER TRANSFORM

BER Performance Improvement for 4 X 4 MIMO Single Carrier FDMA System Using M...

BER Performance Improvement for 4 X 4 MIMO Single Carrier FDMA System Using M...

IRJET- The RTL Model of a Reconfigurable Pipelined MCM

IRJET- The RTL Model of a Reconfigurable Pipelined MCM

Improving The Performance of Viterbi Decoder using Window System

Improving The Performance of Viterbi Decoder using Window System

Ternary content addressable memory for longest prefix matching based on rando...

Ternary content addressable memory for longest prefix matching based on rando...

Hardware Architecture of Complex K-best MIMO Decoder

Hardware Architecture of Complex K-best MIMO Decoder

International Journal of Engineering Research and Development

International Journal of Engineering Research and Development

Design and Implementation of an Embedded System for Software Defined Radio

Design and Implementation of an Embedded System for Software Defined Radio

Último

Falcon stands out as a top-tier P2P Invoice Discounting platform in India, bridging esteemed blue-chip companies and eager investors. Our goal is to transform the investment landscape in India by establishing a comprehensive destination for borrowers and investors with diverse profiles and needs, all while minimizing risk. What sets Falcon apart is the elimination of intermediaries such as commercial banks and depository institutions, allowing investors to enjoy higher yields.Unveiling Falcon Invoice Discounting: Leading the Way as India's Premier Bill...

Unveiling Falcon Invoice Discounting: Leading the Way as India's Premier Bill...Falcon Invoice Discounting

Falcon stands out as a top-tier P2P Invoice Discounting platform in India, bridging esteemed blue-chip companies and eager investors. Our goal is to transform the investment landscape in India by establishing a comprehensive destination for borrowers and investors with diverse profiles and needs, all while minimizing risk. What sets Falcon apart is the elimination of intermediaries such as commercial banks and depository institutions, allowing investors to enjoy higher yields.Falcon Invoice Discounting: The best investment platform in india for investors

Falcon Invoice Discounting: The best investment platform in india for investorsFalcon Invoice Discounting

Último (20)

Chennai Call Gril 80022//12248 Only For Sex And High Profile Best Gril Sex Av...

Chennai Call Gril 80022//12248 Only For Sex And High Profile Best Gril Sex Av...

Challenges and Opportunities: A Qualitative Study on Tax Compliance in Pakistan

Challenges and Opportunities: A Qualitative Study on Tax Compliance in Pakistan

The Abortion pills for sale in Qatar@Doha [+27737758557] []Deira Dubai Kuwait![The Abortion pills for sale in Qatar@Doha [+27737758557] []Deira Dubai Kuwait](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![The Abortion pills for sale in Qatar@Doha [+27737758557] []Deira Dubai Kuwait](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

The Abortion pills for sale in Qatar@Doha [+27737758557] []Deira Dubai Kuwait

Berhampur 70918*19311 CALL GIRLS IN ESCORT SERVICE WE ARE PROVIDING

Berhampur 70918*19311 CALL GIRLS IN ESCORT SERVICE WE ARE PROVIDING

Unveiling Falcon Invoice Discounting: Leading the Way as India's Premier Bill...

Unveiling Falcon Invoice Discounting: Leading the Way as India's Premier Bill...

Pre Engineered Building Manufacturers Hyderabad.pptx

Pre Engineered Building Manufacturers Hyderabad.pptx

Jual Obat Aborsi ( Asli No.1 ) 085657271886 Obat Penggugur Kandungan Cytotec

Jual Obat Aborsi ( Asli No.1 ) 085657271886 Obat Penggugur Kandungan Cytotec

Ooty Call Gril 80022//12248 Only For Sex And High Profile Best Gril Sex Avail...

Ooty Call Gril 80022//12248 Only For Sex And High Profile Best Gril Sex Avail...

Falcon Invoice Discounting: The best investment platform in india for investors

Falcon Invoice Discounting: The best investment platform in india for investors

Paradip CALL GIRL❤7091819311❤CALL GIRLS IN ESCORT SERVICE WE ARE PROVIDING

Paradip CALL GIRL❤7091819311❤CALL GIRLS IN ESCORT SERVICE WE ARE PROVIDING

Berhampur 70918*19311 CALL GIRLS IN ESCORT SERVICE WE ARE PROVIDING

Berhampur 70918*19311 CALL GIRLS IN ESCORT SERVICE WE ARE PROVIDING

Falcon Invoice Discounting: Unlock Your Business Potential

Falcon Invoice Discounting: Unlock Your Business Potential

Uneak White's Personal Brand Exploration Presentation

Uneak White's Personal Brand Exploration Presentation

Horngren’s Cost Accounting A Managerial Emphasis, Canadian 9th edition soluti...

Horngren’s Cost Accounting A Managerial Emphasis, Canadian 9th edition soluti...

High performance nb-ldpc decoder with reduction of message exchange

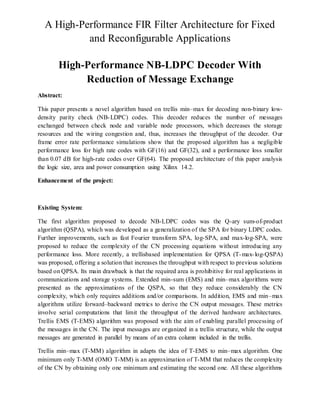

- 1. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications High-Performance NB-LDPC Decoder With Reduction of Message Exchange Abstract: This paper presents a novel algorithm based on trellis min–max for decoding non-binary low- density parity check (NB-LDPC) codes. This decoder reduces the number of messages exchanged between check node and variable node processors, which decreases the storage resources and the wiring congestion and, thus, increases the throughput of the decoder. Our frame error rate performance simulations show that the proposed algorithm has a negligible performance loss for high rate codes with GF(16) and GF(32), and a performance loss smaller than 0.07 dB for high-rate codes over GF(64). The proposed architecture of this paper analysis the logic size, area and power consumption using Xilinx 14.2. Enhancement of the project: Existing System: The first algorithm proposed to decode NB-LDPC codes was the Q-ary sum-of-product algorithm (QSPA), which was developed as a generalization of the SPA for binary LDPC codes. Further improvements, such as fast Fourier transform SPA, log-SPA, and max-log-SPA, were proposed to reduce the complexity of the CN processing equations without introducing any performance loss. More recently, a trellisbased implementation for QPSA (T-max-log-QSPA) was proposed, offering a solution that increases the throughput with respect to previous solutions based on QPSA. Its main drawback is that the required area is prohibitive for real applications in communications and storage systems. Extended min-sum (EMS) and min–max algorithms were presented as the approximations of the QSPA, so that they reduce considerably the CN complexity, which only requires additions and/or comparisons. In addition, EMS and min–max algorithms utilize forward–backward metrics to derive the CN output messages. These metrics involve serial computations that limit the throughput of the derived hardware architectures. Trellis EMS (T-EMS) algorithm was proposed with the aim of enabling parallel processing of the messages in the CN. The input messages are organized in a trellis structure, while the output messages are generated in parallel by means of an extra column included in the trellis. Trellis min–max (T-MM) algorithm in adapts the idea of T-EMS to min–max algorithm. One minimum only T-MM (OMO T-MM) is an approximation of T-MM that reduces the complexity of the CN by obtaining only one minimum and estimating the second one. All these algorithms

- 2. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications exchange q × dc reliability values between CN and variable node (VN) processors. This amount of exchanged messages is large enough to cause wiring congestion, and this limits the maximum throughput, especially for high-rate NB-LDPC codes and high-order GFs. In addition, in decoder architectures with a layered schedule, the CN output messages are stored to be used in the next iteration. So, the required memory, which is the main part of the area in NB-LDPC decoder architectures, is too high. Disadvantages: Area coverage is high Throughput is low Proposed System: MODIFIED TRELLIS MIN–MAX ALGORITHM: Reformulation of Trellis Min–Max Algorithm: We reformulate the T-MM algorithm as a first step to define our proposal. As can be seen in Algorithm 2, Steps 4 and 5 are the ones reformulated. The function ψ’ in Step 4 obtains, which path in the trellis was used to obtain ΔQ (a), that is, the most reliable path. Considering that a maximum of two deviations is evaluated, the function returns the two GF symbols that define this path, η∗ 1(a) and η∗ 2(a). Algorithm 1 T-MM Algorithm

- 3. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications Fig. 1 includes an example of trellis with GF(4) and dc = 5. It shows the CN input messages before (Qmn(a)) and after (ΔQmn(a)) delta domain transformation. The hard-decision symbols are z = {α1, α0, 0, α0, 0}. After the normal-to-delta domain transformation, the reliabilities ΔQ mn(a) in the first row of the trellis are equal to 0.

- 4. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications Fig. 1. Top: example of CN input messages in normal domain. Bottom: messages in delta domain and organized in trellis way including the extra column Q(a) (bottom size). Example for GF(4) and dc = 5. NB-LDPC DECODER IMPLEMENTATION We describe the architecture designed to implement the proposed mT-MM algorithm. CN Architecture for mT-MM Algorithm The main characteristic of the proposed mT-MM Algorithm is to move part of the complexity of the CN processor to the VN processor. In this way, the number of exchanged messages between them and also the storage resources of the decoder are reduced. Therefore, the CN architecture presented in this section requires less functional blocks than a conventional implementation of the T-MM algorithm. Fig. 2 shows the block diagram for the top-level CN architecture, where each block corresponds to a step in the mT-MM algorithm.

- 5. A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications Fig. 2. Proposed CN block diagram. The complete block diagram for the proposed decoder is presented in Fig. 3. As can be seen, there is only one CN processor and one VN processor, which processes one row of H per clock cycle. A layered schedule requires to store the CN output messages from one iteration to be used in the next one. This is done by means of a shift register with M stages (SR in Fig. 3). Fig. 3. Top-level proposed decoder architecture. Advantages: Improve area and throughput. Software implementation: Modelsim Xilinx ISE