VHDL documento sobre invariantes da linguagem e elementos básicos de projeto

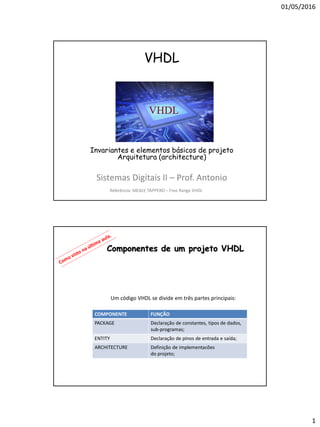

- 1. 01/05/2016 1 VHDL Sistemas Digitais II – Prof. Antonio Invariantes e elementos básicos de projeto Arquitetura (architecture) Referência: MEALY, TAPPERO – Free Range VHDL Componentes de um projeto VHDL COMPONENTE FUNÇÃO PACKAGE Declaração de constantes, tipos de dados, sub-programas; ENTITY Declaração de pinos de entrada e saída; ARCHITECTURE Definição de implementacões do projeto; Um código VHDL se divide em três partes principais:

- 2. 01/05/2016 2 Estrutura típica de um programa VHDL Relembrando: Caixa preta x Caixa branca VISÃO “CAIXA PRETA” VISÃO “CAIXA BRANCA” Entidade do VHDL fornece a visão caixa preta, externa do circuito. Determina quais são as entradas e as saídas Arquitetura do VHDL fornece a visão caixa branca, interna do circuito. Determina como o circuito funciona, o que se liga ao quê etc.

- 3. 01/05/2016 3 “Regras de Ouro” para escrever em VHDL Tenha sempre em mente que: • VHDL é uma linguagem para descrever hardware. Quando você está trabalhando com o VHDL você não está programando e sim projetando um hardware (um circuito). • é necessário ter-se um conceito geral de como o hardware vai ficar quando acabado. VHDL é uma linguagem poderosa mas é necessário ter-se conhecimento de como circuitos digitais básicos são construídos. • Insensível à caixa de texto (alta ou baixa); Ex: Dout <= A and B; doUt <= a AnD b; • Insensível a espaço em branco: Ex: nQ <= In_a or In_b; nQ <= in_a OR in_b; • Comentários: – Começam com o símbolo “--“; – O compilador ignora o que vem depois até o fim da linha. Ex: -- este é um comentário em VHDL • Parêntesis: – Impõem precedência às operações. – Use-os para tornar o seu código mais legível para seres humanos. Ex: if x = '0' and y = '0' or z = '1' then if ( ((x = '0') and (y = '0')) or (z = '1') ) then VHDL: invariantes da linguagem

- 4. 01/05/2016 4 VHDL: Identificadores • Identificadores são os nomes de variáveis, pinos, entidades, arquiteturas etc usados no código VHDL. • Devem ser auto-descritos por seus nomes, provendo informação à respeito de seu uso e propósito. – Ex: CalcPosicaoTerra() ou calc_posicao_terra() – IdadeMeuCarro ou Idade_meu_carro • Podem ser tão longos quanto se queira. Porém, nomes mais curtos facilitam a legibilidade do código. • Só podem conter letras (A-Z e a-z), números (0-9) e o sublinha (_). • Devem iniciar por um letra do alfabeto. • Não devem terminar com um sublinha e não devem ter dois ou mais sublinhas seguidos. Palavras reservadas A lista a seguir apresenta as palavras que têm um significado especial no VHDL. Elas não devem ser utilizadas como identificadores.

- 5. 01/05/2016 5 Exemplos de identificadors válidos Exemplos de identificadores inválidos. Por quê? Começa com um número. Não é auto-explicativo. Caractere inválido. Sublinhas seguidas. Termina com sublinha. Palavra reservada do VHDL Lixo! Vamos ser profissionais!! Feio demais!! Não é auto-explicativo. Caractere inválido. q_merda FFF Lembrete: Só podem conter letras (A-Z e a-z), números (0-9) e o sublinha (_).

- 6. 01/05/2016 6 Exercício: Desenhe o diagrama caixa-preta para a seguinte entidade do código VHDL abaixo: ) Exercício: Escreva o código VHDL para a entidade do seguinte circuito: entity sys2 is port ( input_w : in std_logic; a_data : in std_logic_vector(0 to 7); b_data : in std_logic_vector(0 to 7); clk : in std_logic ; dat_4: out std_logic_vector(0 to 7); dat_5: out std_logic_vector(0 to 2); ); end sys2;

- 7. 01/05/2016 7 Estrutura Básica da Arquitetura Nome da arquitetura Nome da Entidade ARQUITETURA Arquitetura: Visão “caixa branca” do projeto. Define como as entradas são processadas para gerar as saídas do projeto, ou seja, descreve como o circuito realmente funciona. São as “entranhas” expostas do projeto, do que se tem dentro da caixa. Nome da arquitetura Declaração de sinais (representação de sw de um fio) SINTAXE: Declaração de variáveis (usada para armazenar informação, similar ao C. Devem ser declaradas dentro de process e são locais) Nome da entidade !/ Um sinal ou variável devem ser declarados (nome e tipo) antes de serem usados pelo programa)

- 8. 01/05/2016 8 Num circuito real, tudo ocorre ao mesmo tempo, agora! Num circuito real, tudo ocorre simultaneamente. As saídas respondem praticamente instantaneamente aos sinais das entradas. Para ser uma HDL (Linguagem de Descrição de Hardware) o VHDL deve se comportar da mesma maneira. Exercício de Aquecimento a b c d e x y w z PORTAS Compare, analise e tire suas conclusões

- 9. 01/05/2016 9 Operador de Atribuição a b c d e x y w z PORTAS <= Atribui a lógica correspondente ao pino ou sinal Não é linha a linha, é simultâneo! Exemplo: Escreva o código VHDL que implemente uma porta NAND de três entradas. As entradas são nomeadas de A, B e C e o sinal de saída de F. Sempre faça um esquema do que você está querendo obter. MODELO PARA REFERÊNCIA:

- 10. 01/05/2016 10 Solução: Escreva o código VHDL que implemente uma porta NAND de três entradas. As entradas são nomeadas de A, B e C e o sinal de saída de F. Sempre faça um esquema do que você está querendo obter. Exercício: Escreva o código VHDL que implemente a função lógica Qualquer mudança no sinal de qualquer entrada fará com que a saída seja reavaliada. N L M

- 11. 01/05/2016 11 Sinais = fios internos A1 A2 Exercícios Escreva o código VHDL que descreve os seguintes circuitos: