Sequential circuits

- 1. °2/17/2020

- 2. Mahasiswa dapat menjelaskan cara kerja komponen dasar rangkaian Sequential, yaitu Latch dan Flip-flop. °2/17/2020

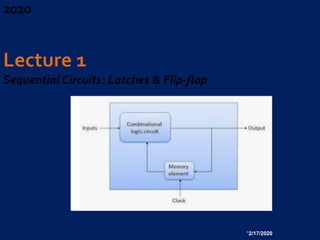

- 4. Circuits require memory to store intermediate data Sequential circuits use a periodic signal to determine when to store values. ◦ A clock signal can determine storage times ◦ Clock signals are periodic Single bit storage element is a flip flop A basic type of flip flop is a latch Latches are made from logic gates ◦ NAND, NOR, AND, OR, Inverter °2/17/2020

- 5. Hasil operasi Rangkaian Logika Kombinasional adalah respon terhadap kombinasi input yang diberikan. Hanya bisa menjumlahkan dua bilangan. Untuk menjumlahkan bilangan ketiga, diperlukan penyimpanan informasi hasil penjumlahan sebelumnya. ▪ Contoh : 2+1 +5 ▪ 2 + 1 = 3 maka 3 disimpan di dalam memory, kemudian : ▪ 3 + 5 = 8 (a sequential operation); To handle this, we need sequential logic capable of storing intermediate (and final) results. °2/17/2020

- 6. °2/17/2020 Combinational circuit Flip Flops OutputsInputs Next state Present state Timing signal (clock) Clock Clock a periodic external event (input) synchronizes when current state changes happen keeps system well-behaved makes it easier to design and build large systems

- 7. °2/17/2020 1 1 1 0 0 1 0 0 S R Q Q’ 0 1 1 0 Set 1 0 Stable 0 1 Reset 0 0 Undefined R (reset) Q Q S (set) ° S-R latch made from cross-coupled NORs ° If Q = 1, set state ° If Q = 0, reset state ° Usually S=0 and R=0 ° S=1 and R=1 generates unpredictable results

- 8. °2/17/2020 S R Q Q’ 0 0 0 1 1 0 1 1 S R Q Q’ 0 1 1 0 Set 1 0 Store 0 1 Reset 1 1 Disallowed ° Latch made from cross-coupled NANDs ° Sometimes called S’-R’ latch ° Usually S=1 and R=1 ° S=0 and R=0 generates unpredictable results

- 9. °2/17/2020 ° Occasionally, desirable to avoid latch changes ° C = 0 disables all latch state changes ° Control signal enables data change when C = 1 ° Right side of circuit same as ordinary S-R latch.

- 10. Latch operation enabled by C Input sampling enabled by gates °2/17/2020 R’ S’ Q’ Q C’ Outputs change when C is low: RESET and SET Otherwise: HOLD Latch is level-sensitive, in regards to C Only stores data if C’ = 0

- 11. °2/17/2020 Q Q’ C D S R X Y X Y C Q Q’ 0 0 1 Q0 Q0’ Store 0 1 1 0 1 Reset 1 0 1 1 0 Set 1 1 1 1 1 Disallowed X X 0 Q0 Q0’ Store 0 1 0 1 1 1 1 0 X 0 Q0 Q0’ D C Q Q’ ° Q0 indicates the previous state (the previously stored value)

- 12. °2/17/2020 Q Q’ C D S R X Y 0 1 0 1 1 1 1 0 X 0 Q0 Q0’ D C Q Q’ ° Input value D is passed to output Q when C is high ° Input value D is ignored when C is low

- 13. °2/17/2020 E x Latches on following edge of clock E D Q C x z z ° Z only changes when E is high ° If E is high, Z will follow X

- 14. °2/17/2020 E x Latches on following edge of clock E D Q C x z z ° The D latch stores data indefinitely, regardless of input D values, if C = 0 ° Forms basic storage element in computers

- 15. °2/17/2020 ° SR latch is based on NOR gates ° S’R’ latch based on NAND gates ° D latch can be based on either. ° D latch sometimes called transparent latch

- 16. Latches are based on combinational gates (e.g. NAND, NOR) Latches store data even after data input has been removed S-R latches operate like cross-coupled inverters with control inputs (S = set, R = reset) With additional gates, an S-R latch can be converted to a D latch (D stands for data) D latch is simple to understand conceptually ◦ When C = 1, data input D stored in latch and output as Q ◦ When C = 0, data input D ignored and previous latch value output at Q °2/17/2020

- 17. Latches respond to trigger levels on control inputs ◦ Example: If G = 1, input reflected at output Difficult to precisely time when to store data with latches Flip flops store data on a rising or falling trigger edge. ◦ Example: control input transitions from 0 -> 1, data input appears at output ◦ Data remains stable in the flip flop until until next rising edge. Different types of flip flops serve different functions Flip flops can be defined with characteristic functions. °2/17/2020

- 18. °2/17/2020 Lo-Hi edgeHi-Lo edge ° What if the output only changed on a C transition? C D Q Q’ 0 0 1 1 1 0 X 0 Q0 Q0’ D C Q Q’ Positive edge triggered

- 19. °2/17/2020 ° Consider two latches combined together ° Only one C value active at a time ° Output changes on falling edge of the clock

- 20. °2/17/2020 D gets latched to Q on the rising edge of the clock. ° Stores a value on the positive edge of C ° Input changes at other times have no effect on output C D Q Q’ 0 0 1 1 1 0 X 0 Q0 Q0’ D C Q Q’ Positive edge triggered

- 21. °2/17/2020 ° Stores a value on the positive edge of C ° Input changes at other times have no effect on output

- 22. Positive Edge-Triggered J-K Flip-Flop 0 0 Q0 Q0’ 0 1 0 1 1 0 1 0 1 1 TOGGLE QJ Q’CLKK°Created from D flop °J sets °K resets °J=K=1 -> invert output °2/17/2020

- 23. °2/17/2020 ° Two data inputs, J and K ° J -> set, K -> reset, if J=K=1 then toggle output Characteristic Table

- 24. 2. Positive Edge-Triggered T Flip-Flop 0 Q0 Q0’ 1 TOGGLE Q Q’CT °Created from D flop °T=0 -> keep current °K resets °T=1 -> invert current °2/17/2020

- 25. °2/17/2020 • J, K are synchronous inputs o Effects on the output are synchronized with the CLK input. • Asynchronous inputs operate independently of the synchronous inputs and clock o Set the FF to 1/0 states at any time.

- 26. °2/17/2020

- 27. °2/17/2020 ° Flip flops store outputs from combinational logic ° Multiple flops can store a collection of data

- 28. Flip flops are powerful storage elements ◦ They can be constructed from gates and latches! D flip flop is simplest and most widely used Asynchronous inputs allow for clearing and presetting the flip flop output Multiple flops allow for data storage ◦ The basis of computer memory! Combine storage and logic to make a computation circuit Next time: Analyzing sequential circuits. °2/17/2020

- 29. Gunakan Multisim untuk merancang rangkaian penyimpan 3 bit data secara paralel. Kemudian data tersebut dihapus Diisi lagi dengan data baru °2/17/2020