CHAPTER 1.pptx

•Transferir como PPTX, PDF•

0 gostou•5 visualizações

sung mo kang vlsi introduction

Denunciar

Compartilhar

Denunciar

Compartilhar

Recomendados

Recomendados

Mais conteúdo relacionado

Semelhante a CHAPTER 1.pptx

Semelhante a CHAPTER 1.pptx (20)

400-101 CCIE Routing and Switching IT Certification

400-101 CCIE Routing and Switching IT Certification

lowpower consumption and details of dfferent power pdf

lowpower consumption and details of dfferent power pdf

Último

Último (20)

HOA1&2 - Module 3 - PREHISTORCI ARCHITECTURE OF KERALA.pptx

HOA1&2 - Module 3 - PREHISTORCI ARCHITECTURE OF KERALA.pptx

S1S2 B.Arch MGU - HOA1&2 Module 3 -Temple Architecture of Kerala.pptx

S1S2 B.Arch MGU - HOA1&2 Module 3 -Temple Architecture of Kerala.pptx

Cara Menggugurkan Sperma Yang Masuk Rahim Biyar Tidak Hamil

Cara Menggugurkan Sperma Yang Masuk Rahim Biyar Tidak Hamil

Design For Accessibility: Getting it right from the start

Design For Accessibility: Getting it right from the start

Bhubaneswar🌹Call Girls Bhubaneswar ❤Komal 9777949614 💟 Full Trusted CALL GIRL...

Bhubaneswar🌹Call Girls Bhubaneswar ❤Komal 9777949614 💟 Full Trusted CALL GIRL...

Orlando’s Arnold Palmer Hospital Layout Strategy-1.pptx

Orlando’s Arnold Palmer Hospital Layout Strategy-1.pptx

XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

Tamil Call Girls Bhayandar WhatsApp +91-9930687706, Best Service

Tamil Call Girls Bhayandar WhatsApp +91-9930687706, Best Service

A CASE STUDY ON CERAMIC INDUSTRY OF BANGLADESH.pptx

A CASE STUDY ON CERAMIC INDUSTRY OF BANGLADESH.pptx

NO1 Top No1 Amil Baba In Azad Kashmir, Kashmir Black Magic Specialist Expert ...

NO1 Top No1 Amil Baba In Azad Kashmir, Kashmir Black Magic Specialist Expert ...

Standard vs Custom Battery Packs - Decoding the Power Play

Standard vs Custom Battery Packs - Decoding the Power Play

Verification of thevenin's theorem for BEEE Lab (1).pptx

Verification of thevenin's theorem for BEEE Lab (1).pptx

CHAPTER 1.pptx

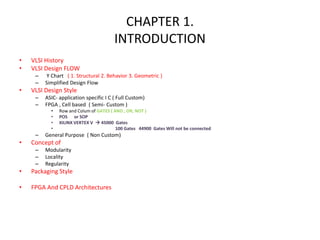

- 1. CHAPTER 1. INTRODUCTION • VLSI History • VLSI Design FLOW – Y Chart ( 1. Structural 2. Behavior 3. Geometric ) – Simplified Design Flow • VLSI Design Style – ASIC- application specific I C ( Full Custom) – FPGA , Cell based ( Semi- Custom ) • Row and Colum of GATES ( AND , OR, NOT ) • POS or SOP • XILINX VERTEX V 45000 Gates • 100 Gates 44900 Gates Will not be connected – General Purpose ( Non Custom) • Concept of – Modularity – Locality – Regularity • Packaging Style • FPGA And CPLD Architectures

- 2. • Packaging Style – Dual In Line – Surface Mount Device – Grid Array – Flat Package

- 3. • VLSI Design Style – ASIC- application specific I C ( Full Custom) – FPGA , Cell based ( Semi- Custom ) • Row and Colum of GATES ( AND , OR, NOT ) • POS or SOP • XILINX VERTEX V 45000 Gates • 100 Gates 44900 Gates Will not be connected – General Purpose ( Non Custom) • Concept of – Modularity – Locality – Regularity

- 4. • Concept of – Modularity • Modularity in design means that the various functional blocks which make up the larger system must have well- defined functions and interfaces – Locality • The concept of locality also ensures that connections are mostly between neighboring modules, avoiding long- distance connections as much as possible – Regularity • Regularity means that the hierarchical decomposition of a large system should result in not only simple, but also similar blocks, as much as possible

- 5. Voltage Transfer Char. Of Inverter • Critical voltage: • VOH = “ Highest Output Voltage” • VOL = “ Lowest output Voltage” • VIH = “ Lowest input voltage which can be consider as logic “1”. • VIL = “ Highest input voltage which can be consider as logic “0”

- 6. 2 3 = 2 V =1.5 V NOISE MARGIN NML = VIL-VOL = 4V = 3.5 V NOISE MARGIN NMH = VOH-VIH

- 7. INVERETER Input Output VOH = “ Highest Output Voltage” VOL = “ Lowest output Voltage” VIH = “ Lowest input voltage which can be consider as logic “1”. Ex. VIH = 4 V VIL = “ Highest input voltage which can be consider as logic “0” Ex. VIL = 2 V 0 1 0 1