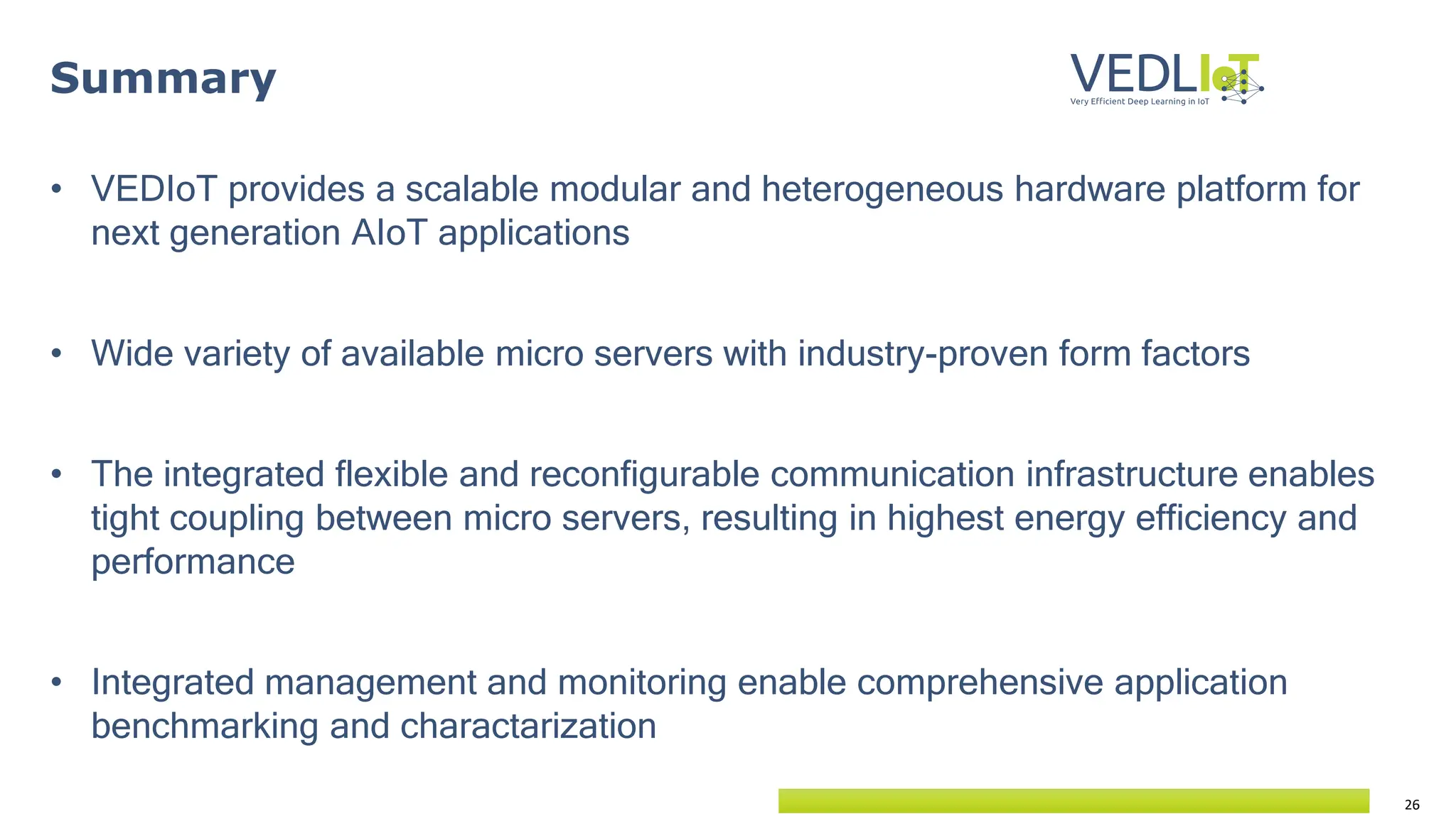

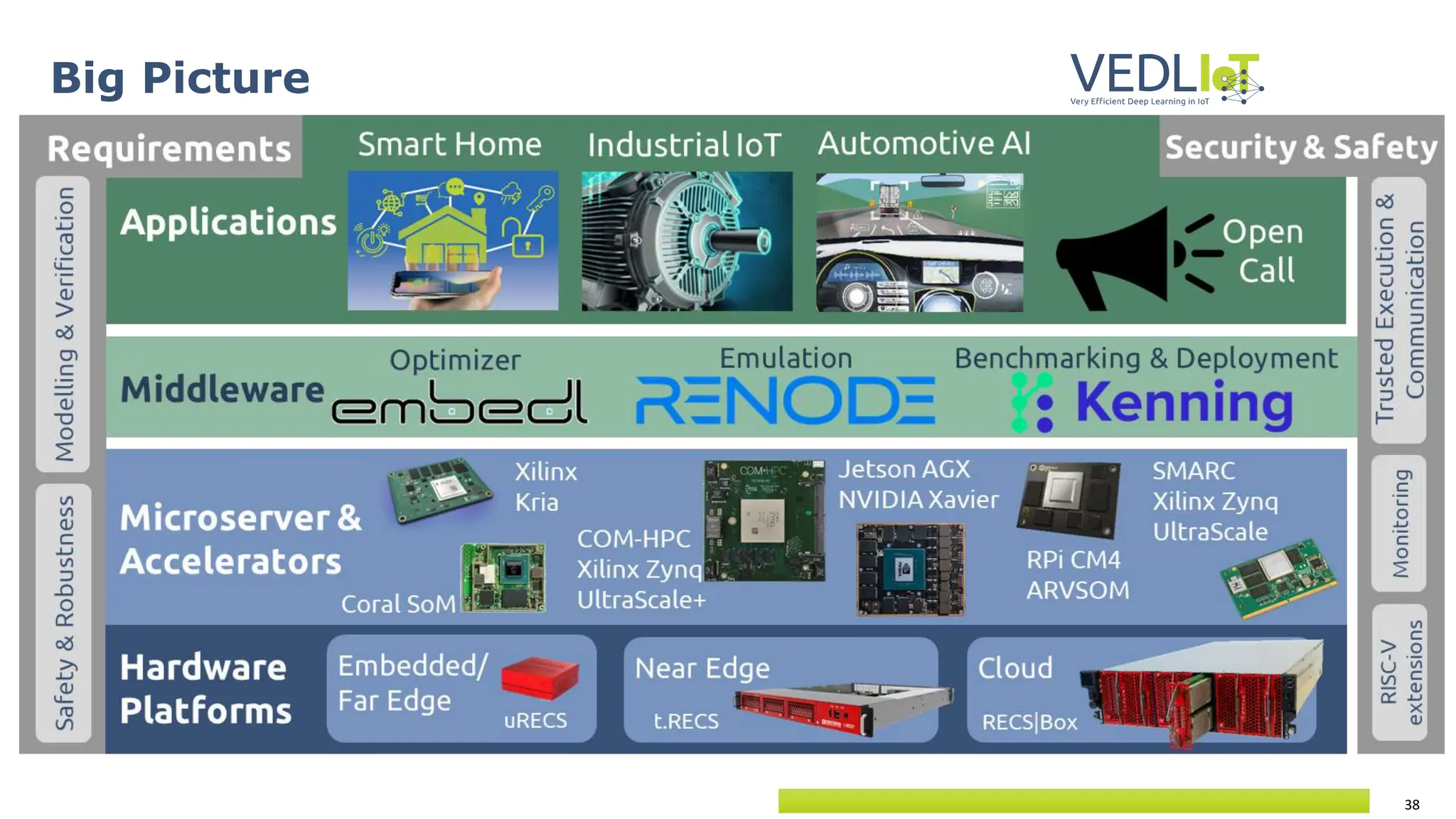

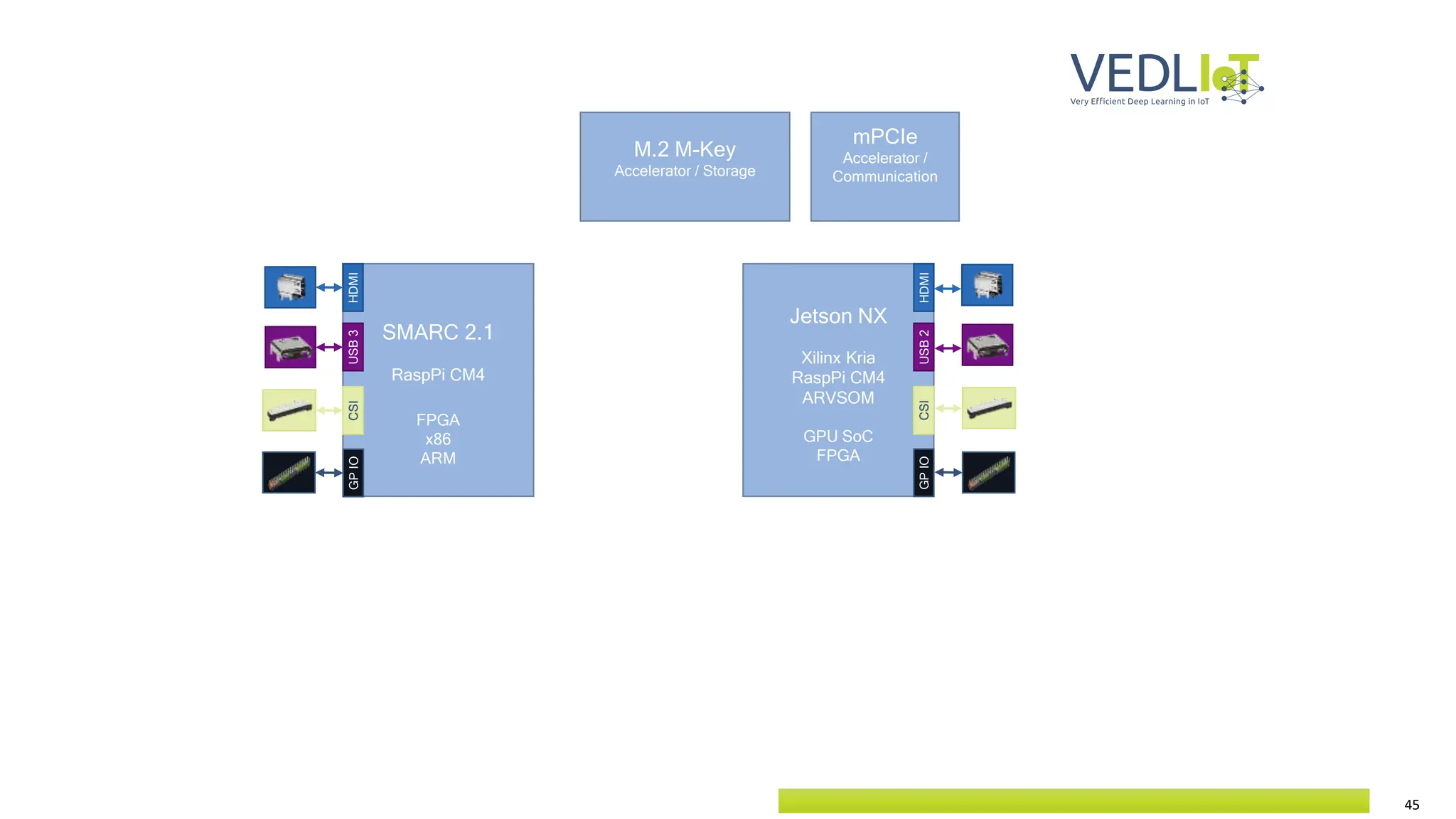

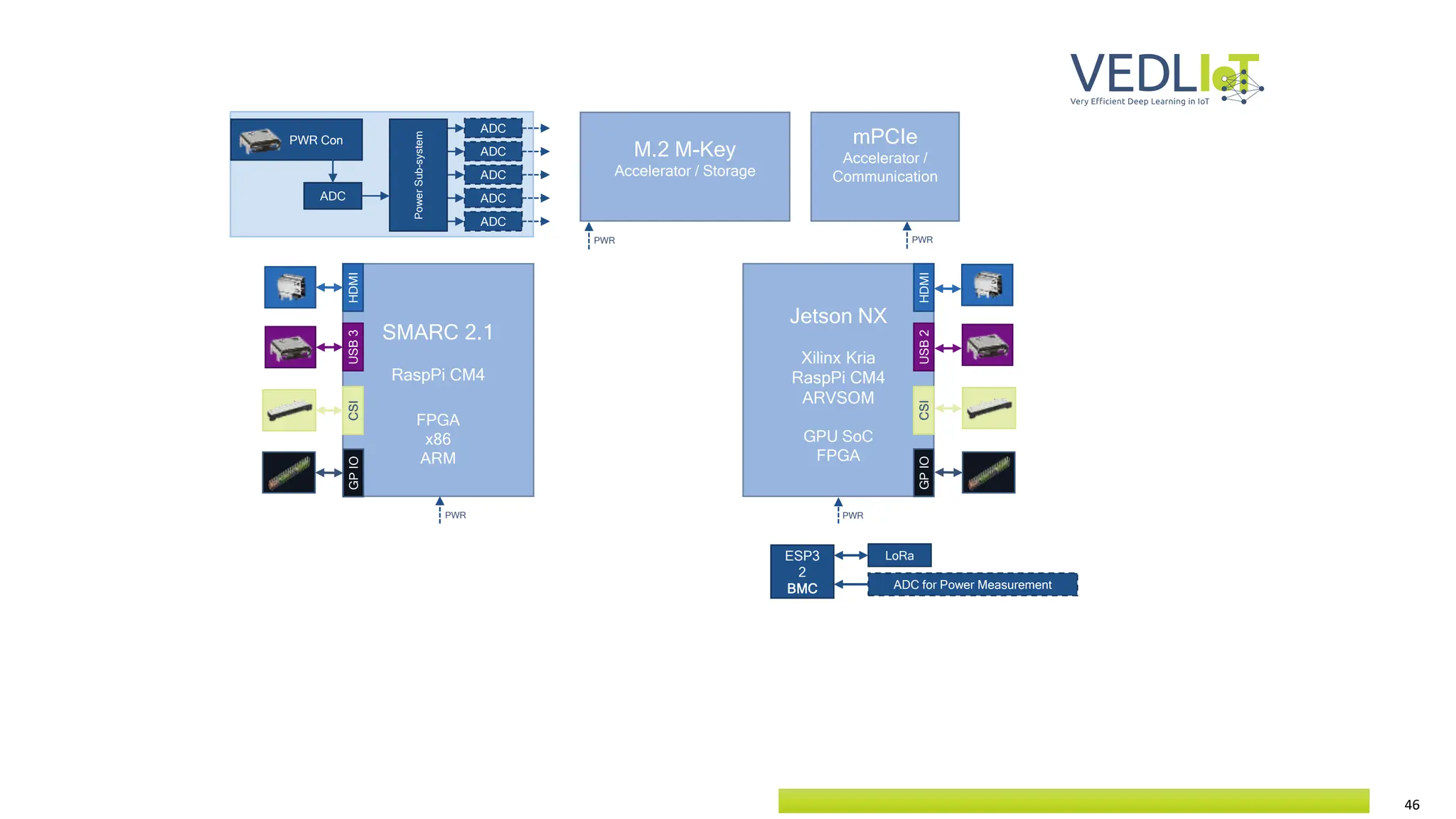

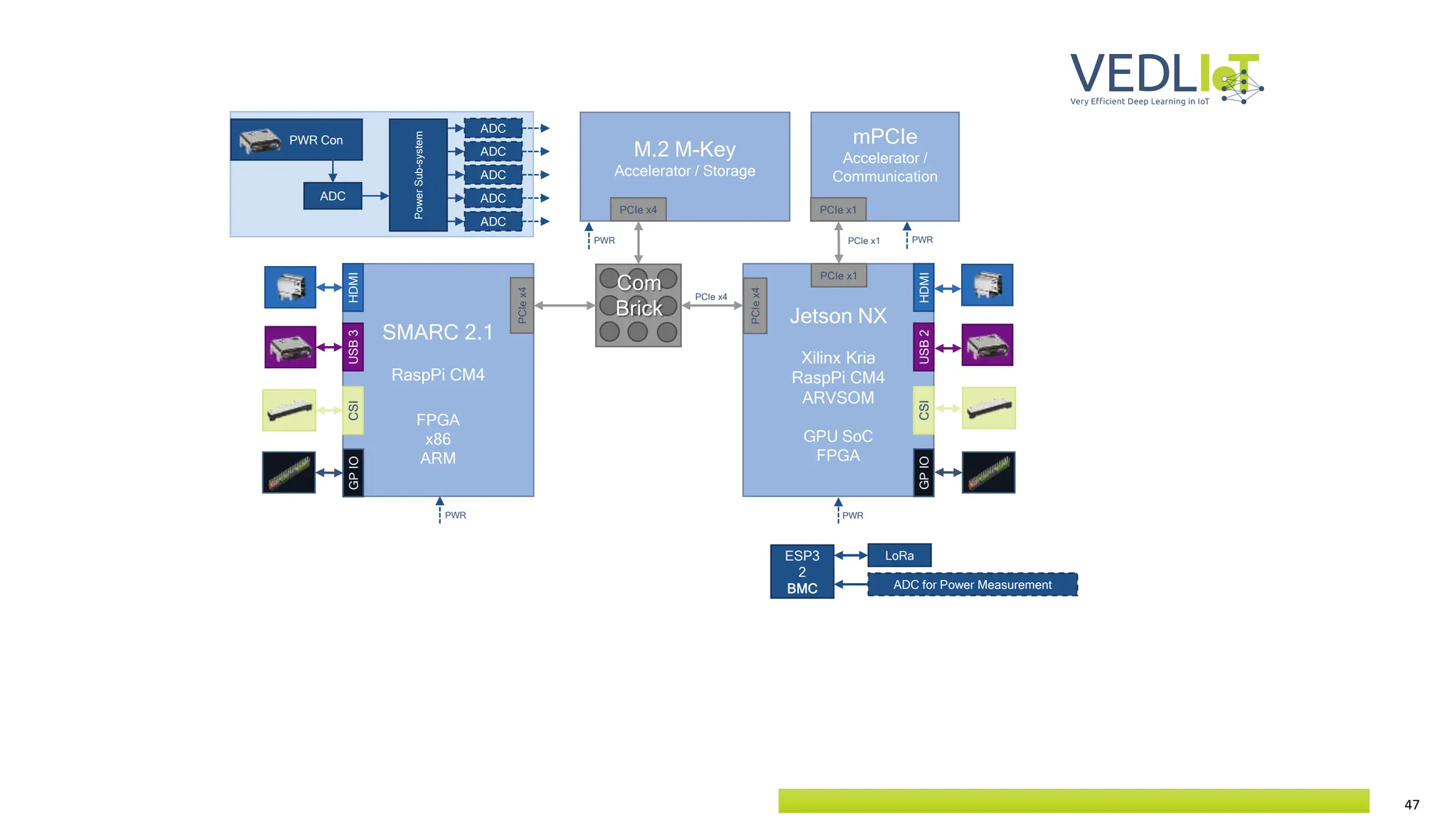

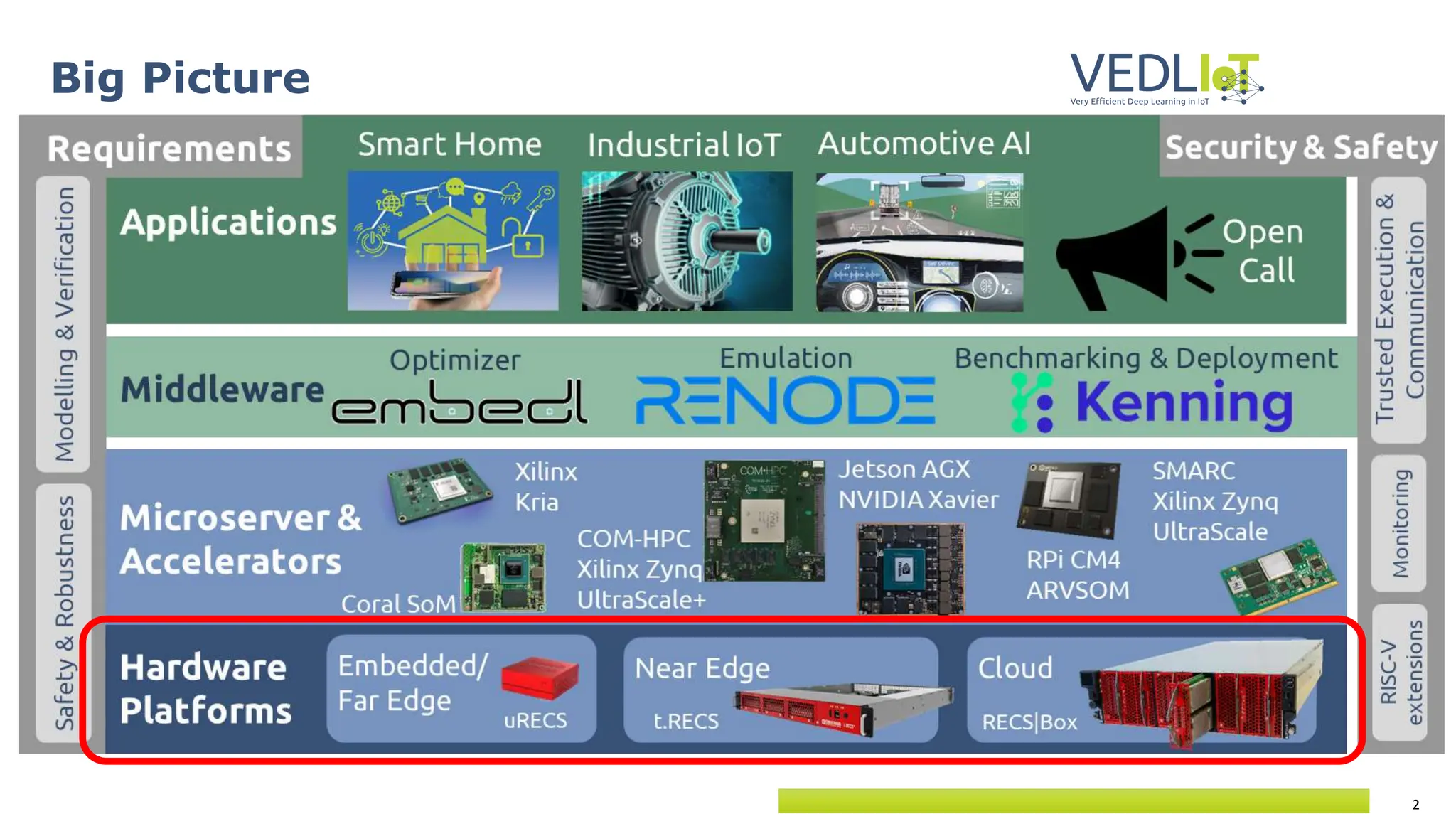

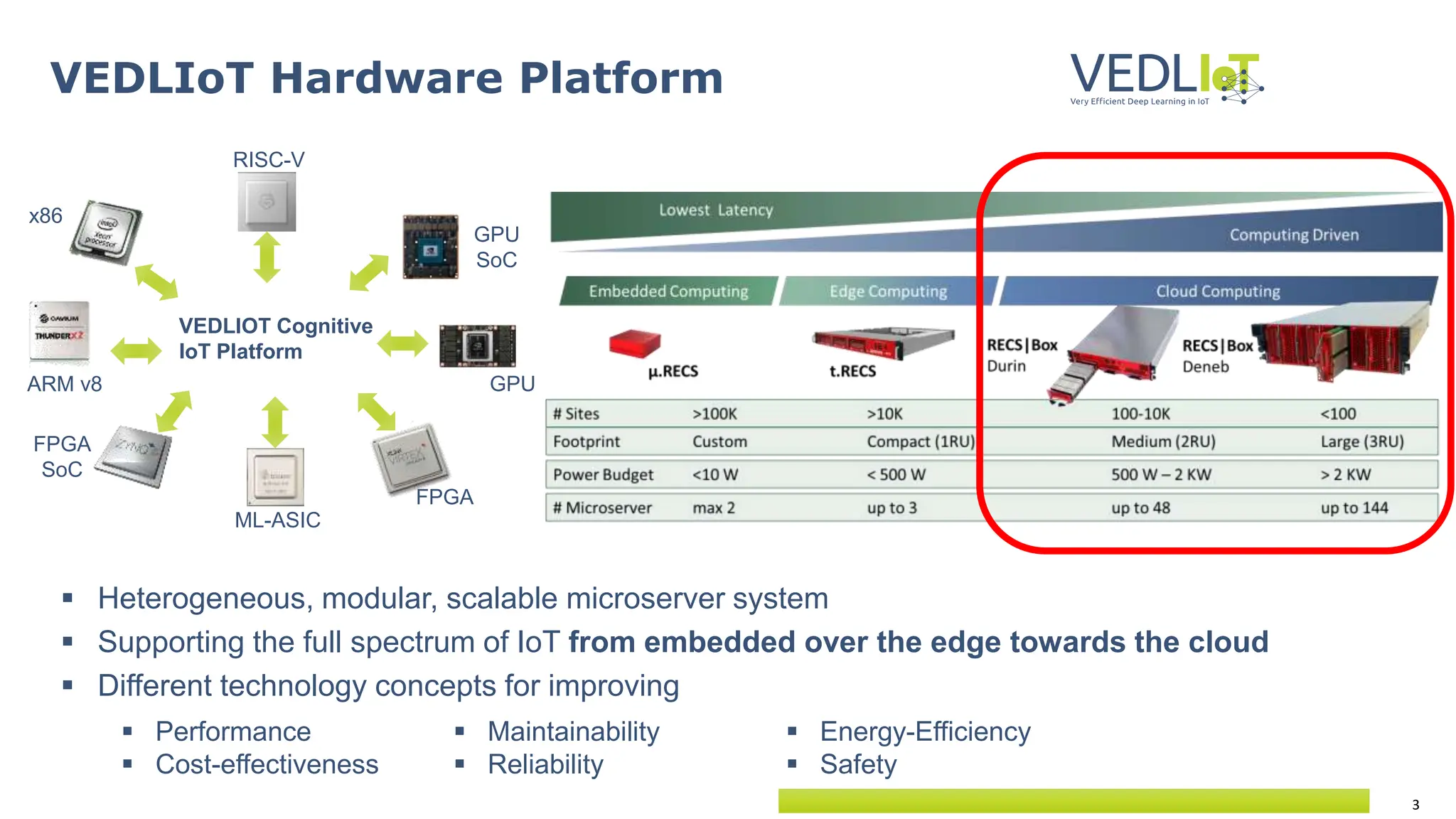

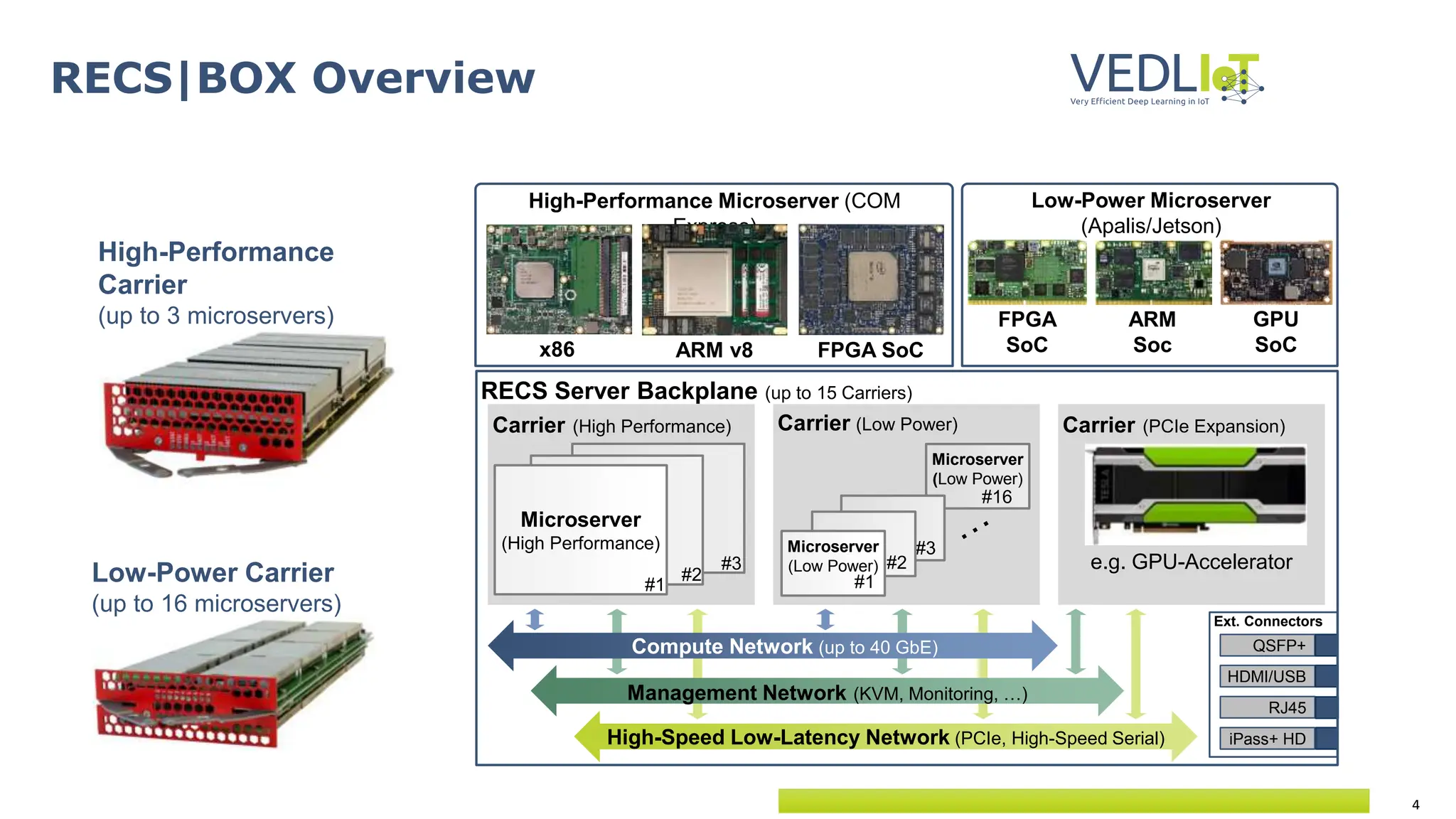

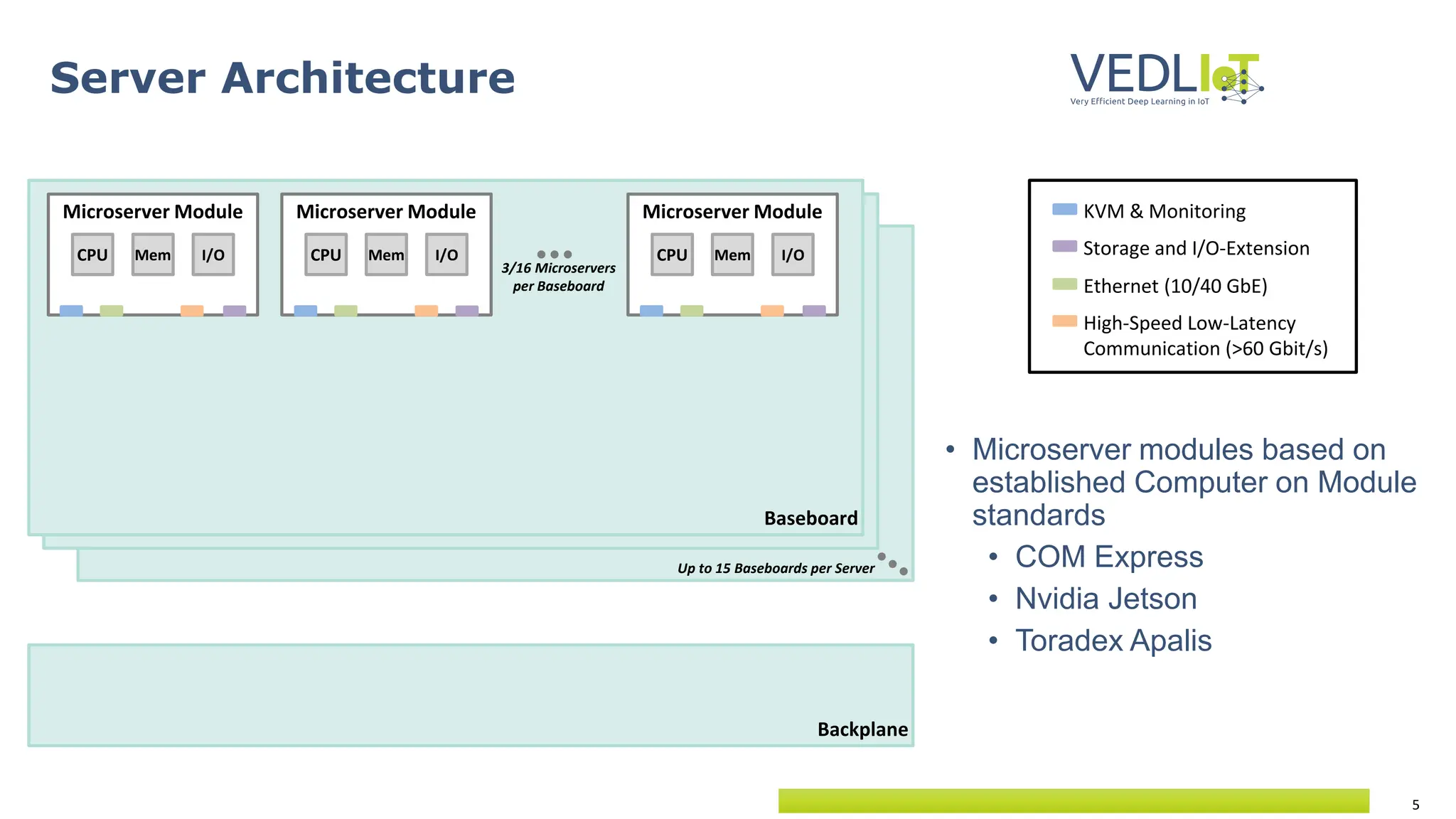

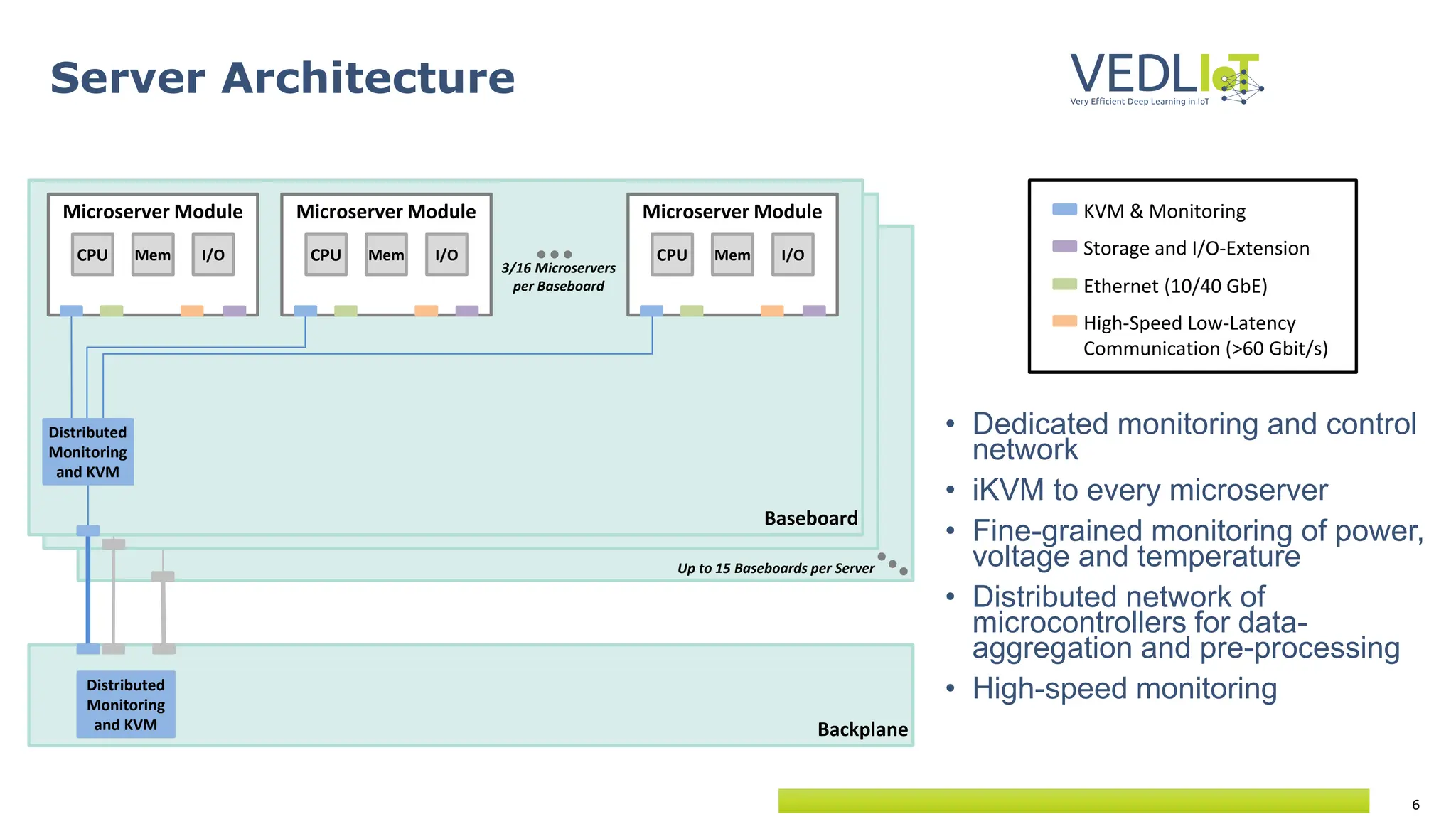

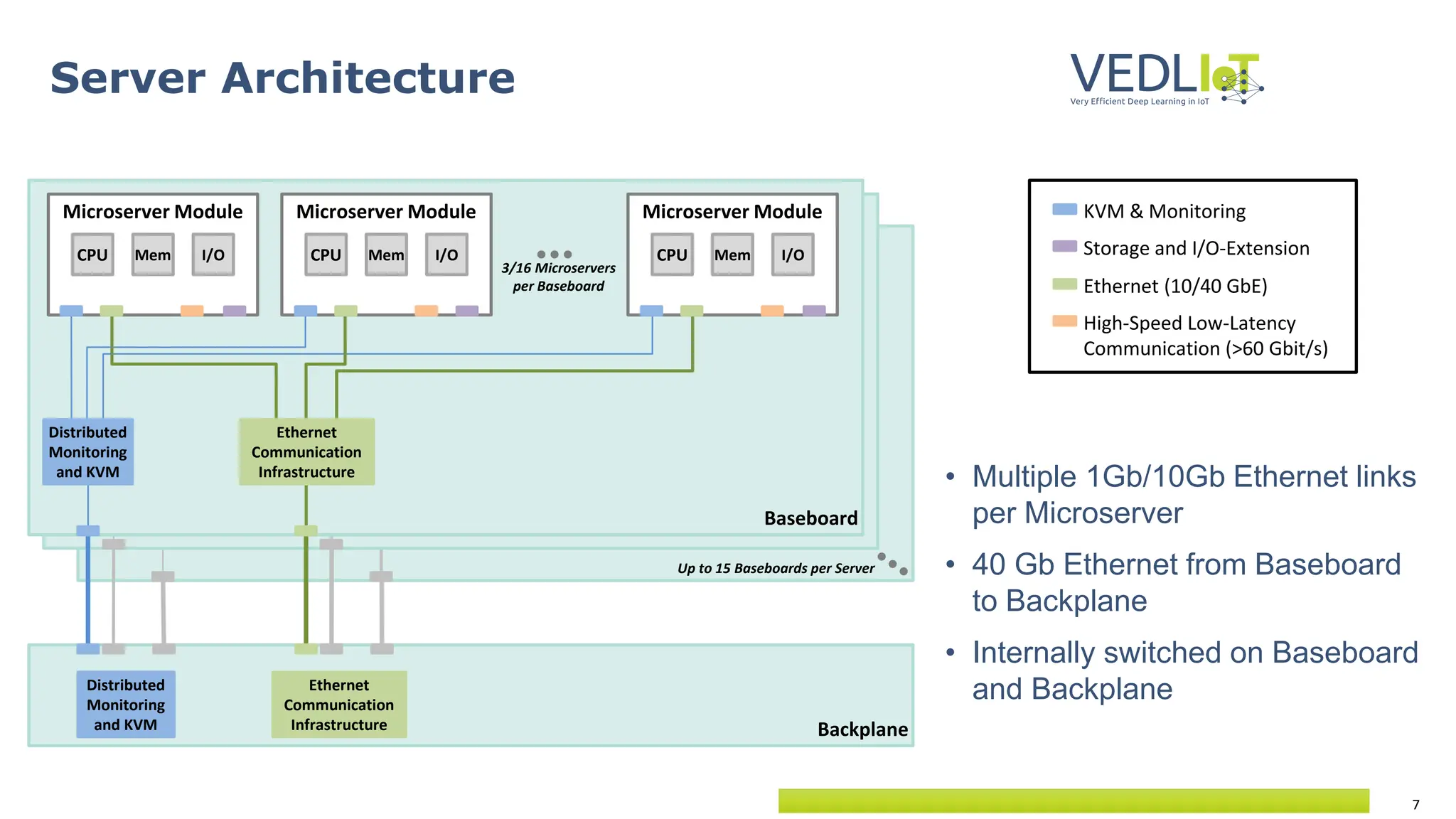

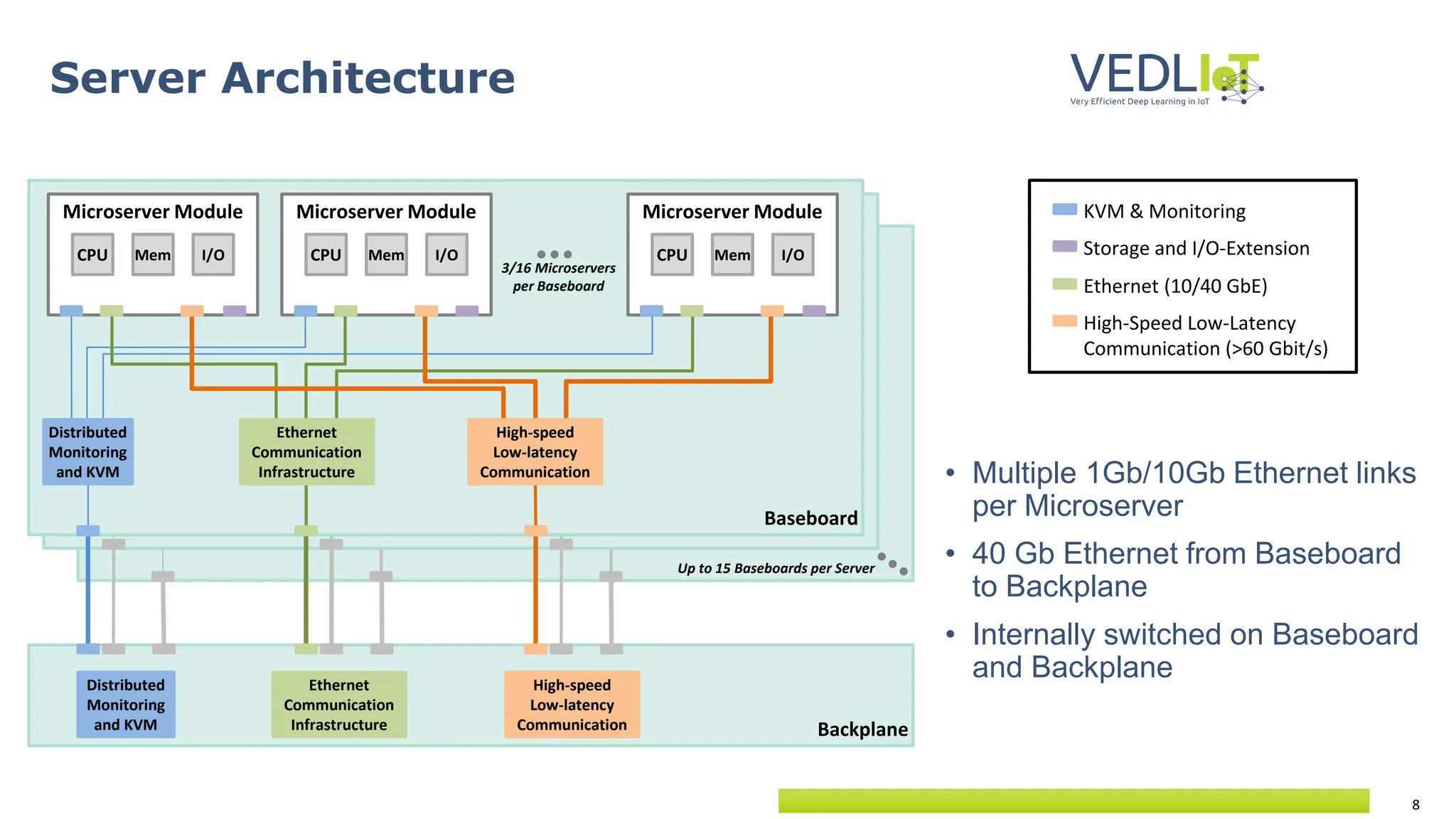

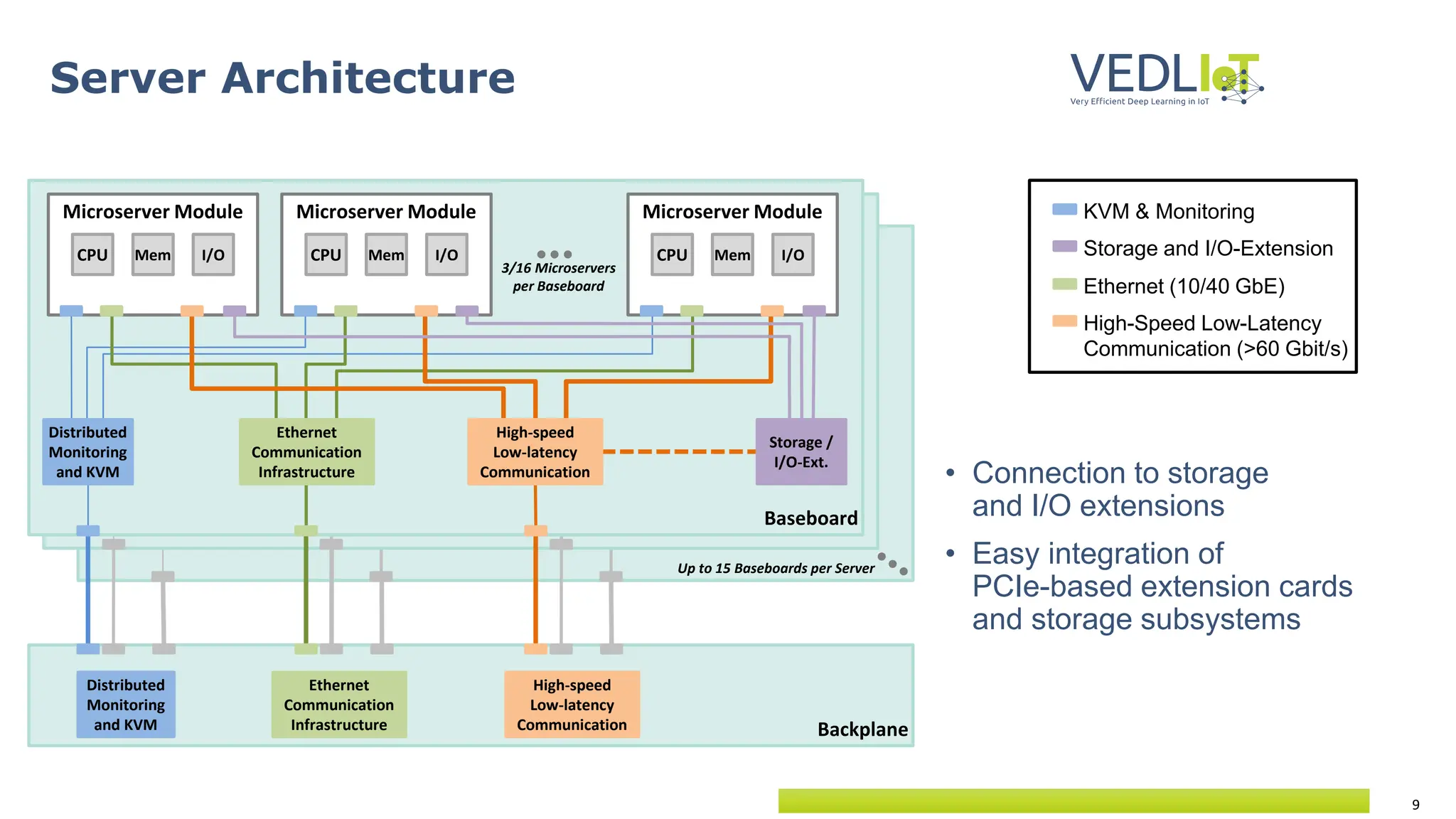

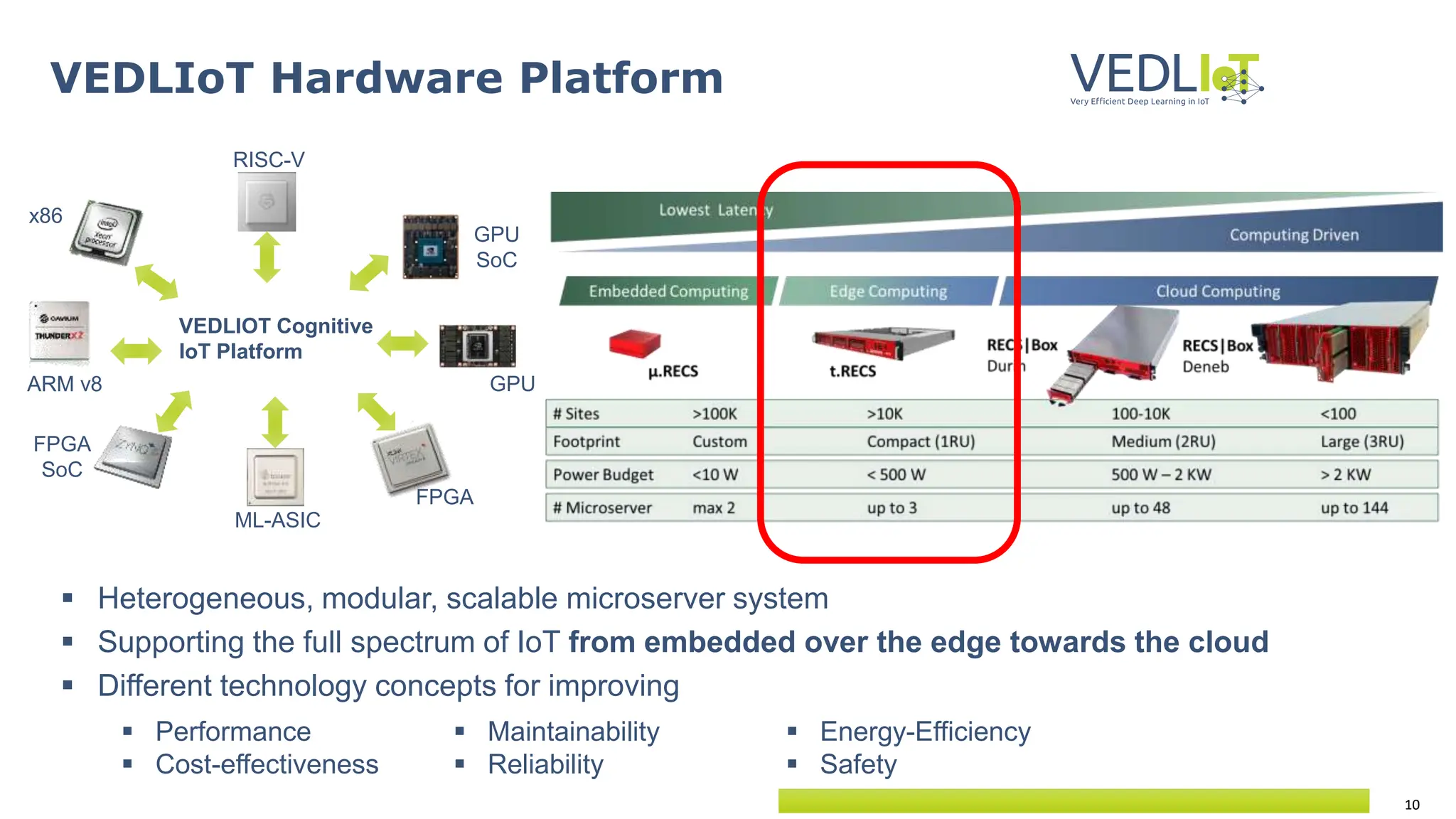

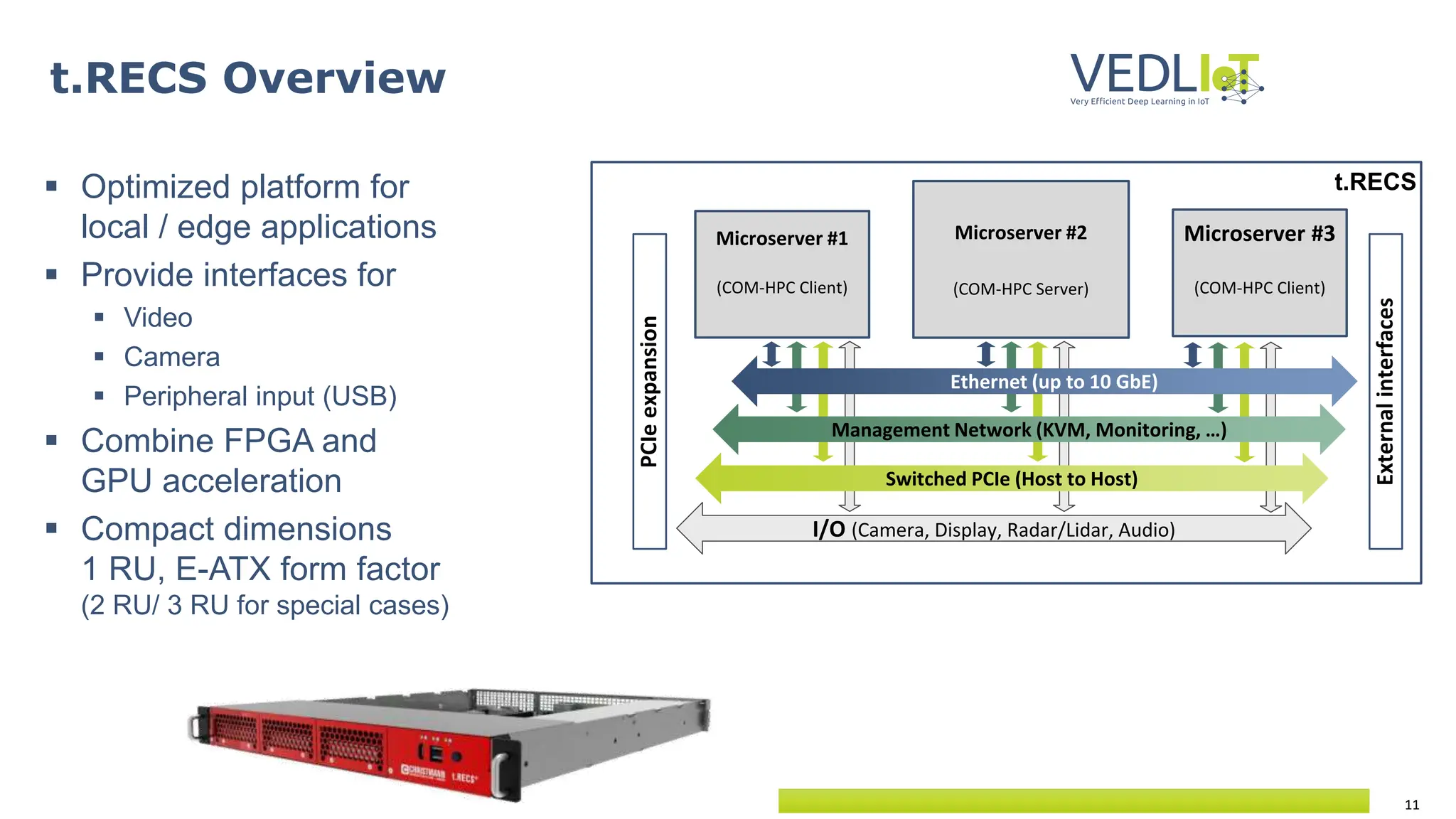

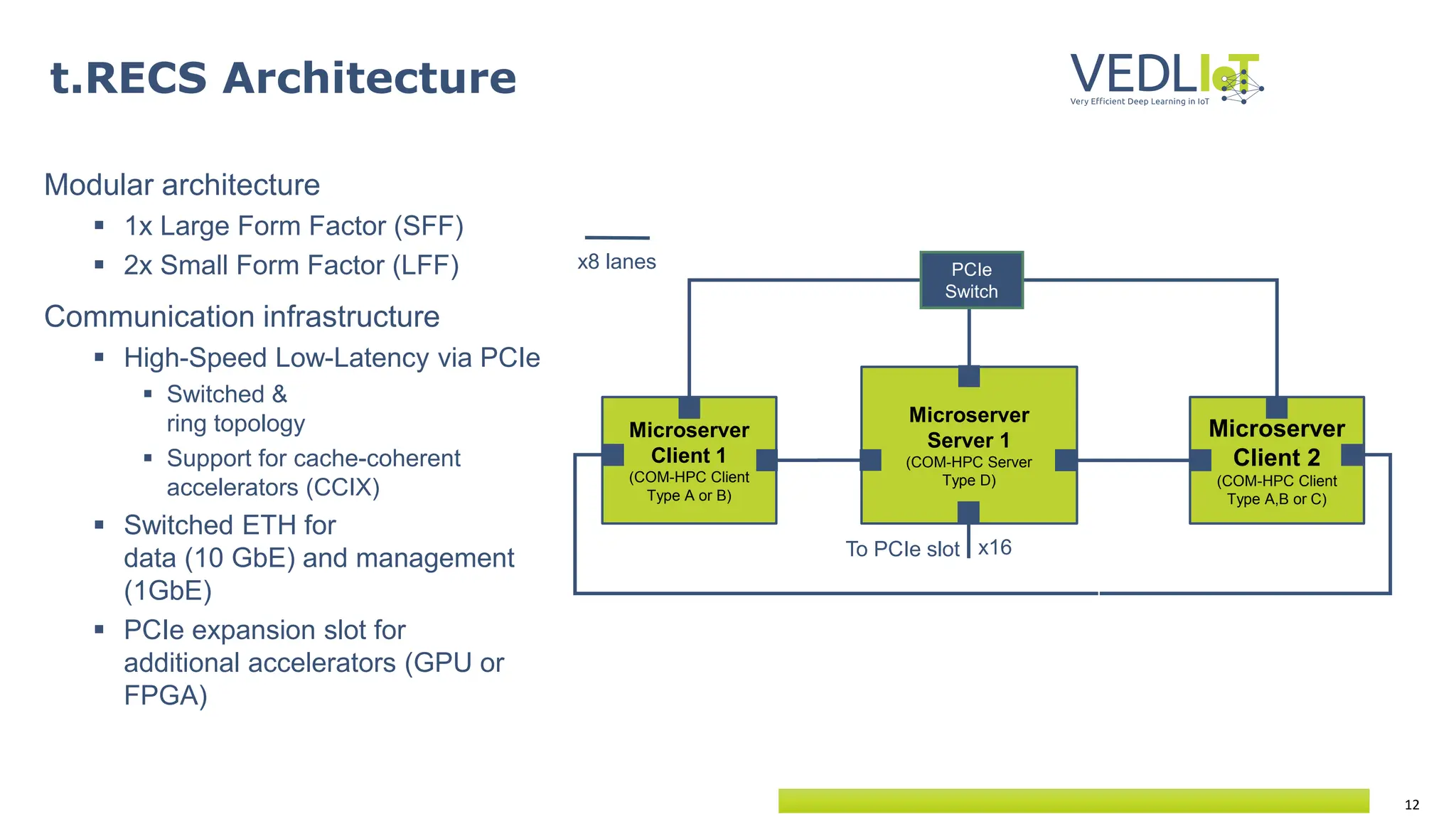

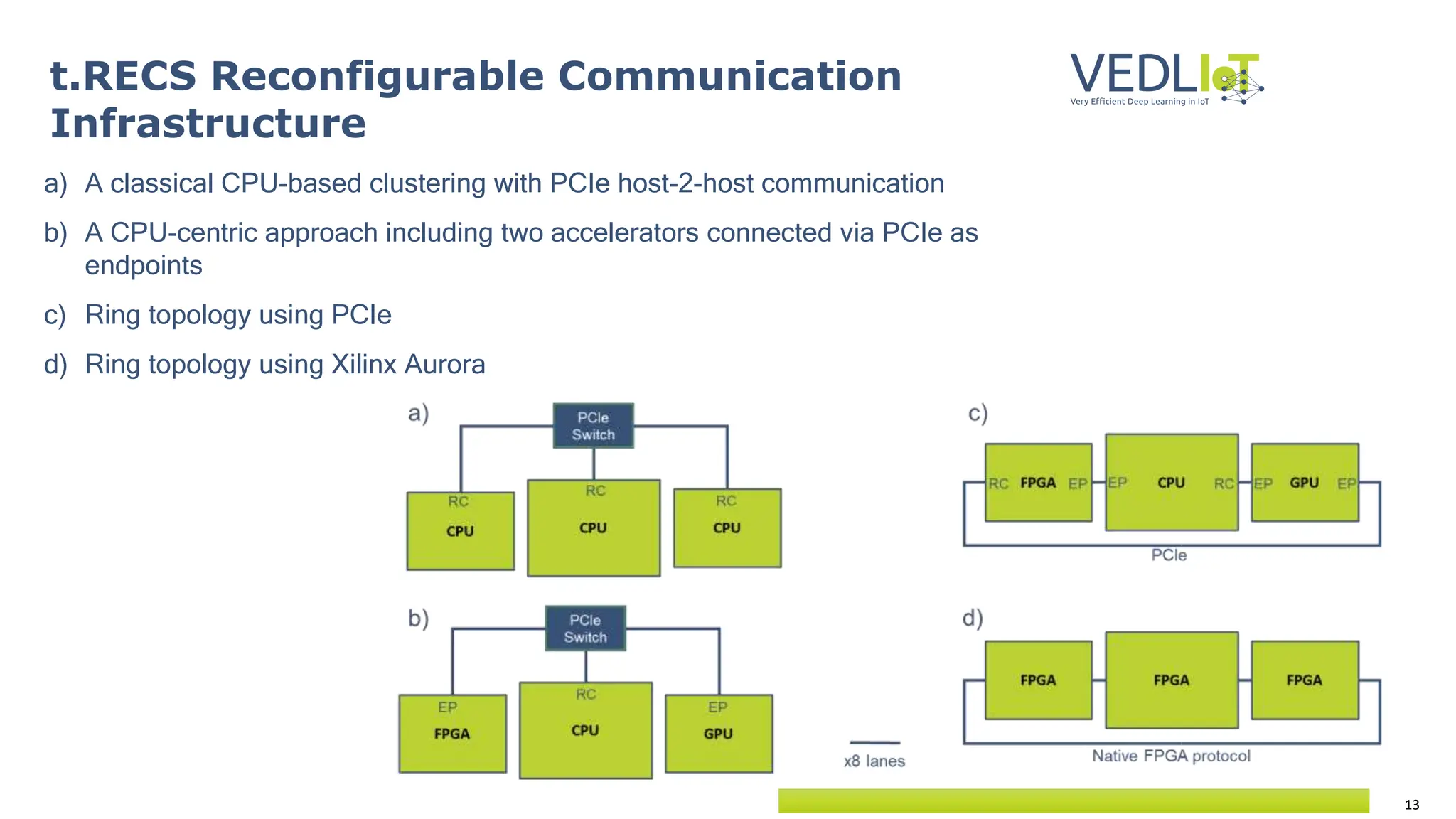

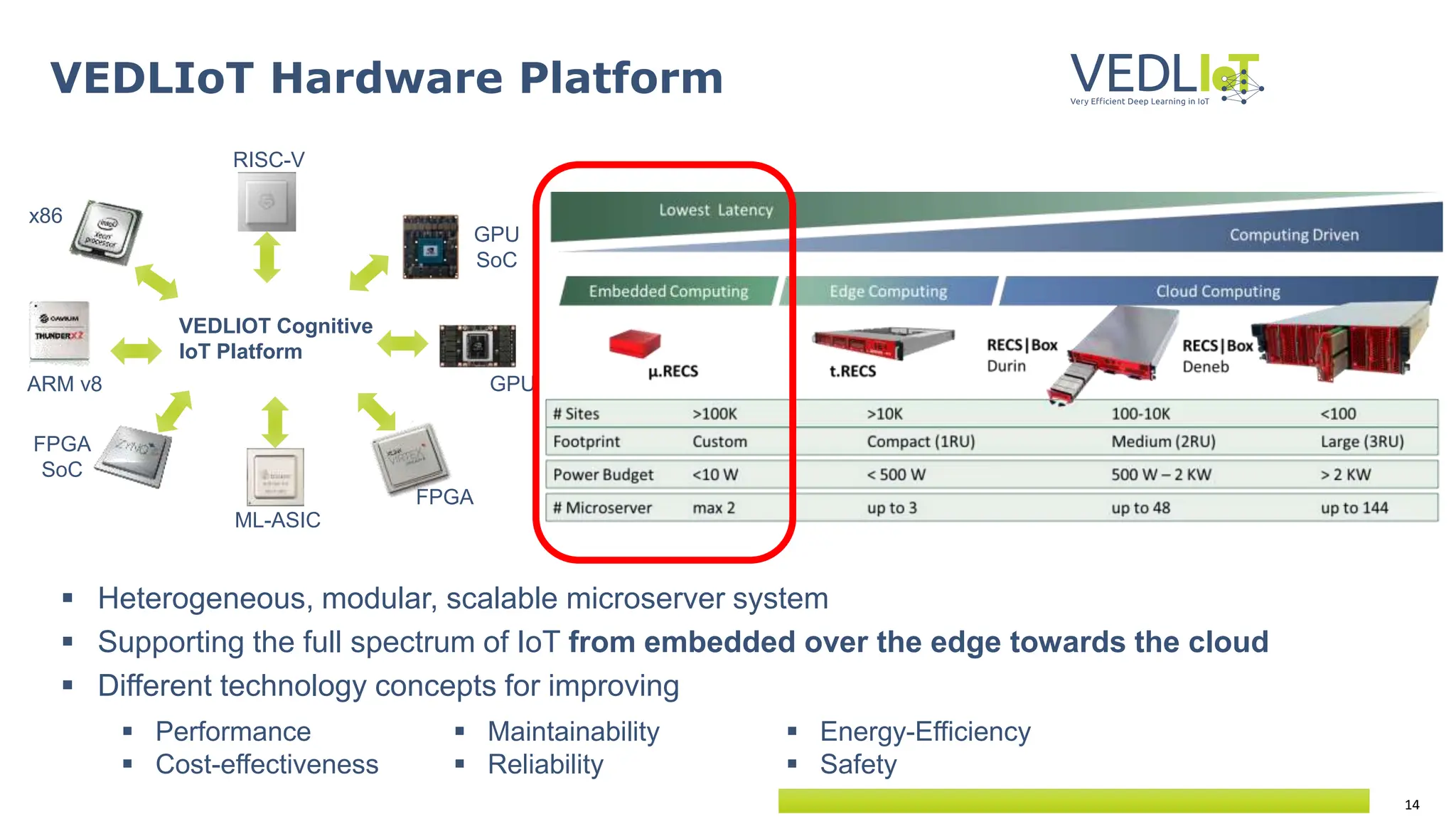

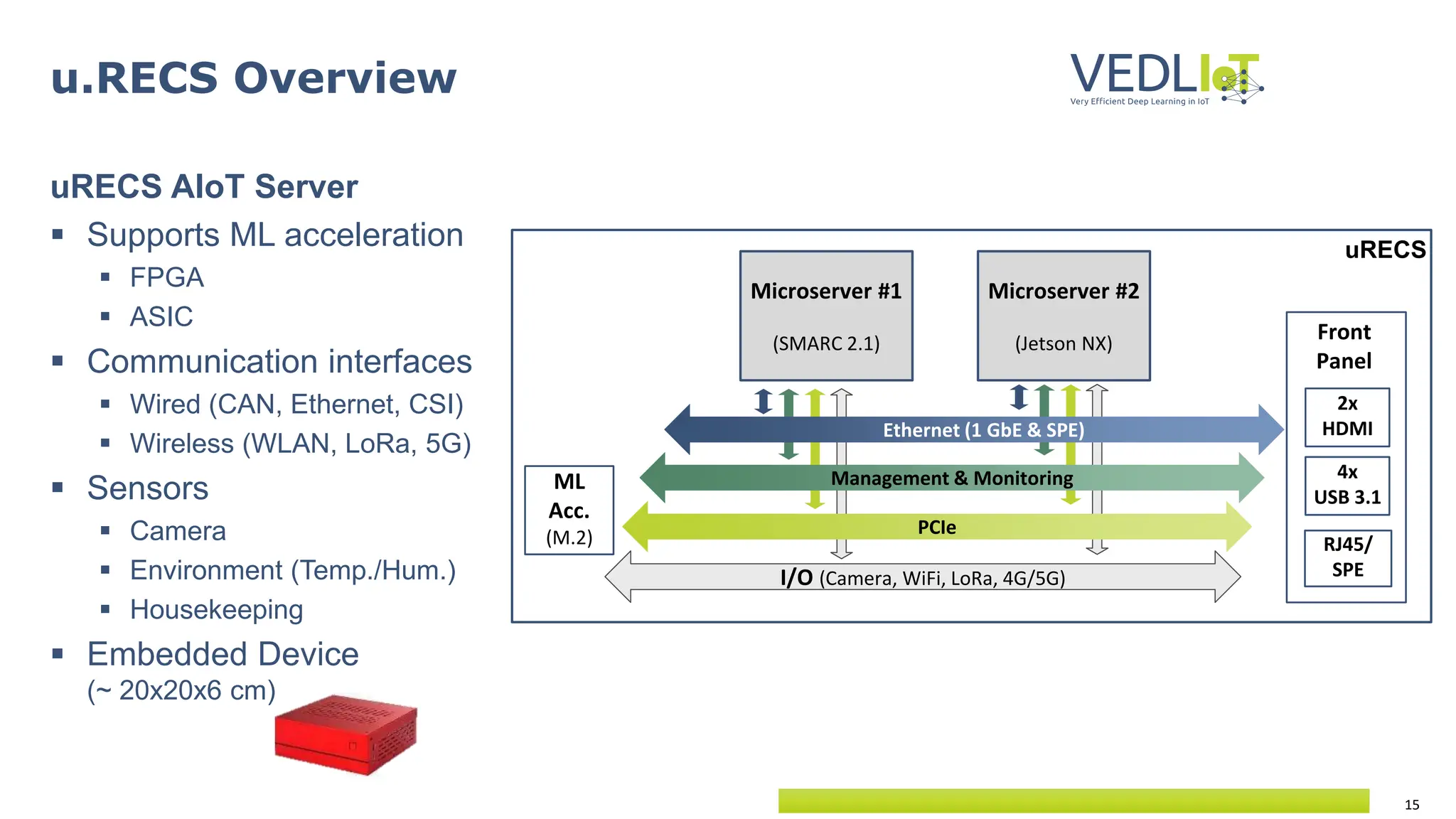

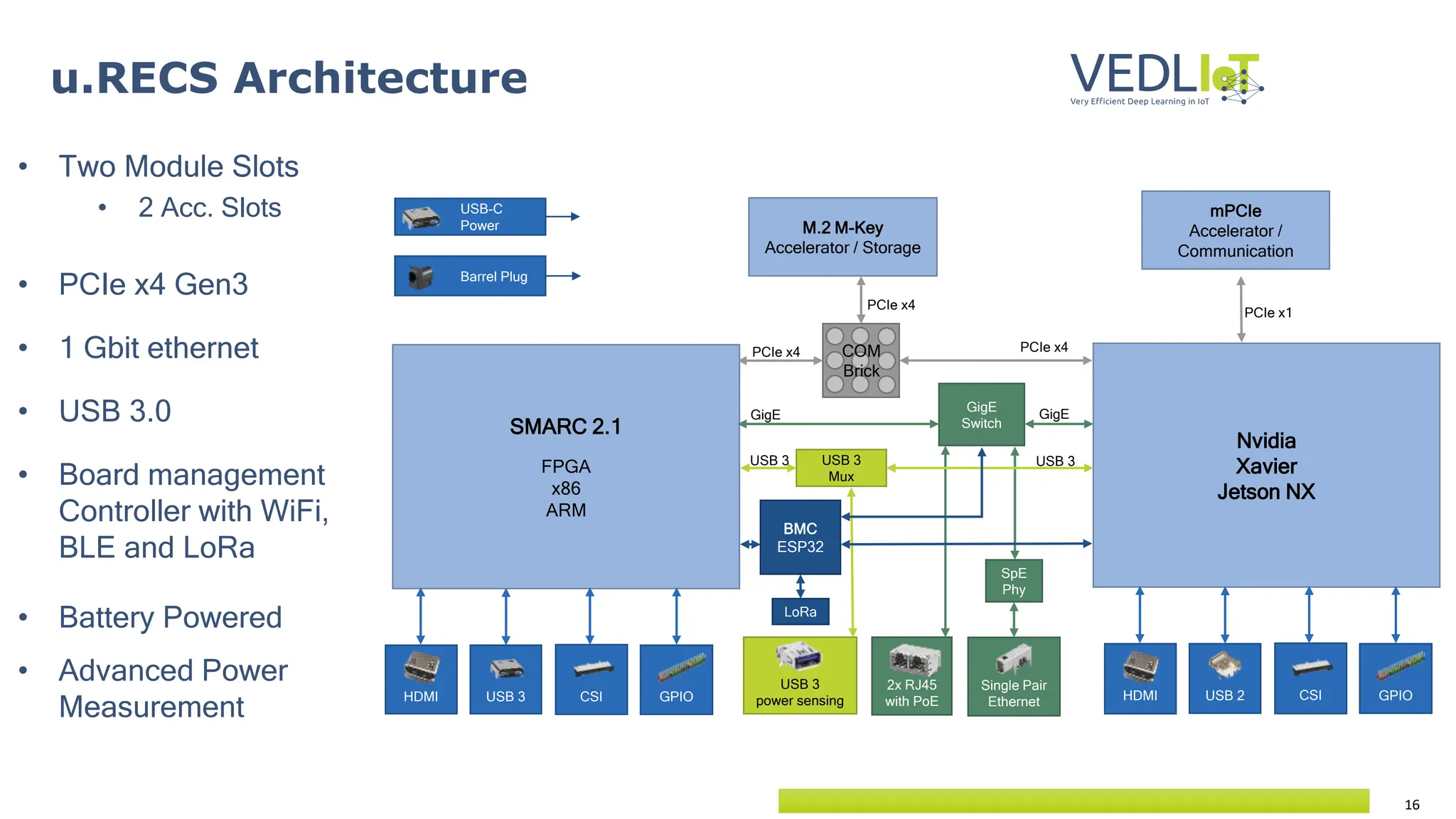

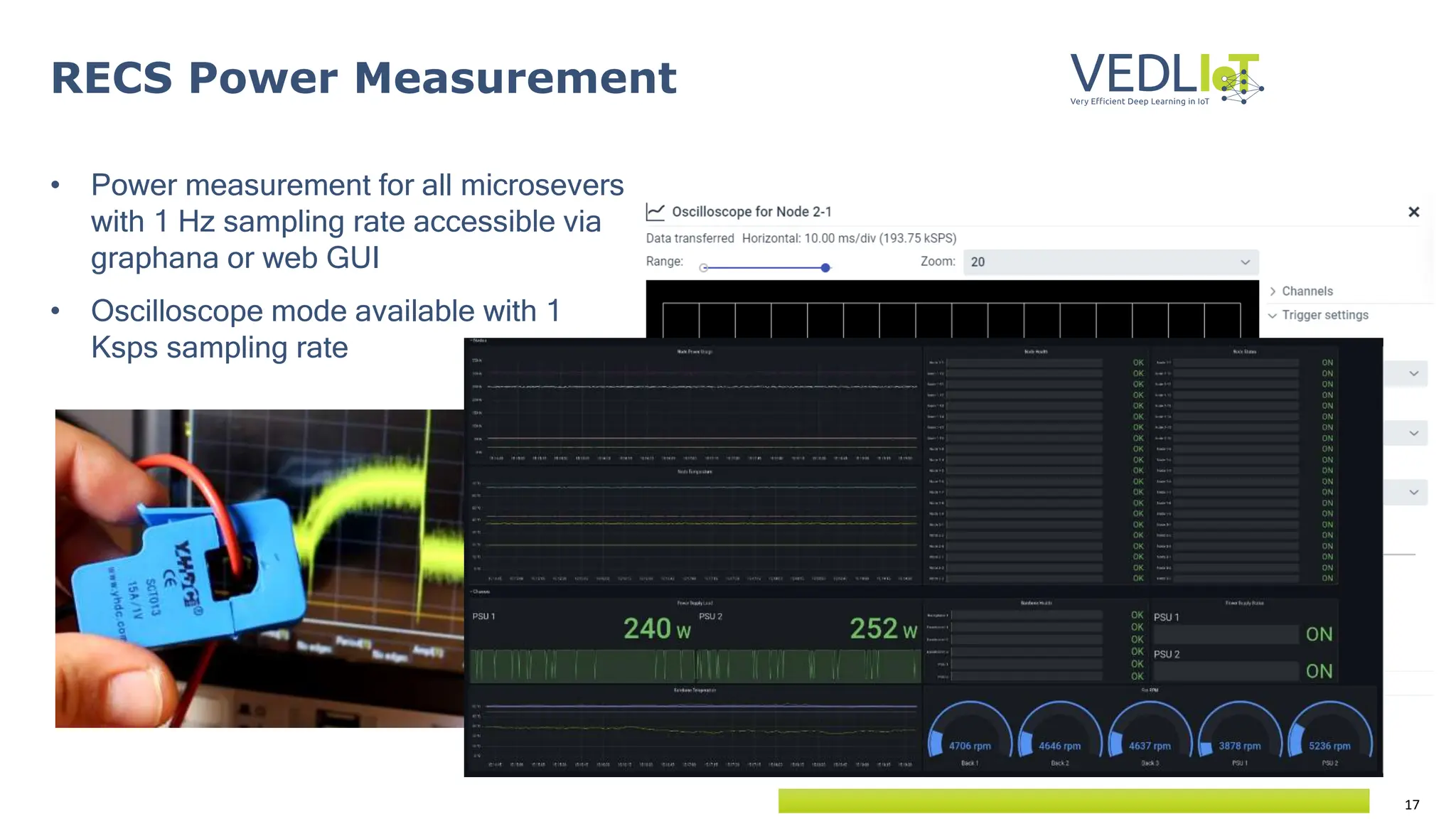

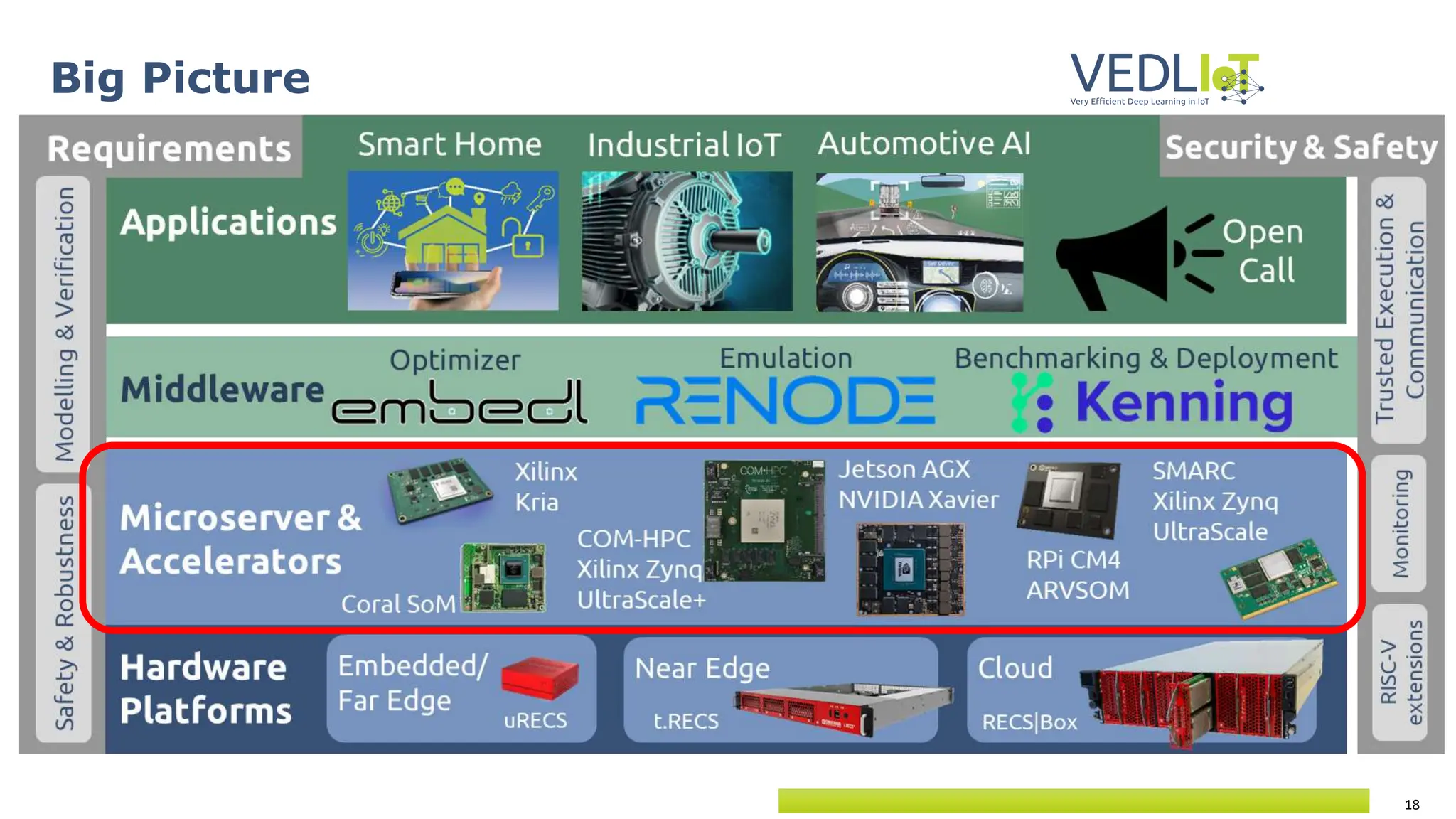

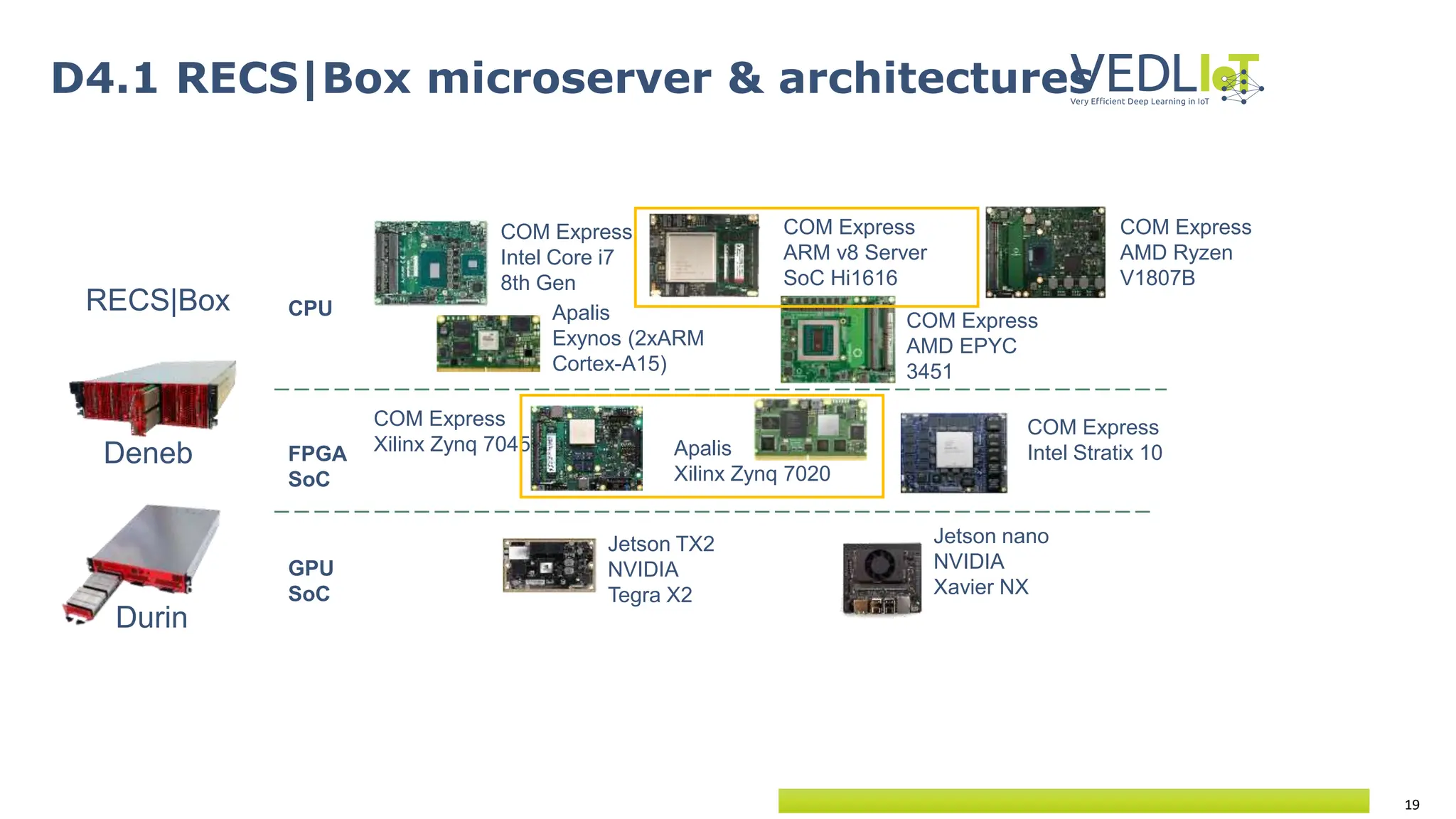

The document discusses hardware platforms and accelerators for VEDLIoT. It describes the VEDLIoT Hardware Platform as a heterogeneous, modular, and scalable microserver system that supports the IoT spectrum from embedded to edge to cloud. It then provides details on several platforms: the RECS|Box platform which uses Computer-on-Module standards to achieve flexibility and performance; the t.RECS platform optimized for local edge applications; and the uRECS embedded device platform that supports machine learning acceleration and communication interfaces. Diagrams and specifications are given for the architectures of these platforms.

![23

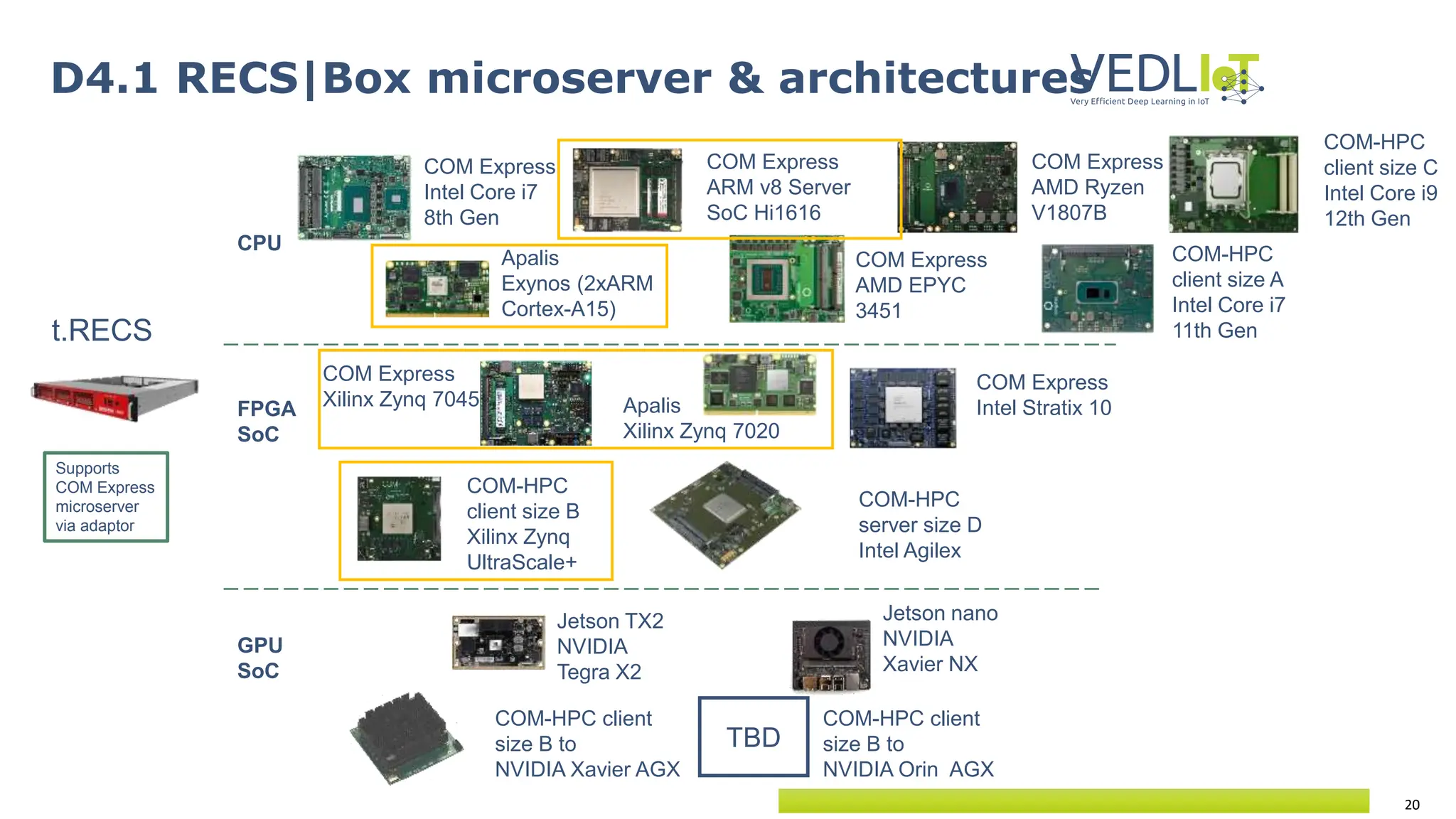

Peak performance values of specialized accelerators, provided by the

vendors (precisions varying from INT8 to FP32)

Peak Performance of DL Accelerators

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

Kendryte K210

[CELLRANGE]

[CELL…

[CELLRA…

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRAN…

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

1

10

100

1000

10000

100000

1000000

0.001 0.01 0.1 1 10 100 1000

Performance

[GOPS]

Power [Watt]

Devices

IP Cores

Average efficiency at 1000 GOPS /W](https://image.slidesharecdn.com/hipeaccswapr22vedliotharware-240206110640-fecbbe29/75/HiPEAC-CSW-2022_Kevin-Mika-presentation-23-2048.jpg)

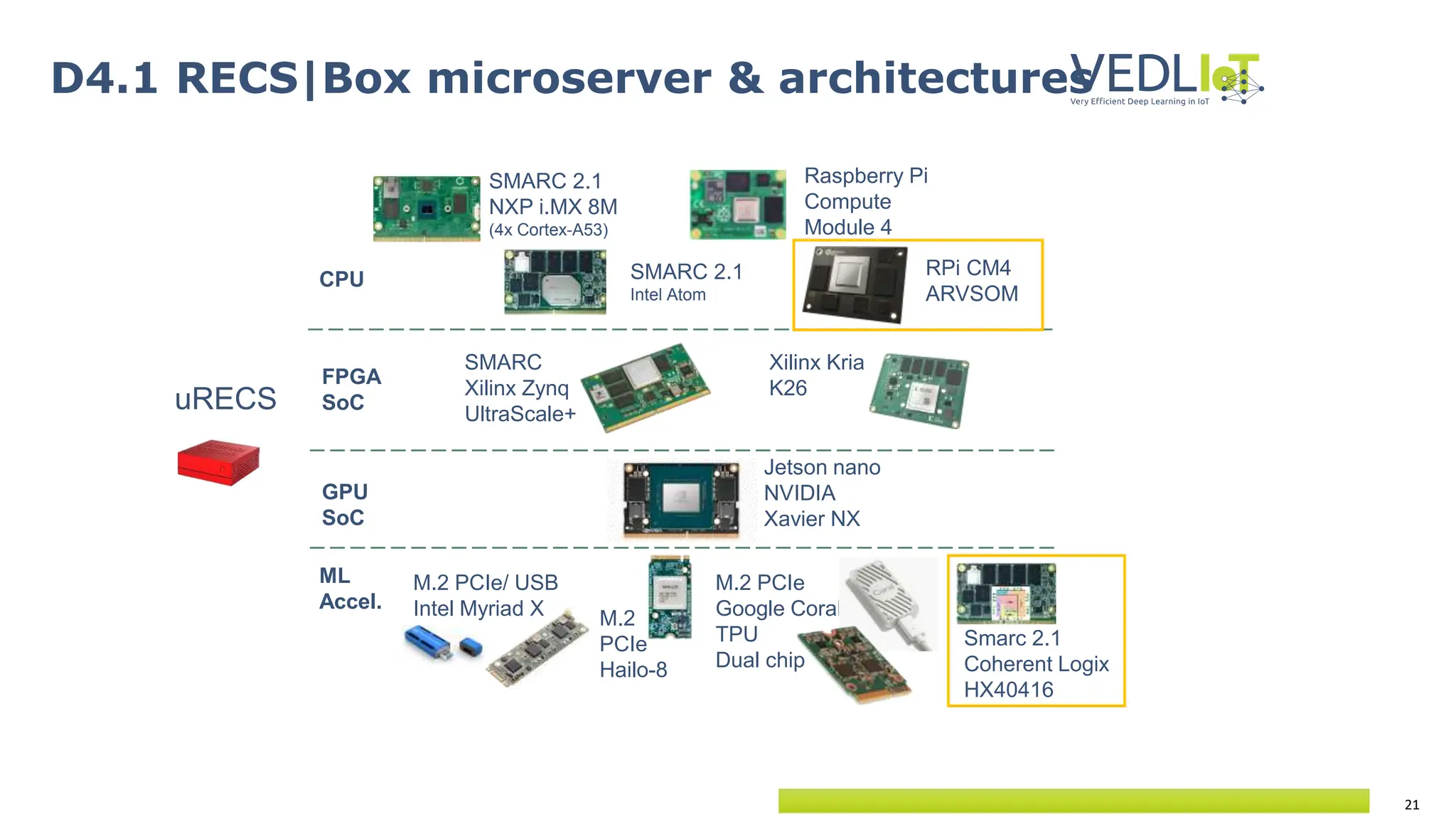

![24

Benchmark performance of DL accelerators

YoloV4

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLR…

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRAN…

[CELLRANGE]

10

100

1000

10000

2 4 8 16 32 64 128

Performance

[GOPS]

Power [Watt]

INT8 FP16 FP32](https://image.slidesharecdn.com/hipeaccswapr22vedliotharware-240206110640-fecbbe29/75/HiPEAC-CSW-2022_Kevin-Mika-presentation-24-2048.jpg)

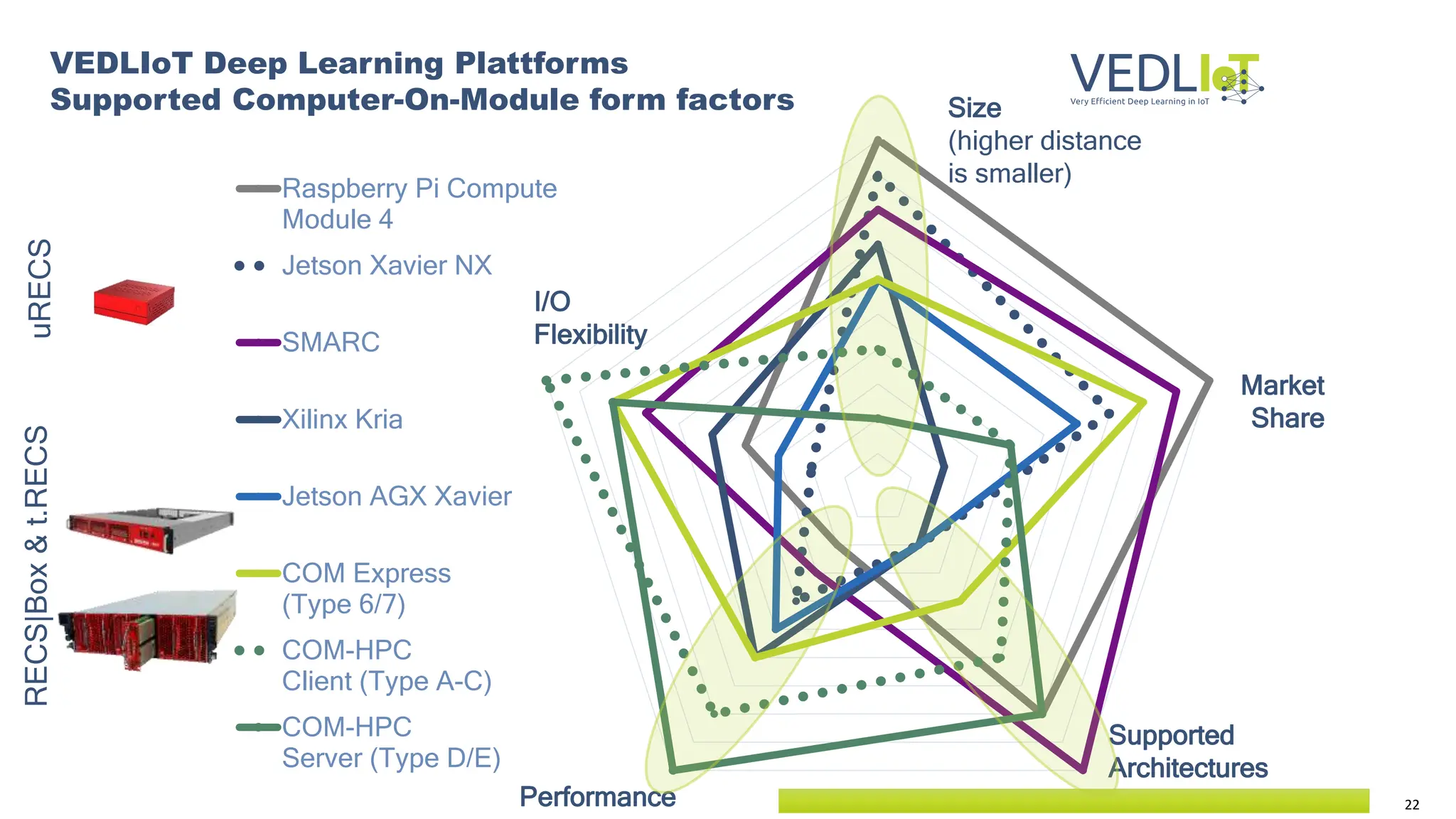

![25

Benchmark performance of DL accelerators

Comparison based on currently available architectures

VEDLIoT will include new specialized accelerators

0

50

100

150

200

250

300

350

Coral (M.2) Coral (Dev.) Xavier AGX

(LP)

Xavier AGX

(HP)

Xavier NX TX2 Nano GTX1660 ZU15 ZU3 Xeon-D1577 Epyc3451 Myriad GAP8

Energy Efficiency [GOPS/W]

ResNet50 Int 8 ResNet50 FP16 ResNet50 FP32

YoloV4 Int 8 YoloV4 FP16 YoloV4 FP32

MobileNet Int 8 MobileNet FP16 MobileNet FP32](https://image.slidesharecdn.com/hipeaccswapr22vedliotharware-240206110640-fecbbe29/75/HiPEAC-CSW-2022_Kevin-Mika-presentation-25-2048.jpg)