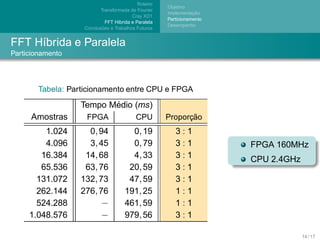

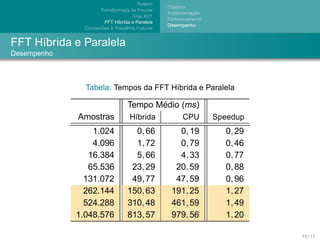

Este documento descreve uma implementação híbrida e paralela da Transformada Rápida de Fourier (FFT) no supercomputador Cray XD1, que combina processamento em CPU e FPGA. A abordagem é dividida entre software em C e hardware em VHDL, com diferentes tamanhos de entrada sendo processados em cada componente. Os resultados mostram um ganho de desempenho para certos tamanhos de entrada. Trabalhos futuros incluem melhorias no pipeline e uso de radix-4.

![Roteiro

Objetivo

Transformada de Fourier

¸˜

Implementacao

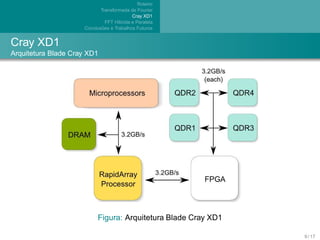

Cray XD1

Particionamento

FFT H´brida e Paralela

ı

Desempenho

˜

Conclusoes e Trabalhos Futuros

FFT H´brida e Paralela

ı

Software

f o r passo from 1 to N by 2

f o r j from 0 to passo by 1

c a l c u l a f a t o r de g i r o

f o r i from j to N by passo ∗2

c a l c u l a b o r b o l e t a ( data [ i ] , data [ i + passo ] )

end f o r

end f o r

end f o r

Implementado em Linguagem C

˜

Compilado com GCC versao 3.3.3

12 / 17](https://image.slidesharecdn.com/apresentacao-091023082358-phpapp02/85/WSCAD2009-12-320.jpg)