Direct Memory Access (DMA)-Working and Implementation

DMA is an important functionality of any computing system involving transfer of data from/to an I/O device. In this presentation, a brief description has been provided regarding how the DMA functionality is implemented on a normal PC as well as on an Intel Quark SoC based small Embedded System.Different implementations of the DMA functionality depend on the Controller Hub present on the SouthBridge of the MotherBoard of the respective platform.For example->DMA implementation in Intel ICH7 is different from those in Intel ICH to Intel ICH6. In the slides, "Galileo" refers to the Intel Galileo Board containing Intel Quark SoC. Intel Galileo Board contains Designware DMA controllers." dmatest.c " is a memory-to-memory data transfer test driver implementing DMA. This module is loaded and then memcpy is checked using dmesg. Do take a look at the "External Links and References" given at the end of the PPT.

Recomendados

Mais conteúdo relacionado

Mais procurados

Mais procurados (20)

Destaque

Destaque (20)

Semelhante a Direct Memory Access (DMA)-Working and Implementation

Semelhante a Direct Memory Access (DMA)-Working and Implementation (20)

Mais de Shubham Kumar

Mais de Shubham Kumar (8)

Último

Último (20)

Direct Memory Access (DMA)-Working and Implementation

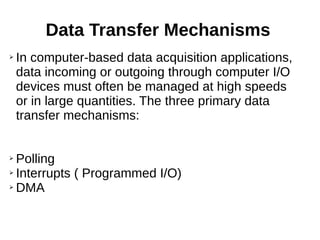

- 1. Data Transfer Mechanisms ➢ In computer-based data acquisition applications, data incoming or outgoing through computer I/O devices must often be managed at high speeds or in large quantities. The three primary data transfer mechanisms: ➢ Polling ➢ Interrupts ( Programmed I/O) ➢ DMA

- 2. DMA Transfer

- 3. DMA Controller The PC motherboard has a DMA controller on the South Bridge that can master the I/O bus and initiate DMA to or from a peripheral. This is usually the case for legacy ISA cards. Can be viewed in /proc/dma on Linux machines

- 4. On Galileo

- 5. DMA Implementations ➢ Native DMA ➢ ISA Bus-master DMA ➢ PCI Bus-master DMA

- 6. Native DMA The only pieces of legacy hardware that use ISA DMA and are still fairly common are Super I/O devices on motherboards that often integrate a built-in floppy disk controller, an IrDA infrared controller when FIR (fast infrared) mode is selected, and a IEEE 1284 parallel port controller when ECP mode is selected.

- 7. Native DMA

- 8. ISA Bus-master DMA ● lshw command on terminal

- 11. PCI IDE Bus-mastering ● The PCI bus also allows you to set up compatible IDE/ATA hard disk drives to be bus masters. Under the correct conditions this can increase performance over the use of PIO modes, which are the default way that IDE/ATA hard disks transfer data to and from the system. When PCI bus mastering is used, IDE/ATA devices use DMA modes to transfer data instead of PIO.

- 13. PCI IDE Bus-mastering ● hdparm -i /dev/sda ●

- 17. DMA Controller in Galileo

- 18. Quark SoC Block Diagram

- 19. Channels Present ls -l /sys/class/dma

- 20. Used and Unused Channels

- 22. dmesg

- 23. Execution of a DMA-operation (single block transfer) 1)The CPU prepares the DMA-operation by the construction of a descriptor , containing all necessary information for the DMAC to independently perform the DMA-operation (off- load engine for data transfer). 2)It initializes the operation by writing a command to a register in the DMAC (2a) or to a special assigned memory area (command area), where the DMAC can poll for the command and/or the descriptor (2b). 3)Then the DMAC addresses the device data register 4) and reads the data into a temporary data register . 5)In another bus transfer cycle, it addresses the memory block and 6) writes the data from the temporary data register to the memory block .

- 27. Contd.

- 28. Issues faced on Ubuntu

- 29. Code Flow

- 30. External links and References ➢ LDD 3- DMA ➢ Essential Linux Device Drivers ➢ https://en.wikipedia.org/wiki/Direct_memory_access ➢ http://www.pcguide.com/ref/mbsys/buses/types/pciID ➢ http://www.pcguide.com/ref/hdd/if/ide/confControllers ➢ http://www.tweak3d.net/articles/howbusmaster/3.sht ● Intel Quark SoC Datasheet

- 31. External links and References ● Intel ICH7 Datasheet ● Intel ICH5 Datasheet ● http://stackoverflow.com/questions/28868932/using ● National Instruments Application Note 011-DMA Fundamentals on Various PC Platforms ● http://zeus.nyf.hu/~bajalinov/OS/07/dma.pdf

- 32. Thanks