Exos de logique séquentielle

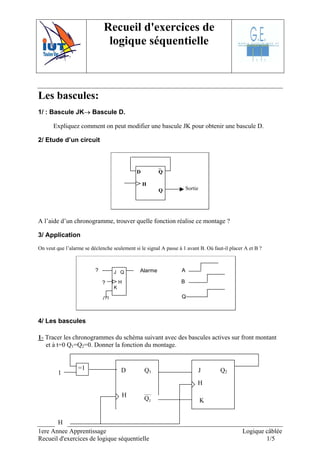

- 1. Recueil d'exercices de logique séquentielle Les bascules: 1/ : Bascule JK→ Bascule D. Expliquez comment on peut modifier une bascule JK pour obtenir une bascule D. 2/ Etude d’un circuit D Q H Q Sortie A l’aide d’un chronogramme, trouver quelle fonction réalise ce montage ? 3/ Application On veut que l’alarme se déclenche seulement si le signal A passe à 1 avant B. Où faut-il placer A et B ? ? J Q Alarme A ? H B K Q 4/ Les bascules 1- Tracer les chronogrammes du schéma suivant avec des bascules actives sur front montant et à t=0 Q1=Q2=0. Donner la fonction du montage. =1 D Q1 J Q2 1 H H Q1 K H 1ere Année Apprentissage Logique câblée Recueil d'exercices de logique séquentielle 1/5

- 2. U1 5/ Anti rebond VB Init Analysons le circuit ci-dessous. & VCC RA Quel est le rôle des deux résistors RA et RB ? Quelle est la fonction réalisée par les portes U1 et U2 ? RB Compléter les chronogrammes ci-dessous. & VA U2 VB 1 0 t VA 1 0 t Init 1 0 t / Init 1 0 t Conclure sur le rôle des portes U1 et U2. COMPTEURS-DECOMPTEUR 1/ Compteur asynchrone Réaliser un compteur asynchrone modulo 4 (0, 1, 2, 3, 0, 1, 2, 3) avec des bascules D. 2/ Décompteur asynchrone Réaliser un compteur asynchrone modulo 4 (0, 1, 2, 3, 0, 1, 2, 3) avec des bascules D front montant. 3/ Compteur asynchrone Réaliser un compteur asynchrone modulo 3 (1, 2, 3, 1,2,..) avec des bascules D. 4/ Décompteur asynchrone Réaliser un décompteur asynchrone modulo 4 (3,2,1,0,3,2,1,0,..) avec des bascules D. 4 bis/ Décompteur asynchrone Quelle modification apporter dans l’exercice Compt4 si les bascules sont des bascules JK ? 1ere Année Apprentissage Logique câblée Recueil d'exercices de logique séquentielle 2/5

- 3. 5/ Synthèse de compteur 1 : Réaliser la synthèse d’un compteur avec bascules JK sur front montant qui réalise la séquence 0→ 1→ 2→ 3→ 5→ 7 6/ Compteur-Décompteur On souhaite réaliser un circuit compteur décompteur à cycle complet, permettant de compter ou de décompter en binaire pur de 0 à 7. Pour commander le comptage, ou le décomptage, on utilise un signal D//U qui sera au 0 logique pour compter, et au 1 logique pour décompter. De plus, on dispose de bascules JK commandée sur front montant. 7/ Synthèse de compteurs modulo 5 1- Réaliser la synthèse d’un compteur synchrone modulo 5 avec bascules D sur front montant 2 - A partir du chronogramme des sorties des bascules et du signal d’horloge H, déterminer un signal dont la fréquence est égale à celle du signal H divisée par 5. 8/ Diviseur de fréquence par 16 puis par 10 1 - On vous demande de générer une horloge symétrique de 100 Hz. Vous disposez pour cela d’une fréquence d’horloge de 1600 Hz et de 6 bascules JK front montant. Il vous faut donc réaliser une division par 16 de la fréquence. Proposer un schéma simple en expliquant votre démarche. 2 - Vous disposez toujours de la même horloge et des mêmes bascules. On a maintenant besoin d’une horloge symétrique de fréquence de 160 Hz. Vous devez donc construire un diviseur de fréquence par 10. Proposez une solution et la réaliser. 9/ Compteur-Comparateur 1/ A l’aide de compteurs/décompteurs 191 créer un compteur binaire naturel 8 bits. 2/ A l’aide de comparateurs 85 créer un comparateur 8 bits. 3/ En utilisant les deux montages précédents, créer un montage qui permette, suite à l’action d’une commande /Init, de compter à partir de zéro tant que la valeur (8 bits) en sortie du compteur est inférieure à la consigne sur le comparateur. Une fois les deux valeurs égales, le compteur est inhibé et seule une nouvelle action sur /Init peut relancer un cycle. Ecrire le schéma de réalisation complet. 1ere Année Apprentissage Logique câblée Recueil d'exercices de logique séquentielle 3/5

- 4. /Init Consigne Sortie compteur Les Registres: 1/ Buffer 3bits Faire le schéma de réalisation d’un registre 3 bits à entrée parallèle sortie parallèle à base de bascules D actives sur front montant. 2/ Registre à décalage 3 bits Faire le schéma de réalisation d’un registre 3 bits à entrée série sortie série et parallèle à base de bascules D actives sur front montant. 3/ Synthèse d’un registre à décalage On se propose de bâtir un registre à décalage 3 bits à base de bascules D actives sur front montant répondant au cahier des charges suivant. LD/ SH est une entrée synchrone de ce registre. . LD/ SH Sorties 0 Décalage vers la droite 1 Chargement parallèle Soit M le mot de 3 bits en entrée parallèle. Soit Q le mot de 3 bits en sortie. Soit Es l’entrée série Un chargement parallèle signifie que suite au front significatif sur l’horloge Qi = Mi 1ere Année Apprentissage Logique câblée Recueil d'exercices de logique séquentielle 4/5

- 5. Un décalage vers la droite signifie que suite au front significatif sur l’horloge : Qi (n+1) = Qi-1 (n) Donner les équations de chaque entrée des bascules notées D0,D1,D2 Proposer un schéma de réalisation. 4/ Réalisation d’un sérialiseur/désérialiseur Pour transmettre de l’information entre deux systèmes informatisés on utilise la plupart du temps la transmission série. Dans ce type de transmission, les bits du mot sont transmis les uns à la suite des autres au rythme d’une horloge. Dans le système informatisé les informations circulent en parallèle (tous les bits du mot sont transmis en même temps), il sera donc nécessaire de faire une transformation parallèle/série (sérialisation) à l’émission et série/parallèle (désérialisation) à la réception. On se propose de faire cette opération sur 8 bits, le bit de poids faible étant transmis en premier. 1/ Etude du désérialiseur A l’aide de bascules D, faire le schéma de réalisation de cette fonction. 2/ Etude du sérialiseur On désire réaliser cette fonction à l’aide d’un MUX et d ‘un compteur. Donner les caractéristiques de ces composants. Faire le schéma de réalisation de cette fonction, le compteur sera à base de bascules JK 3/ Génération et vérification d’un bit de parité. On utilise le bit de parité paire comme code détecteur d ‘erreur. Les données sont sur 7 bits et le bit de parité occupera la position B7. Déterminer le bloc de logique combinatoire permettant de générer ce bit de parité à l’émission. Lors de la réception, le bit de parité est recalculé et comparé à celui reçu. Si ils diffèrent, un indicateur booléen prendra la valeur vrai. Donner le schéma de réalisation. 1ere Année Apprentissage Logique câblée Recueil d'exercices de logique séquentielle 5/5