Esercitazione Calcolatori Elettronici Vanadia 2007 12 06

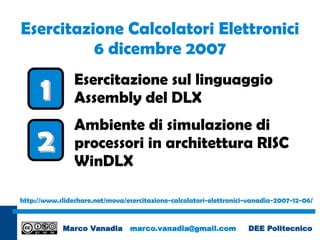

- 1. Esercitazione Calcolatori Elettronici 6 dicembre 2007 Esercitazione sul linguaggio 1 Assembly del DLX Ambiente di simulazione di 2 processori in architettura RISC WinDLX http://www.slideshare.net/mova/esercitazione-calcolatori-elettronici-vanadia-2007-12-06/ Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 2. Materiale da cercare in rete WinDLX ● pagina di Herbert Gruenbacher presso la Technische Universitat Wien http://www.soc.tuwien.ac.at/intern/RA/ http://cs.uns.edu.ar/~jechaiz/arquitectura/windlx/windlx.html http://cs.uns.edu.ar/~jechaiz/arquitectura/windlx/DLXinst.html Dinero IV Trace-Driven Uniprocessor Cache Simulator ● Mark Hill presso la University of Wisconsin http://www.cs.wisc.edu/~markhill/DineroIV/ EduMIPS64 ● porting italiano di WinMIPS64 da Visual C++ a Java Swing www.edumips.org http://www.opencores.org/projects.cgi/web/minimips/overview Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 3. Strumenti per la didattica Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 4. Assembly il linguaggio assembly è la rappresentazione simbolica che ● descrive le istruzioni e i dati per un computer il linguaggio macchina è la codifica binaria presente nella ● memoria ed elaborata dal processore L'assembly è più leggibile del linguaggio macchina perchè ● utilizza simboli piuttosto che bit. I simboli rappresentano sequenze di bit comuni per ● gli opcode, i codici mnemonici per rappresentare le istruzioni ➔ i registri ➔ le label che identificano le locazioni in memoria di istruzioni o ➔ dati Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 5. Struttura base codice sorgente Assembly commenti ; NomeProgramma.s ; autore ; versione direttiva inizio sezione dati .data definizione di tutti i dati e delle variabili direttiva che definisce .global main un etichetta globale .code offset direttiva inizio sezione codice istruzioni assembler entry point del codice assembly main: istruzioni assembler ferma il simulatore trap 0 Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 6. Direttive allineamento del codice e dei dati all'indirizzo successivo con i primi n bit meno significativi .align n posti a zero alloca le stringhe alfanumeriche nel codice oggetto che poi saranno caricate in memoria; le .ascii “string1”, “string2”, ... stringhe non sono terminate con il carattere zero alloca le stringhe alfanumeriche nel codice .asciiz “string1”, “string2”, oggetto che poi saranno caricate in memoria; le ... stringhe sono terminate con il carattere zero alloca una sequenza di byte nel codice oggetto .byte byte1, byte2,... che poi saranno caricate in memoria alloca una sequenza di double, numeri floating .double number1, number2,... point a doppia precisione di 64 bit nel codice oggetto che poi saranno caricate in memoria alloca una sequenza di float, numeri floating .float number1, number2,... point a singola precisione di 32 bit nel codice oggetto che poi saranno caricate in memoria definisce una etichetta come globale, un .global label riferimento a questa locazione è disponibile ad altri codici oggetto linkato a questo sorgente lascia lo spazio per size bytes quando il codice .space size sarà caricato in memoria Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 7. Assemblatore Linker Loader Un programma in linguaggio assembly è codificato in un file oggetto ● usando un programma assemblatore. Un assemblatore legge un singolo file sorgente e produce il file oggetto assemblando tutte le informazioni necessarie a descrivere il codice e i dati. Queste verranno poi messe assieme da un linker a formare un programma eseguibile o una libreria, caricati in memoria da un loader all'atto dell'esecuzione o invocazione. Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 8. Codice rilocabile Il file oggetto comincia con un'intestazione, un ● header, ed è formato da uno o più segmenti contenenti il codice macchina e la rappresentazione binaria dei dati. Vengono salvate le informazioni sulla rilocazione per le parole che dipendono dall'indirizzo assoluto in memoria in cui è caricato ogni segmento. Inoltre viene salvata la symbol table delle label che ● possono essere indirizzate da altri file sorgente e la lista di tutti i riferimenti esterni irrisolti. Per finire possono esservi informazioni di debugging. Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 9. Esercizio Assembly #1 Scrivere, nel linguaggio Assembly del DLX ● scalare, l’inizializzazione a valore nullo di un vettore composto da N elementi interi di una sola word. for (i=0; i<N; i++) { x[i] = 0; } Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 10. Esercizio Assembly #1 SUB R0, R0, R0 ; 0 -> R0 ADD R3, R0, R0 ; 0 -> R3 ADD R2, R0, N ; N -> R2 loop: SW R1, R3, F2 ; 0 -> M[R1+R3] ADD R3, R3, #4 ; R3 + 4 -> R3 SUB R2, R2, #1 ; R2 - 1 -> R2 JNZ loop ; se R2 > 0 salta a loop Sia R0 il registro nullo ● R1 il registro base (contenente il primo indirizzo di allocazione in memoria del ● vettore) R2 il registro contenente il numero di elementi del vettore da inizializzare ● R3 il registro indice che punta ai singoli elementi del vettore in memoria ● Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 11. Esercizio Assembly #1 SUB R0, R0, R0 ADD R3, R0, R0 ADD R2, R0, N -> LW R2, N loop: SW R1, R3, F2 -> SW vett(R3), R0 ADD R3, R3, #4 SUB R2, R2, #1 JNZ loop -> BNEZ R2, loop R0 vale sempre zero ● per caricare il valore di una parola all'etichetta N si usa LW Rx, N ● la SW (I-type) ha un indirizzamento indirizzo base + spiazzamento 16bit ● il branch richiede un registro per una condizione di == o <> da zero ● Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 12. Esercizio Assembly #1 ; asm1_1.s ADD R3, R0, R0 ; imposta a zero l'indice R3 LW R2, N ; carica N in R2 loop: SW vettore(R3),R0 ; pone 0 alla locazione M[R3 + vettore] ADDI R3, R3, #4 ; incrementa l'indice di 4 ogni word SUBI R2, R2, #1 ; decrementa il contatore BNEZ R2, loop ; salta a loop se non uguale a zero trap 0 ; per fermare windlx .data .word 8 N: .word 1,2,3,4,5,6,7,8 vettore: Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 13. Esercizio Assembly #1 N: 8 0x1000 x[0] = 1 vettore: 0x1004 x[1] = 2 0x1008 x[2] = 3 0x100c x[3] = 4 0x1010 x[4] = 5 0x1014 x[5] = 6 0x1018 x[6] = 7 0x101c 0x1020 x[7] = 8 Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 14. Esercizio Assembly #1 ; asm1_2.s LW R2, N ; carica N in R2 SLLI R2, R2, #2 ; moltiplico per 4 shiftando a sx di 2 loop: SW vettore-4(R2),R0 ; pone 0 alla M[R2 + (vettore-4)] SUBI R2, R2, #4 ; uso R2 come indice e decremento di 4 BNEZ R2, loop ; salta a loop se non uguale a zero trap 0 ; per fermare windlx .data N: .word 8 vettore:.word 1,2,3,4,5,6,7,8 Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 15. Esercizio Assembly #1 N: 8<<2 = 32 8 0x1000 vettore + 0 x[0] = 1 vettore: 0x1004 vettore + 4 x[1] = 2 0x1008 vettore + 8 x[2] = 3 0x100c x[3] = 4 0x1010 vettore + 12 x[4] = 5 0x1014 vettore + 16 x[5] = 6 0x1018 vettore + 20 x[6] = 7 0x101c vettore + 24 0x1020 x[7] = 8 vettore + 28 vettore + 32 Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 16. Esercizio Assembly #7 Scrivere nel linguaggio Assembly di una ● architettura DLX-like scalare (non pipe), la procedura che esegue la somma di due vettori di n elementi interi, espressi su singola word, allocati in memoria a partire dagli indirizzi rispettivamente contenuti negli registri R1 ed R2, ponendo il risultato a partire dall'indirizzo contenuto nel registro R3. for (i=0; i<N; i++) { z[i] = x[i] + y[i]; } Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 17. Esercizio Assembly #7 .text .text lw r4, length lw r4, length slli r4, r4, #2 slli r4, r4, #2 add r1, r4, v1 add r2, r4, v2 add r3, r4, v3 loop: beqz r4, end loop: beqz r4, end lw r5, v1-4(r4) lw r5, -4(r1) lw r6, v2-4(r4) lw r6, -4(r2) subi r4, r4, #4 ; schedulata add r5, r5, r6 add r5, r5, r6 sw v3(r4), r5 ; (indirizzo-4)+4 sw -4(r3), r5 subi r4, r4, #4 subi r1, r1, #4 subi r2, r2, #4 subi r3, r3, #4 subi r4, r4, #4 j loop j loop end: trap 0 end: trap 0 .data .data v1: .word 1,-1, 0,-1 v1: .word 1,-1, 0,-1 v2: .word 2, 0, 1, 1 v2: .word 2, 0, 1, 1 v3: .space 4*4 v3: .space 4*4 length: .word 4 length: .word 4 Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 18. Esercizio Architetture Avanzate #1 Dire quale è lo scopo del seguente programma: loop: LD F0, 0(R1) ADDD F4, F0, F2 SD 0(R1), F4 ADDI R1, R1, #-8 BNEZ R1, loop e fornire una sua versione srotolata per 6 volte schedulata in maniera opportuna. vedi H&P pag.271 (par.6.8 pipelining avanzato ILP, srotolamento e schedulazione) Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 19. Pipelining avanzato ILP Instruction-level parallelism le pipeline sono state sviluppate per poter eseguire ● contemporaneamente più istruzioni indipendenti Pipeline CPI = Ideal pipeline CPI + Structural stalls + ● RAW stalls + WAR stalls + WAW stalls + Control stalls tecniche per ridurre gli stalli ● Loop unrolling – per gli stalli di controllo ● Pipeline scheduling – riduce gli stalli RAW ● Register renaming – riduce gli stalli WAR e WAW ● Dynamic branch prediction – per gli stalli di controllo ● Superscalar pipeline – riduce CPI ideale ● Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 20. Esercizio Architetture Avanzate #1 loop: LD F0, 0(R1) ADDD F4, F0, F2 for(int i=1;i<=N;i++) { SD 0(R1),F4 x[i]=x[i] + c; ADDI R1, R1, #-8 } BNEZ R1, loop somma un valore scalare double agli elementi di un vettore di double in memoria R1 contiene l'indirizzo dell'elemento del vettore con l'indirizzo più alto in memoria F2 contiene il valore dello scalare c da sommare N.B. non viene caricato l'elemento all'indirizzo zero... Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 21. Stalli della pipeline loop: LD F0, 0(R1) stallo ADDD F4, F0, F2 stallo stallo SD 0(R1), F4 ADDI R1, R1, #-8 5 ISTRUZIONI stallo 10 CICLI BNEZ R1, loop CPI = 2 stallo Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 22. Scheduling loop: LD F0, 0(R1) loop: LD F0, 0(R1) ADDI R1, R1, #-8 stallo ADDD F4, F0, F2 ADDD F4, F0, F2 stallo stallo BNEZ R1, loop stallo SD 8(R1), F4 SD 0(R1), F4 ADDI R1, R1, #-8 5 ISTRUZIONI stallo 6 CICLI BNEZ R1, loop CPI = 1,2 stallo la LD causa stallo strutturale nella fase MEM per la dipendenza con la EXE di ADDD ● ● la ADDD causa un doppio stallo RAW per la dipendenza con SD ● la ADDI causa uno stallo RAW per la dipendenza con la fase ID del branch ● il branch quando salta indietro richiede uno stallo di controllo schedulo l'aggiornamento dell'indice nel delay slot della load ● ● schedulo la store del risultato nel delay slot della branch (non previsto da WinDLX) ● la store dipende da R1 ma sfruttare il campo immediato per avere l'indirizzo corretto Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 23. Loop unrolling loop: LD F0, 0(R1) loop: LD F0, 0(R1) ;1 ADDD F4, F0, F2 SD 0(R1), F4 ADDD F4, F0, F2 LD F6, -8(R1) ;2 SD 0(R1), F4 ADDD F8, F6, F2 SD -8(R1), F8 ADDI R1, R1, #-8 LD F10, -16(R1) ;3 BNEZ R1, loop ADDD F12, F10, F2 SD -16(R1), F12 LD F14, -24(R1) ;4 ADDD F16, F14, F2 SD -24(R1), F16 LD F18, -32(R1) ;5 ADDD F20, F18, F2 SD -32(R1), F20 LD F22, -40(R1) ;6 ADDD F24, F22, F2 20 ISTRUZIONI SD -40(R1), F24 6*6+4 = 40 CICLI ADDI R1, R1, #-48 CPI = 2 BNEZ R1, loop Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 24. Unrolled & scheduled loop: LD F0, 0(R1) ;1 loop: LD F0, 0(R1) ; 1 ADDD F4, F0, F2 LD F6, -8(R1) ; 2 SD 0(R1), F4 LD F10, -16(R1) ; 3 LD F14, -24(R1) ; 4 LD F6, -8(R1) ;2 LD F18, -32(R1) ; 5 ADDD F8, F6, F2 LD F22, -40(R1) ; 6 SD -8(R1), F8 ADDD F4, F0, F2 ; 1 LD F10, -16(R1) ;3 ADDD F8, F6, F2 ; 2 ADDD F12, F10, F2 ADDD F12, F10, F2 ; 3 SD -16(R1), F12 ADDD F16, F14, F2 ; 4 ADDD F20, F18, F2 ; 5 LD F14, -24(R1) ;4 ADDD F24, F22, F2 ; 6 ADDD F16, F14, F2 SD -24(R1), F16 SD 0(R1), F4 ; 1 SD -8(R1), F8 ; 2 LD F18, -32(R1) ;5 SD -16(R1), F12 ; 3 ADDD F20, F18, F2 SD -24(R1), F16 ; 4 SD -32(R1), F20 SD -32(R1), F20 ; 5 LD F22, -40(R1) ;6 ADDI R1, R1, #-48 ADDD F24, F22, F2 SD -40(R1), F24 BNEZ R1, loop 20 ISTRUZIONI SD 8(R1), F24 ;6 ADDI R1, R1, #-48 6+3*6+6+1+1= 32 CICLI BNEZ R1, loop ;asm1_3 CPI = 1,6 ;asm1_2 Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 25. Cicli arc1_0 246 arc1_1 198 arc1_2 166 CYC arc1_3 134 arc1_4 106 0 50 100 150 200 250 300 WinDLX istruzioni utili / stalli stats arc1_0 68% 26% 6% arc1_1 74% 18% 9% CONTR STRUT arc1_2 68% 31% 1% WAW TOT RAW TOT arc1_3 76% 23% 2% CYC arc1_4 88% 10% 2% 0,00% 20,00% 40,00% 60,00% 80,00% 100,00% Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 26. Architettura Superscalare istruzione ALU istruzione FP 1 loop: LD F0, 0(R1) 2 LD F6, -8(R1) 3 LD F10, -16(R1) ADDD F4, F0, F2 4 LD F14, -24(R1) ADDD F8, F6, F2 5 LD F18, -32(R1) ADDD F12, F10, F2 6 LD F22, -40(R1) ADDD F16, F14, F2 7 SD 0(R1), F4 ADDD F20, F18, F2 8 SD -8(R1), F8 ADDD F24, F22, F2 9 SD -16(R1), F12 10 SD -24(R1), F16 11 ADDI R1, R1, #-48 12 SD 16(R1), F20 20 ISTRUZIONI 13 BNEZ R1, loop 14 CICLI 14 SD 8(R1), F24 CPI = 0,7 Marco Vanadia marco.vanadia@gmail.com DEE Politecnico

- 27. Architettura VLIW istruzione Rif M1 Rif M2 istruz FP1 istruz FP2 ALU/Branch 1 LD F0, 0(R1) LD F6, -8(R1) 2 LD F10,-16(R1) LD F14,-24(R1) 3 LD F18,-32(R1) LD F22,-40(R1) ADDD F4, F0,F2 ADDD F8, F6, F2 4 ADDD F12,F10,F2 ADDD F16,F14, F2 5 SD 0(R1), F4 SD -8(R1), F8 ADDD F20,F18,F2 ADDD F24, F22, F2 6 SD -16(R1), F12SD -24(R1), F16 ADDI R1,R1,#-48 7 SD 16(R1), F20 SD 8(R1), F24 BNEZ R1, loop 8 nop nop nop nop nop istruzione Rif M1 Rif M2 istruz FP1 istruz FP2 ALU/Branch 1 LD F0, 0(R1) LD F6, -8(R1) 2 LD F10,-16(R1) LD F14,-24(R1) 3 LD F18,-32(R1) LD F22,-40(R1) ADDD F4, F0,F2 ADDD F8, F6, F2 4 ADDD F12,F10,F2 ADDD F16,F14, F2 5 SD 0(R1), F4 SD -8(R1), F8 ADDD F20,F18,F2 ADDD F24, F22, F2 ADDI R1,R1,#-48 6 SD 32(R1), F12 SD 24(R1), F16 BNEZ R1, loop 20 ISTRUZIONI 7 SD 16(R1), F20 SD 8(R1), F24 (delay slot) 7 CICLI CPI = 0,35 Marco Vanadia marco.vanadia@gmail.com DEE Politecnico