Sistemas electronicos digitales

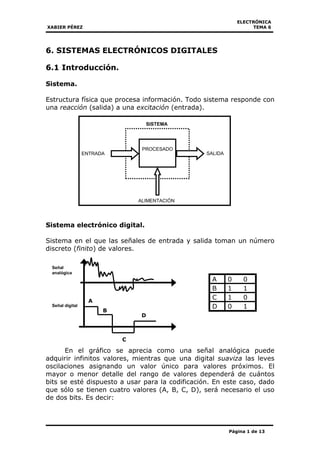

- 1. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 1 de 13 6. SISTEMAS ELECTRÓNICOS DIGITALES 6.1 Introducción. Sistema. Estructura física que procesa información. Todo sistema responde con una reacción (salida) a una excitación (entrada). Sistema electrónico digital. Sistema en el que las señales de entrada y salida toman un número discreto (finito) de valores. En el gráfico se aprecia como una señal analógica puede adquirir infinitos valores, mientras que una digital suaviza las leves oscilaciones asignando un valor único para valores próximos. El mayor o menor detalle del rango de valores dependerá de cuántos bits se esté dispuesto a usar para la codificación. En este caso, dado que sólo se tienen cuatro valores (A, B, C, D), será necesario el uso de dos bits. Es decir: A 0 0 B 1 1 C 1 0 D 0 1 PROCESADO ENTRADA ALIMENTACIÓN SALIDA SISTEMA Señal analógica Señal digital A B C D

- 2. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 2 de 13 2n = número de combinaciones posibles entre n bits No existe una codificación única, de forma que la propuesta sería tan válida como cualquier otra. Sistema lógico. Caso particular de los sistemas digitales. Sólo toma dos valores: 0 y 1 SISTEMA BINARIO Sistemas Analógicos Vs. Sistemas Digitales. Analógicos: mejores prestaciones de velocidad o potencia. Digitales: menos sujetos a errores y variaciones paramétricas. Mayor flexibilidad. Sin embargo, se alimentan de magnitudes analógicas, lo que conlleva una pérdida de información irrecuperable al hacer la conversión analógica-digital. A mayor número de bits en la conversión menor pérdida de información. SISTEMA DIGITAL N bits M bits N bits M bits SISTEMA LÓGICO 2 bits2 bits DECODCOD SISTEMA DIGITALN bits M bits A/D D/A Analógico

- 3. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 3 de 13 Sistemas Combinacionales. Son aquellos sistemas que no tienen memoria, entendiéndose como memoria la imposibilidad de recordar eventos anteriores al actual. Ejemplo de sistema combinacional: AIRBAG Se supone que un airbag salta en un coche cuando se produce una desaceleración lo suficientemente pronunciada como para activar el mecanismo. Además, en función de cómo de rápida haya sido la desaceleración, la bolsa del aibag se infla más o menos para que el grado de amortiguación sea el adecuado para el impacto. El hecho de que el airbag salte cuando se produce una situación de riesgo es independiente de que con anterioridad se hayan producido otras. Es decir, el airbag saltará siempre que sea necesario y no tendrá en cuenta cuándo fue la última vez tuvo que usarse. Sistemas Secuenciales. Son aquellos sistemas que tienen memoria, entendiéndose como memoria la posibilidad de recordar eventos anteriores al actual. El sistema no requiere necesariamente que recuerde el histórico de eventos, sino sólo los inmediatamente anteriores (habitualmente, sólo recuerda el evento anterior). X Y A OFF B OFF C ON D ON E OFF Supongamos que X (entrada) adquiere cinco posibles valores que han de provocar la reacción de Y (salida). La descripción del sistema podría hacerse mediante una tabla de verdad (TdV). ACELERÓMETRO x SISTEMA COMBINACIONAL AIRBAG y SISTEMA COMBINACIONAL x y = f(x) SISTEMA SECUENCIAL xi z = f(xi, xi-1, xi-2,...) Analógico

- 4. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 4 de 13 Ejemplo de sistema secuencial: ASCENSOR Se supone un ascensor en un edificio de tres plantas (segunda planta, primera planta y planta baja). El sistema ha de modelar el hecho de que un usuario pueda llamar al ascensor desde cualquiera de las tres plantas e, independientemente de dónde se encuentre en ese momento, el ascensor acuda. Para ello es necesario definir: Una variable que indique desde qué planta el usuario llama al ascensor X. Una variable de estado que indique en qué planta se haya el ascensor, es decir, que recuerde dónde se quedó el ascensor tras el trayecto inmediatamente anterior S. Una variable de salida que, en función de la combinación de las variables anteriores, le indique al ascensor cuántas plantas debe subir o bajar Z. Variable Descripción Rango de valores x Piso desde el que se llama al ascensor 0, 1, 2 s Piso en el que se encuentra el ascensor 0, 1, 2 z Número de plantas que ha de desplazarse el ascensor para acudir a la llamada -2, -1, 0, 1, 2 X S Z 0 0 0 0 1 -1 0 2 -2 1 0 1 1 1 0 1 2 -1 2 0 2 2 1 1 2 2 0 BOTONERA ASCENSOR x SISTEMA SECUENCIAL MOTOR ASCENSOR z=f(x,s)s Como indica la tabla de verdad, si el usuario llama al ascensor desde la planta (x = 1), y el ascensor se encuentra en la planta baja (s = 0), la orden al motor será la de subir un piso (z = 1).

- 5. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 5 de 13 Optimización. 6.2 Sistemas de numeración. Entre otros BCD, Binario, Octal y Hexal. Explicados en el archivo Sistemes de Numeració.pdf colgado en el Campus. 6.3 Sistemas de codificación. Codificación. Una codificación ha de permitir escribir en valores binarios una combinación digital. Asigna una secuencia binaria de dimensión N a cada elemento de un conjunto finito. {CONJUNTO} {0,1}N Las codificaciones son arbitrarias. No existe una codificación única. Sin embargo, sí se ha de ser coherente eligiendo la codificación en función del posterior diseño e implementación del circuito. Retomando el ejemplo del AIRBAG, dado que existen cinco posibles valores para la entrada, hará falta el uso de tres bits para su codificación (con dos bits sólo se podrían codificar cuatro combinaciones). X COD1 A 001 B 010 C 110 D 101 E 000 X COD2 A 000 B 001 C 010 D 011 E 100 ESPECIFICACIÓN DiseñoAnálisis IMPLEMENTACIÓN En el diseño de un circuito no existe una implementación óptima. Distintos circuitos pueden responder satisfactoriamente a un mismo fin. Sin embargo, se ha de elegir el que cumpla con el criterio de optimización marcado. Esta codificación es válida, aunque posiblemente sea más útil establecer una relación de orden de menor a mayor:

- 6. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 6 de 13 Tipos de código. Binario, octal, hexal. BCD. Codifica las cifras decimales: (951)10 = (100101010001)BCD Códigos de Gray (cíclicos). Tienen como característica que entre codificaciones consecutivas sólo varía un bit. Para su construcción se usa el principio de reflexión: se usa la codificación de Gray de un bit menos, extendiéndola sobre sí misma como si se reflejara en un espejo; finalmente se completa la columna para el nuevo bit rellenando dos mitades con ceros y unos consecutivos. Códigos Redundantes. Estos códigos permiten la detección y corrección de errores. Tienen más bits de los estrictamente necesarios para realizar la codificación. Los bits excedentes se usan como clave para la detección de los errores. # CODN=2 0 0 0 1 0 1 2 1 1 3 1 0 # COD N=3 0 0 0 0 1 0 0 1 2 0 1 1 3 0 1 0 4 1 1 0 5 1 1 1 6 1 0 1 7 1 0 0 # COD N=4 0 0 0 0 0 1 0 0 0 1 2 0 0 1 1 3 0 0 1 0 4 0 1 1 0 5 0 1 1 1 6 0 1 0 1 7 0 1 0 0 8 1 1 0 0 9 1 1 0 1 10 1 1 1 1 11 1 1 1 0 12 1 0 1 0 13 1 0 1 1 14 1 0 0 1 15 1 0 0 0 reflexión reflexión

- 7. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 7 de 13 Bits de menor peso Bits de mayor peso Ejemplo. Bit de paridad detecta un número impar de unos 6.4 Mapa de Karnaugh (MdK). Permite la representación del comportamiento del sistema, ya recogido en la tabla de verdad, en una tabla ordenada según la codificación de Gray. Fijada una celda de la tabla, serán celdas adyacentes aquéllas que sólo difieren en un bit en la codificación. Modelo de construcción de MdK para cuatro variables de entrada. # Binario base 3 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1 # Binario base 3 con exceso 0 0 0 0 0 1 1 0 0 1 2 1 0 1 0 3 0 0 1 1 4 1 1 0 0 5 0 1 0 1 6 0 1 1 0 7 1 1 1 1 x x3 x2 x1 x0 f(x) 0 0 0 0 0 f(0000) 1 0 0 0 1 f(0001) 2 0 0 1 0 f(0010) 3 0 0 1 1 f(0011) 4 0 1 0 0 f(0100) 5 0 1 0 1 f(0101) 6 0 1 1 0 f(0110) 7 0 1 1 1 f(0111) 8 1 0 0 0 f(1000) 9 1 0 0 1 f(1001) 10 1 0 1 0 f(1010) 11 1 0 1 1 f(1011) 12 1 1 0 0 f(1100) 13 1 1 0 1 f(1101) 14 1 1 1 0 f(1110) 15 1 1 1 1 f(1111) x1 x0 x3 x2 00 01 11 10 0 0 f(0000) f(0001) f(0011) f(0010) 0 1 f(0100) f(0101) f(0111) f(0110) 1 1 f(1100) f(1101) f(1111) f(1110) 1 0 f(1000) f(1001) f(1011) f(1010) Las celdas sombreadas en tonos más claros, son adyacentes de las sombreadas en tonos más oscuros

- 8. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 8 de 13 y1 y0 Ejemplo. Sistema que cuenta los unos que entran Hay tres entradas que codifican en rango de valores del 0 al 7. El rango de valores que puede tomar la salida Y va del 0 al 3, cuatro combinaciones, con lo que harán falta dos bits para la codificación (y1, y0) x x2 x1 x0 y y1 y0 0 0 0 0 0 0 0 1 0 0 1 1 0 1 2 0 1 0 1 0 1 3 0 1 1 2 1 0 4 1 0 0 1 0 1 5 1 0 1 2 1 0 6 1 1 0 2 1 0 7 1 1 1 3 1 1 x1 x0 x2 00 01 11 10 0 0 1 0 1 1 1 0 1 0 6.5 Funciones Lógicas. Una función establece una relación, según el criterio marcado por el sistema, entre las entradas y las salidas. Si el sistema tiene N entradas, la salida tendrá que contemplar una respuesta para 2N combinaciones posibles, que darán (2N )2 funciones diferentes. Entradas Combinaciones Funciones N 2N (2N )2 1 2 4 2 4 16 x1 x0 x2 00 01 11 10 0 0 0 1 0 1 0 1 1 1 Cuenta # de 1’s y( y1,y0)x (x2,x1,x0)

- 9. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 9 de 13 6.6 Funciones Lógicas Habituales. Caso N = 1 A F0 F1 F2 F3 0 0 0 1 1 1 0 1 0 1 Caso N = 2 A B F0 F1 F2 F3 F4 F5 F6 F7 F8 F9 F10 F11 F12 F13 F14 F15 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Las funciones sombreadas en azúl permiten descubrir nuevas funciones lógicas básicas. F0 Tierra F0(A) = 0 F1 Identidad F1(A) = A F2 Negación/ inversión F2(A) = A F3 Constante Alimentación F3(A) = 1 F Nombre Símbolo Clave Expresión F1(A,B) AND Producto sale 1 si sólo entran 1’s F1(A,B) = A·B F14(A,B) NAND Sale 0 si sólo entran 0’s F14(A,B) = B·A F7(A,B) OR suma lógica Sale 1 si entra al menos un 1 F7(A,B) = A+B F8(A,B) NOR Sale 1 si sólo entran ceros F8(A,B) = B+A F6(A,B) XOR Suma exclusiva Sale 1 si entra número impar de 1’s F6(A,B) = BA ⊕ F9(A,B) XNOR Sale 1 si entran número par de 1’s F9(A,B) = BA ⊕ F( . ) A F(A)

- 10. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 10 de 13 TdV Z MdK Las funciones sombreadas en gris son análogas a las encontradas para el caso anterior (N = 1). Las funciones que están en blanco son combinación de las funciones ya identificadas. 6.7 Composición de Funciones. Mezclando la funciones básicas (AND, OR, NAND,...) se forman funciones complejas. Las funciones pueden representarse de cuatro formas equivalentes entre ellas: Expresión, Tabla de Verdad, Mapa de Karnaugh y Logigrama. Un logigrama es la representación gráfica a partir de la interconexión de los símbolos de las funciones básicas. Ejemplo. Representación de una función A B C D DBCE = Z 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 1 1 0 1 1 0 1 1 1 0 0 1 0 0 0 0 1 1 0 0 1 0 1 1 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 1 1 1 1 1 1 0 1 C D A B 00 01 11 10 0 0 0 0 0 0 0 1 0 0 0 1 1 1 1 1 1 1 1 0 1 1 1 1 LOGIGRAMA MdKTdV EXPRESIÓN diseño DBCA)B,A(F += A B C D Z E Expresión Logigrama

- 11. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 11 de 13 F1 Habitualmente, y según la complejidad del logigrama o de la expresión, se suelen crear variables intermedias para facilitar su análisis. Ejemplo. Encontrar las otras representaciones a partir del logigrama El sistema tiene tres entradas (A, B, y C) una salida (F1). Para el análisis se crean tres variables intermedias (D, E y G). Se hace el recorrido de delante a atrás: Se identifican D, E y G: Se substituyen D, E y G en F1: Se rellena la TdV a partir de la expresión, usando las variables intermedias: Finalmente se rellena el MdK: A B C D E G F1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 1 1 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 1 1 0 0 1 1 1 0 0 0 1 1 1 1 1 1 0 0 1 B C A 00 01 11 10 0 0 0 0 1 1 1 1 1 1 A C B F1 D E G GEDF1 ++= C·BG C·B·AE ACD = = = C·BC·B·AACF1 ++= F1

- 12. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 12 de 13 Ejemplo. Encontrar las otras representaciones a partir del logigrama Siguiendo el procedimiento del ejemplo anterior, se encuentra la expresión, la TdV y el MdK: En los dos ejemplos, F1 y F2 dan la misma TdV y el mismo MdK. Eso es así porque distintas implementaciones pueden responder a idénticas necesidades. Para evitar diseños no óptimos, como el del primer ejemplo, se ha de conocer la Algebra de Boole y/o las formas de análisis del MdK que ofrecen las implementaciones más optimizadas. A B C D F2 0 0 0 0 0 0 0 1 0 0 0 1 0 1 1 0 1 1 0 0 1 0 0 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 0 1 B C A 00 0 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 B F2 D C A DAF +=2 CBAF ·2 += CBD ·= F2

- 13. ELECTRÓNICA XABIER PÉREZ TEMA 6 Página 13 de 13 6.8 Funciones Incompletamente Especificadas. Son aquéllas que ofrecen libertad en la codificación de determinados valores de entrada. Se propone un ejemplo para estudiarlo. Ejemplo. Detector de 5 en dado electrónico. La salida y sólo contempla dos valores: 1 ó 0 Pero las inespecificaciones (las ‘X’s) pueden ser de utilidad para el diseño del circuito. Como jamás se producirán, podemos asignarle el valor (0 ó 1) que más nos convenga para conseguir una implementación más óptima. Se han planteado dos casos: Se observa que la implementación Y1 resulta óptima respecto la Y0. A B C y 0 0 0 X 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 X A B C Y0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 0 A B C Y1 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 1 5? A B C y CBAY ··0 = Y0 De las características del dado se extrae que existen dos codificaciones que nunca ocurrirán: la del CERO y la del SIETE. En la TdV se pondrá una X para recalcar que las salidas para estos valores jamás se producirán dado que estos valores nunca se pueden manifestar como entradas. Un dado presenta 6 caras con los valores del 1 al 6. Para codificar estas 6 posibilidades hará falta tres bits: A, B, C. CAY ·1 = Y1 A C A B C