xilinx fpga problems

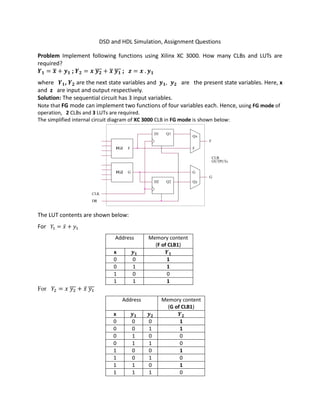

- 1. DSD and HDL Simulation, Assignment Questions Problem Implement following functions using Xilinx XC 3000. How many CLBs and LUTs are required? 𝒀 = 𝒙̅ + 𝒚 ; 𝒀 = 𝒙 𝒚̅̅̅ + 𝒙̅ 𝒚̅̅̅ ; 𝒛 = 𝒙 . 𝒚 where 𝒀 , 𝒀 are the next state variables and 𝒚 , 𝒚 are the present state variables. Here, x and z are input and output respectively. Solution: The sequential circuit has 3 input variables. Note that FG mode can implement two functions of four variables each. Hence, using FG mode of operation, 2 CLBs and 3 LUTs are required. The simplified internal circuit diagram of XC 3000 CLB in FG mode is shown below: The LUT contents are shown below: For = ̅ + Address Memory content (F of CLB1) x 𝒚 𝒀 0 0 1 0 1 1 1 0 0 1 1 1 For = ̅̅̅ + ̅ ̅̅̅ Address Memory content (G of CLB1) x 𝒚 𝒚 𝒀 0 0 0 1 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 1 1 1 1 0 DR CLB OUTPUTs G FG1 F Qy CLK GFG2 Q2 D1 F D2 G Q1 Qx F

- 2. For 𝑧 = . Address Memory content (F of CLB2) x 𝒚 𝒀 0 0 0 0 1 0 1 0 0 1 1 1 Circuit implementation using two XC3000 CLBs is shown below: ----------------------------------------------------------------------------------------------------------------------------------------- Problem Consider a 2 bit magnitude comparator to compare 𝐴 𝐴 and 𝐵 𝐵 to define three outputs A>B, A<B, A=B and map it using Xilinx XC 3000 FPGA. How many CLBs and LUTs are required? Show the contents of sRAM cell Solution: Consider the truth table for output A=B Y1 Q1 D2 Q1 Q2 Q2 DR G y1 CLK G G F Y2 G z FG2 FG1 CLB 2 x Qx y1 Qy DR x y1 CLB 1 y2 D2 FG1 F x F FG2 CLK Qy D1 D1 F Qx

- 3. 𝐴 𝐴 𝐵 𝐵 EQ 0 0 0 0 1 0 1 0 1 1 1 0 1 0 1 1 1 1 1 1 Design equation for EQ is 𝐸𝑄 = 𝐴̅̅̅ 𝐴̅̅̅ 𝐵̅̅̅ 𝐵̅̅̅ + 𝐴̅̅̅ 𝐴 𝐵̅̅̅ 𝐵 + 𝐴 𝐴̅̅̅ 𝐵 𝐵̅̅̅ + 𝐴 𝐴 𝐵 𝐵 Consider the truth table for output A>B 𝐴 𝐴 𝐵 𝐵 A>B 1 X 0 X 1 0 1 0 0 1 1 1 1 0 1 The corresponding implicant table is 𝐴 𝐴 𝐵 𝐵 A>B 1 X 0 X 1 X 1 0 0 1 1 1 X 0 1 Design equation for A>B is 𝐴 > 𝐵 = 𝐴 𝐵̅̅̅ + 𝐴 𝐵̅̅̅ 𝐵̅̅̅ + 𝐴 𝐴 𝐵̅̅̅ Consider the truth table for output A<B 𝐴 𝐴 𝐵 𝐵 A<B 0 X 1 X 1 0 0 0 1 1 1 0 1 1 1 The corresponding implicant table is 𝐴 𝐴 𝐵 𝐵 A<B 0 X 1 X 1 0 0 X 1 1 X 0 1 1 1 Design equation for A<B is 𝐴 < 𝐵 = 𝐴̅̅̅ 𝐵 + 𝐴̅̅̅. 𝐴̅̅̅̅. 𝐵 + 𝐴̅̅̅̅ 𝐵 𝐵

- 4. 2 bit magnitude comparator has 4 input variables and 3 outputs. The circuit implementation using XC 3000 in FG mode requires 2 CLBs and 3 LUTs. Circuit implementation using two XC3000 CLBs is shown below: The LUT (LUT1 and LUT2 of two CLBs) contents are given below: G A0 B1 LUT1 FG mode B0 F F A0 Qy Qy B1 CLK CLK G A>B G A1 A=B B1 Q2 Q2 A<B B0 D1 D1 A1 D2 D2 A0 Q1 Q1 B0 Qx Qx LUT2 F F FG mode DR CLB 1 LUT1 CLB 2 DR A1 LUT2 G

- 5. Address Memory content (F of CLB1) Memory content (G of CLB1) Memory content (F of CLB2) > = < 0 0 0 0 0 1 0 0 0 0 1 0 0 1 0 0 1 0 0 0 1 0 0 1 1 0 0 1 0 1 0 0 1 0 0 0 1 0 1 0 1 0 0 1 1 0 0 0 0 0 1 1 1 0 0 0 1 0 0 0 1 0 0 1 0 0 1 1 0 0 1 0 1 0 0 1 0 1 0 1 1 0 0 1 1 1 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 0 1 0 0 1 1 1 1 0 1 0 ------------------------------------------------------------------------------------------------------------------------------ Problem Implement following function using Xilinx XC 3000. How many CLBs and LUTs are required? F(a, b, c, d, e) = a. b. c + a. b̅. c + e̅ + d. e Solution: The output function has 5 input variables. The circuit implementation using XC 3000 in F mode (Note that F mode can generate one function of five variables) requires 1 CLB and 1 LUT. Problem Implement 2421 to 8421 code converter using Xilinx XC 3000. How many CLBs and LUTs are required? Show the contents of the sRAM cell. Dr. D. V. Kamath Professor, Dept. of E&C Engg., MIT LUT F F G b e Q2 DR CLB 1 Qy CLK D1 F F Qx Q1 G a D2 c d F mode