work order of logic laboratory

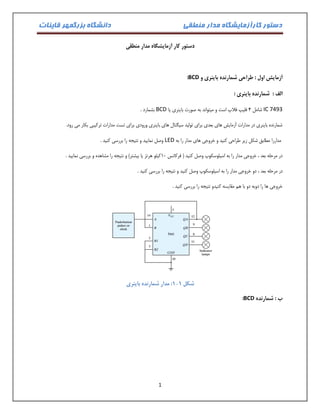

- 1. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 1 دستور کار آزمایشگاه مدار منطقی آزمایش اول : طراحی شمارنده باینری و BCD : الف : شمارنده باینری : IC 7493 شامل 4 فلیپ فلاپ است و میتواند به صورت باینری یا BCD بشمارد . شمارنده باینری در مدارات آزمایش های بعدی برای تولید سیگنال های باینری ورودی برای تست مدارات ترکیبی بکار می رود. مداررا مطابق شکل زیر طراحی کنید و خروجی های مدار را به LED وصل نمایید و نتیجه را بررسی کنید . در مرحله بعد ، خروجی مدار را به اسیلوسکوپ وصل کنید ) فرکانس 01 کیلو هرتز یا بیشتر( و نتیجه را مشاهده و بررسی نمایید . در مرحله بعد ، دو خروجی مدار را به اسیلوسکوپ وصل کنید و نتیجه را بررسی کنید . خروجی ها را دوبه دو با هم مقایسه کنیدو نتیجه را بررسی کنید . شکل 1 1 : مدار شمارنده باینری - ب : شمارنده BCD :

- 2. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 2 شکل 2 - :1 مدار شمارنده BCD مدار شمارنده BCD در شکل 0 2 نشان داده شده است . خروجی های مدار را به - LED وصل کنید ومشاهدات را بررسی نمایید . در مراحل بعد ، مانند قسمت الف ، خروجی ها را به اسیلوسکوپ وصل کنید و نتایج را بررسی نمایید . تمرین : -0 مدار داخلی IC مورد استفاده را با کمک دیتاشیت آن به دست آورید . -2 عملکرد شمارنده باینری را توضیح دهید . -3 عملکرد شمارنده BCD را توضیح دهید . -4 مدارات را در نرم افزار Proteus شبیه سازی نمایید . آزمایش دوم : گیت های منطقی دیجیتال هدف از انجام این آزمایش بررسی تاخیر انتشار گیت های منطقی است . IC 0414 و 0417 شامل گیت های منطقی ،0412 ، های 0411 متداولی هستند که در اکثر مدارات منطقی مورد استفاده قرار می گیرند . الف جدول درستی : از هر - IC یک گیت را انتخاب کنید و جدول درستی آن را به دست آورید. ورودی های گیت را به کلید ها و خروجی آن را به لامپ وصل کنید و نتیجه حاصل را با جدول درستی ایده آل گیت مقایسه کنید . ب شکل موج یک ورودی و خروجی هر گیت را در اسیلوسکوپ مشاهده و نتیجه را بررسی کنید . به زمان - rise یا fall دوسیگنال دقت کنید . ج برای تابع - F=AB+CD -0 دیاگرام مدار را رسم کنید . -2 جدول درستی F را به عنوان تابعی از 4 ورودی به دست آورید. -3 مدار را طراحی کنید و جدول درستی آن را به دست آورید.

- 3. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 3 -4 الگوهای صفر ویک ورودی ها را در جدول لیست کرده )از 1 باینری تا 01 باینری ( و خروجی متناظر با هریک را بدست آورید . -1 چهار خروجی شمارنده باینری آزمایش اول را به چهار ورودی مدار وصل کنید . ورودی کلاک شمارنده را به یکی از دو پورت ورودی اسیلوسکوپ متصل کنید و خروجی F را به ورودی دیگر اسیلوسکوپ متصل کنید . الگوهای صفر ویک خروجی بعد از هر کلاک را با جدولی که در قسمت 4 نوشته اید ، مقایسه کنید و دلیل را توضیح دهید. آزمایش 3 : ساده سازی توابع Boolean : هدف از این آزمایش ، بررسی رابطه بین توابع بولی وگیت های منطقی متناظرشان است . توابع بولی ، با روش نقشه کارنو )فصل 3 مدار منطقی مانو ( ساده می شوند .دیاگرام های منطقی با استفاده از گیت های NAND ) یک ورودی ، دو ورودی ، 3 ورودی یا 4 ورودی ( رسم می شوند .این را در نظر داشته باشید که در طراحی اگر یک ورودی گیت NAND مورد استفاده قرار نگیرد ، باید به پایه دیگر )که ورودی مدار است (متصل شود . الف دیاگرام منطقی - شکل 2 برای طراحی انتخاب شده و شما باید با استفاده از ساده سازی توابع منطقی ، تعداد گیت های مورد نیاز آزمایش را به حداقل ممکن برسانید . پس در انتخاب گیت ها دقت کنید . به همه ورودی ها و خروجی های گیت ها ، شماره اختصاص دهید . خروجی مدار را بااستفاده از جدول صحت آن ، بررسی کنید . شکل 2 توابع بولین زیر به شکل مجموع حاصل ضرب ها ) SOP (هستند : F1(A,B,C,D)= (0,1,4,5,8,9,10,12,13) F2(A,B,C,D)= (3,5,7,8,10,11,13,15)

- 4. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 4 ب توابع بالا را به روش کارنو ساده کنید . دو تابع را با یکدیگر اجرا کنید و سعی کنید حداقل تعداد گیت ها را در نظر بگیرید . مدار را طراحی - کنید و عملکردش را بررسی نمایید . جدول درستی F1 و F2 حاصل از مدار باید مطابق لیست مینترم هایتان باشد . تمرین : - شبیه سازی مدارهای بالا در نرم افزار های Proteus یا Xilinx . - تابع F=A’D + BD+B’C + AB’D و معکوس آن را با حداقل تعداد گیت های ممکن رسم کنید . ) به همراه جدول درستی و ساده سازی کارنو ( آزمایش 4 : مدارات ترکیبی در این آزمایش ، ما 4 مدار منطقی ترکیبی را طراحی و بررسی خواهیم کرد . دو مدار اول با گیت های NAND ساخته خواهند شد ، سومی با گیت های XOR و چهارمی با یک دیکدر و گیت های NAND . )عملکرد دیکدر در فصل 4 کتاب منطقی مانو توضیح داده شده است .( الف مثال طراحی : - یک مدار ترکیبی با 4 ورودی A,B,C,D و خروجی F طراحی کنید بااین فرض که خروجی زمانی 0 است که A=1 و B=0 باشد یا زمانی که B=1 و Cیا D نیز مقدار 0 را داراباشند . -0 جدول درستی مدار را به دست آورید . -2 تابع خروجی را ساده سازی نمایید. -3 دیاگرام منطقی مدار را با گیت های NAND و حداقل تعداد IC ها رسم نمایید . -4 مدار را طراحی کنید و خروجی را با فرضیاتی که به دست آوردید ، مقایسه کنید. ب منطق اکثریت : - منطق اکثریت مدار دیجیتالی است که زمانی که اکثریت ورودی ها 1 باشند ، خروجی آن نیز 0 است ) برای 1 هم همینطور(. یک مدار منطق حداکثر 3 ورودی طراحی و تست کنید با این پیش فرض که از گیت های NAND باید استفاده کنید و تعداد IC ها باید حداقل ممکن باشند . ج مولد بیت توازن : - یک مدار طراحی کنید که یک بیت توازن زوج از 4 بیت ورودی تولید کند . از گیت های XOR استفاده کنید .اگر یک گیت XOR بیشتر در مداراستفاده کنید مدار ، مولد بیت های فرد نیز می باشد . مدار را برای تولید یک بیت توازن فرد توسعه دهید . د عملکرد دیکدر : -

- 5. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 5 مدار ترکیبی ای داریم که شامل 3 ورودی X,Y,Z و 3 تابع خروجی , F2 ,F3 F1 میباشد . توابع بولین ساده شده مدار برابراند با : F1= xz+x’y’z’ F2= x’y + xy’z’ F3= xy + x’y’z مدار را با یک دیکدر ) IC 74155 ( و گیت های NAND خارجی طراحی و تست کنید .) NAND یا OR )؟؟ شکل 3 : بلاک دیاگرام و جدول صحت 74155 74155 2 استفاده شود . زمانی که بخواهیم از آن به عنوان یک دیکدر * 3 یا دو دیکدر 4 * می تواند به عنوان یک دیکدر 7 3*8 استفاده کنیم باید دو پایه C1 و C2 آنرا به هم وصل کنیم .دیتاشیت این IC را مطالعه کنید تا بهتربا عملکرد آن آشنا شوید . تمرین : شبیه سازی مدارات طراحی شده با نرم افزار Proteus یا Xilinx . آزمایش 5 :تبدیل کننده 1 کد 1 Converter

- 6. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 6 تبدیل اعداد دودویی به اعداد دیگر ، در سیستم های دیجیتال امری معمول است . در این آزمایش ، 3 مبدل مدارات ترکیبی را طراحی و اجرا خواهیم کرد. الف کد گری به باینری : - میخواهیم مدار ترکیبی طراحی کنیم که چهاربیت گری را به چهاربیت باینری معادل آن تبدیل کند .)مراجعه به جدول 0.1 کتاب منطقی مانو(. برای اینکار می توانید از گیت های EXOR ( IC7486 ( کمک بگیرید . ورودی ها را به کلید و خروجی ها را به led وصل کنید و عملکرد مدار رابررسی نمایید . - : ب مکمل 9 هدف طراحی مدار ترکیبی است که چهاربیت ورودی آن نشاندهنده یک رقم BCD است و چهاربیت خروجی آن مکمل 9 عدد ورودی می باشد . در طراحی این مدار این نکته را در نظر بگیرید که باید مدارتان به گونه ای باشد که اگر ورودی داده شده رقم BCD نبود ، شما را از این اشتباه آگاه کند . برای طراحی ازهر IC ای میتوانید استفاده کنید فقط تعدادشان باید حداقل باشد. ج نمایشگر - 7-seg : نمایشگر 7-seg برای نمایش اعداد دهدهی 1 تا 9 بکار می رود . اعداد دهدهی معمولا به فرم BCD هستند . یک دیکدر BCD به 7-seg اعداد دهدهی را به عنوان ورودی می گیرد و کد 7-seg متناظرشان را بر می گرداند )عملکرد :کتاب منطقی( شکل 3 ، اتصالات لازم بین دیکدر و نمایشگر را نشان میدهد. مدار را طراحی کنید و الگوی خروجی 1 رقم تعریف نشده ورودی آن را ثبت کنید . شکل 4 : مبدل BCD به 7-seg آزمایش 6 : جمع کننده ها و تفریق کننده ها در این آزمایش ، چندین مدار جمع کننده و تفاضل کننده خواهیم ساخت وتست خواهیم کرد.مدار تفاضل ، برای مقایسه بزرگی نسبی دو عدد به کار می رود .

- 7. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 7 الف نیم جمع کننده : - یک مدار نیم جمع کننده با استفاده از گیت های XOR و NAND طراحی و تست نمایید. ب تمام جمع کننده : - یه مدار تمام جمع کننده با استفاده از قطعات 7486 و 7400 طراحی کنید. ج جمع کننده موازی : - 7483 یک جمع کننده موازی 4 بیتی است که شمایی از آن را در شکل زیر می توانید ببینید . چهار بیت ورودی A آن را یک مقدار ثابت دهید و چهار بیت ورودی B را به کلید ها وصل کنید و خروجی ها را به LED وصل کنید . با انجام چند عمل جمع ، عملکرد مدار را بررسی کنید .نشان دهید که زمانی که حامل ورودی 0 است ، مقدار 0 به مجموع خروجی اضافه می شود. د جمع کننده تفریق کننده : – - دو عدد باینری با گرفتن مکمل 2 مفروق و جمع آن با مفروق منه می توانند از هم کم شوند . در واقع برای انجام عمل تفریق A-B ، چهار بیت B مکمل و با A جمع می شوند سپس 0 به جمع آنها اضافه می شود . مدار شکل 4 را طراحی کنید . چهار بیت ورودی A را مقدار ثابتی دهید و چهار بیت ورودی B را به کلید وصل کنید . با انتخاب مد جمع یا تفریق ، چند عمل انجام دهید و نتایج را با مقادیر محاسبه شده منطقی ، مقایسه کنید. 3443 : شکل 5

- 8. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 8 برای مثال ، جدول زیر را تست کنید : جمع کننده نتیجه تفریق کننده نتیجه - 9 1 5+9 - 9 9 9+9 - 9 01 9+15 ی مقایسه کننده مقدار : - مقایسه کردن دو مقدار ، عملی است که تعیین می کند کدام عدد بزرگتر ، کوچکتر یا مساوی دیگری است . با استفاده از مدار بالا می توان دو عدد A و B را با هم مقایسه کرد . مد عمل را تفریق تعیین می کنیم .اگر خروجی S مساوی 1 بود دو عدد مساوی اند . حالت های مقایسه ای دیگر را با استفاده از مدار توضیح دهید . مدار ترکیبی می تواند با قطعات 7404 و 7408 اجرا شود . تمرین : شبیه سازی مدارهای طراحی شده در این آزمایش به ازای ورودی ها مختلف در نرم افزارهای Xilinx و Proteus آزمایش 3 : فلیپ فلاپ ها در این آزمایش ، عملکرد لچ ها و فلیپ فلاپ های مختلف را بررسی خواهید نمود . ساختار داخلی لچ ها و فلیپ فلاپ ها در فصل 1 کتاب مانو آورده شده است . الف لچ - SR : مدار داخلی لچ را طراحی کنید . ورودی ها را از کلید دریافت کنید و خروجی را به LED متصل کنید. همه حالت های ورودی مختلف را چک کنید و با جدول عملکرد لچ مقایسه کنید . ب لچ - D : ازآنجا که حالت S=1 , R=1 برای –SR لچ غیر مجاز است و خروجی ها با هم برابرند ، لچ D پیشنهاد شده است .این لچ را به عنوان یک حافظه ی تک بیتی می شناسند )چرا؟(. یک لچ D با استفاده از 4 گیت NAND بسازید و جدول حالت آن را بررسی کنید . ج فلیپ فلاپ رهبر پیرو ) – - Master-Slave :) با اتصال دو لچ D ویک معکوس کننده ، یک فلیپ فلاپ رهبر پیشرو بسازید .ورودی - Dرا از کلید و کلاک را از پالسر بگیرید .خروجی لچ رهبر را به LED وصل کنید و خروجی لچ پیشرو را به LED دیگر وصل کنید .مقدار ورودی را به مکمل خروجی وصل کنید . پالسر را فشار

- 9. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 9 دهید تا یک پالس ایجاد شود .تغییرات رهبر و پیشرو را مشاهده کنید و توضیح دهید . در مرحله بعد ، کلاک را از پالسر قطع کنید و آنرا به مولد کلاک وصل کنید . یک ورودی اسیلوسکوپ را به کلاک وصل کنید و دیگری رابه خروجی لچ ها .رابطه بین تاخیر زمانی خروجی های لچ ها و سیکل کلاک چگونه است ؟ با رسم یک دیاگرام زمانی ، این رابطه را نشان دهید . د فلیپ فلاپ حساس به لبه : - ساخت یک فلیپ فلاپ حساس به لبه مثبت نیاز به 1 گیت NAND دارد. ورودی کلاک را به پالسر، ورودی D را به کلید و خروجی را به LED وصل کنید . مقدار D را به خروجی مکمل وصل کنید . نشان دهید که خروجی فلیپ فلاپ فقط در گذر مثبت پالس کلاک تغییر می کند . ورودی کلاک را به مولد کلاک وصل کنید و مانند حالت قبل ، خروجی را در اسیلوسکوپ مشاهده کنید و دیاگرام زمانی مربوطه را رسم نمایید. تمرین : -0 IC 7476 ، شامل دو فلیپ فلاپ JK است و IC7474 شامل دو فلیپ فلاپ D است . دیتاشیت این IC ها را مطالعه کنید و با دادن ورودی و مشاهده خروجی ، جدول حالت این فلیپ فلاپ ها را بررسی کنید . عملکرد پایه های PR و CLR چگونه است ؟ -2 گیت های منطقی پایه و سپس این فلیپ فلاپ ها را در نرم افزار Xilinx شبیه سازی وخروجی آن را تست کنید و اگر عملکرد مورد انتظار را داشت آنها را با عنوان مناسب ، بلاک نمایید . آزمایش 4 : مدارات ترتیبی دراین آزمایش شما 3 مدار ترتیبی رسم ، طراحی و تست خواهید کرد . می توانید هر کدام از IC های 7476 و 7474 را مورد استفاده قرار دهید . )گیتی را انتخاب کنید که حداقل تعداد IC را نیاز داشته باشد (. )بحث مدارات ترتیبی در بخش 1.0 کتاب منطقی مانو( الف شمارنده بالا پایین با فعال ساز : - - یک شمارنده دوبیتی با فعال ساز طراحی کنید که یا بالا شمار یا پایین شمار باشد .پایه فعال ساز تعیین می کند که آیا شمارنده روشن است یا خاموش . پایه x نیز ، بالاشمار یا پایین شمار بودن فلیپ فلاپ را تعیین می کند . ب دیاگرام حالت : - یک مدار ترتیبی رسم ، طراحی و تست کنید که دیاگرام حالت شکل 1 را پاسخگو باشد .دو فلیپ فلاپ برای A و B ، یک ورودی برای X و یک خروجی با نام y که متصل به LED می باشد .

- 10. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 10 شکل 6 ج طراحی شمارنده : - شمارنده ای طراحی کنید که ترتیب حالت های باینری زیر را بشمارد : 0,1,2,3,6,7,10,11,12,13,14,15,0 . در نظر بگیرید که حالت های باینری 4,5,8,9 بکار نرفته اند .شمارنده خودش باید شروع به شمارش کند واگر شروع شمارش از هریک از حالت های غیرمجاز بود ،پالس های شمارنده باید مدار رابه یک حالت مجاز ببرند تا شمارش ادامه داشته باشد . آزمایش 9 : شیفت رجیستر در طراحی دیجیتال، شیفت رجیستر )به معنی ثبات انتقال دهنده(، زنجیره ای از فلیپ فلاپ ها است که یک پالس ساعت مشترک دارند و خروجی هر فلیپ فلاپ، به ورودی فلیپ فلاپ بعدی در زنجیره متصل شده است؛ درنتیجه مداری حاصل می شود که می تواند در هر پالس ساعت، آرایه بیتی که در آن ذخیره شده را یک واحد به سمت چپ یا راست شیفت )انتقال( دهد. در عمل شیفت، بیتی که در ورودی قرار دارد به داخل آرایه آورده می شود )شیفت به داخل( و آخرین بیت از آرایه خارج می شود و از بین می رود )شیفت به بیرون(. در هر عمل شیفت، بیت ها از یک فلیپ فلاپ خارج، و به فلیپ فلاپ بعدی وارد می شوند. شیفت رجیسترها می توانند به صورت سریال )پشت سر هم( یا موازی )همزمان( باشند. در حالت سری، بیت ها به صورت پشت سر هم و به ترتیب وارد شیفت رجیستر می شوند و در حالت موازی همه داده ها به صورت همزمان وارد شیفت رجیستر می شوند. مثلاً یک شیفت رجیستر می تواند به صورت ورودی سری، خروجی موازی ) serial-in, parallel-out ( و یا ورودی موازی، خروجی سری ) parallel-in, serial- out ( باشد. همچنین گونه های دیگری هم وجود دارد که در آن هم ورود و هم خروج داده ها یا به صورت سری و یا به صورت موازی صورت می گیرد. مثلاً حالت ) Serial in, Serial out ( که داده ها هم به صورت سریال وارد می شوند و هم به صورت سریال خارج می شوند. همچنین گونه های دیگری از شیفت رجیسترها وجود دارد که می توانند عمل شیفت را به صورت دوطرفه انجام دهند: شیفت به سمت راست و شیفت به سمت چپ. در یک شیفت رجیستر سری می توان آخرین بیت را به اولین بیت متصل کرده تا یک شیفت رجیستر حلقوی حاصل شود. شیفت دادن یک عدد به تعداد n بار به سمت راست، برابر با تقسیم آن عدد به 2 n است. شیفت دادن یک عدد به تعداد n بار به سمت چپ، برابر با ضرب کردن آن عدد در 2 n است. در این آزمایش ما عملکرد شیفت رجیسترها را بررسی می کنیم . IC مورد استفاده در این آزمایش 04091 با پایه load موازی است . عملکرد مدارات شیفت رجیستر در بخش 1.2 کتاب منطقی مانو توضیح داده شده است .

- 11. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 11 IC 74195 یک ثبات شیفت دهنده چهاربیتی با پایه load موازی و پایه clear ) غیر همزمان است ) شکل 1 شکل 3 پایه ای که با SH/LD نشان داده شده است ،عملیات همزمان ثبات را مشخص می کند ) Shift/Load ( . زمانی که ورودی پایه به 1 وصل است ، عملیات load انجام و ورودی ها در ثبات بار می شوند و زمانی که به 0 وصل است ، عملیات shift انجام و اطلاعات ثبات از QA به QD شیفت می یابند . عملکرد پایه های j , k را در مدار بررسی کنید ) می توانید از دیتاشیت IC نیز کمک بگیرید.( الف شمارنده حلقوی : - یک شمارنده حلقوی ، ثبات شیفت دهنده دایره ای است که سیگنال خروجی سریال QD را به ورودی سریال وصل می کند.شرایط load را طوری تعیین کنید که زمانی که ورودی مدار به 0111 رسید ، شمارش از سر گرفته شود . پایه های J و K’ چه نقشی دارند ؟ عملکرد ثبات را بعد از هر پالس کلاک بررسی نمایید. ب ثبات شیفت دهنده فیدبکی - 2 : ثباتی است که ورودی سریال آن به توابعی از خروجی هایش وصل است . ثبات شیفت دهنده فیدبکی طراحی کنید که ورودی های آن به xor خروجی های QC و QD اش وصل باشد . ترتیب حالت های ثبات را پیش بینی کنید . حالت شروع 0111 باشد . نتیجه مشاهدات را با پیش بینی های خود ، مقایسه کنید. ج ثبات شیفت دهنده دوجهته : - هر عملیات شیفت به راست تاثیری معادل تقسیم بر 2 باینری است . اگر عملیات برعکس شود ) شیفت به چپ ( ، تاثیری معادل ضرب در 2 خواهد داشت . با یک ترکیب مناسب گیت های منطقی ، یک شیفت رجیستر می تواند در دو جهت عمل کند . یک شیفت رجیستر دوطرفه با قابلیت معکوس شدن می تواند دیتا را به سمت راست یا چپ شیفت دهد . 2 Feedback Shift Register

- 12. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 12 د ثبات شیفت دهنده دوجهته با پایه بارگذاری موازی : - IC 74195 می تواند یک شیفت رجیستر دو جهته با پایه load موازی است که به یک مدار مالتی پلکسر متصل است . برای مالتی پلکسر ما IC 74157 را به کار می بریم که مالتی پلکسر 2به 0 است که مدار آن در شکل زیر نشان داده شده است . دقت کنید که نام پایه فعال ساز این IC ، Strobe نام دارد . : شکل 8 IC 74157 با کمک ثبات 74195 ومالتی پلکسر 74157 ، یک ثبات شیفت دهنده دوجهته با پایه load موازی بسازید . مدار باید قادر باشد عملیات زیر را انجام دهد : -0 پاک کننده غیر همزمان -2 شیفت به راست -3 شیفت به چپ -4 بارگذاری موازی -1 پاک کننده غیرهمزمان یک جدول برای 1 عملیات بالا طراحی کنید . مدارتان را طراحی کنید و عملکرد آن را با جدولتان مقایسه کنید . شکل 9: شیفت دهنده با پایه load موازی

- 13. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 13 آزمایش 11 : جمع کننده سریال در این آزمایش ما قصد داریم تا مدار جمع کننده سریالی با استفاده ازدو شیفت رجیسترو یک تمام جمع کننده ، برای جمع دوعدد باینری بسازیم . شکل 01 : مدار جمع کننده سریال همانطور که از شکل مشخص است ، برای ساخت یک جمع کننده سریال نیاز به 2 شیفت رجیستر و یک مدار جمع کننده تفریق کننده – سریال داریم . لذا IC های موردنیاز این آزمایش 2 عدد IC 74195 ، 7408 ، 7486 و 7476 می باشند . جمع کننده سریال : با مراجعه به بخش 1.1 کتاب منطقی مانو ، توضیحات لازم برای ساخت این مدار را پیدا خواهید کرد . شبفت رجیستر B داده هار ا به صورت موازی از 4 کلید دریافت می کند . ورودی سریال این شیفت رجیستر رابه زمین وصل کنید )چرا؟( برای پایه clear تمام جمع کننده و شیفت رجیستر نیز از 2 کلید کمک بگیرید. یک کلید دیگر هم نیاز داریم تا تعیین کنیم که شیفت رجیستر B داده موازی رابپذیرد یا اطلاعات را شیفت دهد . تست جمع کننده : 01+1+1= برای تست مدار جمع کننده جمع باینری 21 را انجام دهید . جمع کننده تفریق کننده سریال : – اگر طبق روش گفته شده در بخش 1.2 برای طراحی یک تفریق کننده سریال عمل کنیم ، خواهیم دید که خروجی نهایی با خروجی sum برابر است اما ورودی j,k فلیپ فلاپ borrow )رقم قرضی( به مکمل QD نیاز دارد. با بکاربردن دو گیت XOR دیگر، جمع کننده سریال را به جمع کننده تفریق کننده سریال با انتخاب حالت ) – M( تبدیل کنید بطوریکه وقتی M=0 باشد مدار جمع کننده باشد و زمانی که M=1 باشد ، مدار تفریق کننده باشد. پس از طراحی ، تفریق 15-4-5-13=-7 را انجام دهید و صحت عملکرد مدار را بررسی نمایید.

- 14. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 14 آزمایش 11 : واحد حافظه دراین آزمایش ، رفتار یک واحد حافظه با دسترسی تصادفی (RAM) و توانایی ذخیره سازی اش را بررسی خواهیم کرد . RAM را برای شبیه سازی یک حافظه فقط خواندنی (ROM) نیز بکار خواهیم برد. سپس از ROM برای اجرای مدارات ترکیبی استفاده خواهیم کرد . )فصل 0 منطقی مانو( الف : RAM )34149( IC 74189 یک RAM 16*4 است )مدار داخلی آن مثل RAM 4*4 شکل 0.1 کتاب مانو است( . ورودی های آدرس یکی از 01 کلمه حافظه را انتخاب می کنند (A0…16) . ورودی انتخابگر چیپ (CS) برای فعال سازی حافظه باید 1 باشد که اگر 0 باشد حافظه غیر فعال و خروجی در حالت امپدانس بالا خواهد بود . ورودی فعال ساز نوشتن (WE) نوع عملیات را تعیین می کند ) مطابق جدول زیر ( - شکل 00 74189 عملیات خواندن زمانی اجرا می شود که WE=1 باشد . خروجی های حافظه 3حالته می باشند که توسعه حافظه را آسان تر می کند.)چرا؟؟( تست RAM : از آنجایی که خروجی های این IC فعال پایین اند نیاز هست که سر راه ورودی ها گیت NOT قرار دهید . بعد از اینکه ، RAM را طراحی کردید ، ورودی های آدرس را به یک شمارنده باینری (7493) وصل کنید . ورودی های داده را به چهار کلید و خروجی ها را نیز به چهار معکوس کننده )چرا؟( وصل کنید . چهار LED به خطوط آدرس و چهار تا به خروجی ، CS را به زمین و WE را به کلید وصل کنید . تعدادی کلمه در حافظه ذخیره کنید . شروع به خواندن آنها نمایید و صحت عملکرد مدار را مشاهده کنید .

- 15. دستور کارآزمایشگاه مدار منطقی دانشگاه بزرگمهر قاینات 15 ب : ROM یک ROM شبیه ساز ، عملکرد یک RAM را در حالت فقط خواندنی دارد . در حالت نوشتن ، الگوی 1 و 0 در خانه های حافظ قرار می گیرند . شبیه ساز با قراردادن واحدی در مد خواندن و دادن خطوط آدرس به عنوان ورودی به دست می آید . ROM می تواند در هر مدار ترکیبی به کار رود. یک مدار ترکیبی با کمک شبیه ساز ROM ، که یک عدد چهاربیتی باینری را به کد گری معادلش تبدیل می کند ، طراحی کنید . ابتدا جدول صحت تبدیل کد را به دست آورید . جدول صحت را در حافظه 04079 با قراردادن مقدار باینری در ورودی های آدرس و مقدار کد گری متناظردر ورودی های داده ذخیره کنید .بعد از اینکه 01 ورودی جدول در حافظه نوشته شدند ، شبیه ساز ROM با اتصال همیشگی پایه WE به منطق 0 ایجاد می شود . صحت عملکرد مدار را با دادن آدرس های ورودی مختلف چک کنید . ج : توسعه حافظه واحد حافظه را با بکار بردن دو IC 74189 ، به یک RAM 32*4 تبدیل کنید .ورودی های CS را برای انتخاب بین دو IC بکار برید . دقت کنید که از آنجایی که خروجی های داده 3 حالته اند ، باید خروجی هارا بایکدیگر جفت کنید تا یک عمل منطقی OR بین دو IC به دست آید. مدار را با تبدیل آن به یک شبیه ساز ROM که یک عدد 3 بیتی رابا یک عدد 2 بیتی جمع و نتیجه یک عدد 4 بیتی حاصل شده است ، تست کنید . برای مثال اگر ورودی ROM 010 باشد .برای خطوط آدرس از یک شمارنده +01= عدد 01001 باشد خروجی باید عدد 1000 چهاربیتی و برای بیت پنجم از یک کلید استفاده کنید )چرا؟( تمرین : شبیه سازی مدارات آزمایش با نرم افزارهای Xilinx و Proteus . موفق باشید کریمی