More Related Content

Similar to 新規デザインキット計画(新サービス:株式会社ビー・テクノロジー)

Similar to 新規デザインキット計画(新サービス:株式会社ビー・テクノロジー) (9)

More from Tsuyoshi Horigome

More from Tsuyoshi Horigome (20)

新規デザインキット計画(新サービス:株式会社ビー・テクノロジー)

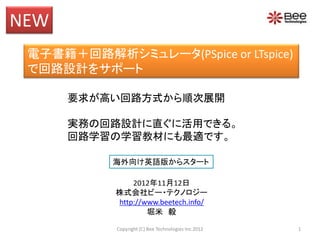

- 1. NEW

電子書籍+回路解析シミュレータ(PSpice or LTspice)

で回路設計をサポート

要求が高い回路方式から順次展開

実務の回路設計に直ぐに活用できる。

回路学習の学習教材にも最適です。

海外向け英語版からスタート

2012年11月12日

株式会社ビー・テクノロジー

http://www.beetech.info/

堀米 毅

Copyright (C) Bee Technologies Inc.2012 1

- 3. ご提供予定の回路方式

降圧チョッパ ZETA 電流モード

昇圧チョッパ 絶縁CUK 力率改善

昇降圧チョッパ 電圧共振 マルチフェーズ

フォワード 電流共振 電流型

フライバック 共振 三相フルブリッジインバータ

フルブリッジ E級共振

ハーフブリッジ 複共振

プッシュプル アクティブクランプ

CUK 位相シフト

SEPIC 同期整流

Copyright (C) Bee Technologies Inc.2012 3

- 4. イメージ

降圧チョッパ回路方式(スタンダード版)

R1 C1

10 2n

U1

R2 L1 2SK3682 L2

1 2 1 2

Vo

1m 0.01uH

100uH

R3

R4 R5

10

12Vdc V2

V1 22 10k

C2 U2 R6

S 40CPQ050

2n 1m

Implementation = V_sig 2 R7

I

L3 0.5

10nH C3

1000u

1

R8

1m

0

Copyright (C) Bee Technologies Inc.2012 4

- 6. イメージ

降圧チョッパ回路方式(プロフェッショナル版)

R1 C1

BUCK CONVERTER

10 2n

R2 L1 L2

1 2 D S 1 2

Vo

1m 0.01uH

U1 100uH

K

2SK3682

G

R4 R5

R3

GATE

V1 22 10k 10 R6

C2 U2 1m

SOURCE

12Vdc 40CPQ050

2n

A

2 R7

L3 0.5

10nH

1 C3

R8 1000u

1m

0 CONTROL

GATE SIG_G Vin+ Vo

SOURCE SIG_S Vin-

Implementation = CONTROL2

0

制御方式を選択

CONTROL1 プロフェッショナル版では、制御回路も含まれます。

CONTROL2 実践的な内容です。

Copyright (C) Bee Technologies Inc.2012 6

- 7. イメージ

降圧チョッパ回路方式(プロフェッショナル版)

CONTROL1 Error Amplifier

D1 D2

C1

100p

Soft Start

R1 C2

D3 R2

1k 0.68u

1000

Dbreak R3

C3

1u 470k

0 IC = 5 VEE

Detecting Output Voltage

E1 R4 4

V- U1A Comparator

2

Vin+ IN+ OUT+ -

IN- OUT- 1k E2

1

EVALUE 0 OUT IN+ OUT+ SIG_G

Vin- IN- OUT-

1.8/5*V(%IN+, %IN-) 3

+ 8 ETABLE

1.8Vdc V+ V(%IN+,%IN-)

SIG_S

VREF1 VCC TABLE = (0,0) (1m,15)

VCAREER1

VCC VEE 0 (0, 0)(49.99u,5)(50u,0)

V1 V2 0

15Vdc -15Vdc

0 0

Copyright (C) Bee Technologies Inc.2012 7

- 8. イメージ

降圧チョッパ回路方式(プロフェッショナル版)

Error Amplifier

CONTROL2 D1 D2

C1

100p

Soft Start

R1 C2

D3 R2

1k 0.68u

1000

Dbreak R3

C3

1u 470k

0 IC = 5

AMP

Detecting Output Voltage Comparator

E1 R4

Vin+ IN+ OUT+ INV E2

IN- OUT- 1k OUT IN+ OUT+ SIG_G

EVALUE 0 NON_INV IN- OUT- R5

Vin- EVALUE

1.8/5*V(%IN+, %IN-)

VREF1 limit(V(%IN+, %IN-)*1e9,0,15)

1k

SIG_S

1.8Vdc

0 VCAREER1

(0, 0)(49.99u,5)(50u,0)

0

1 (-V(%IN1) R1

INV

+V(%IN2) )*1e1*2 3 V(%IN)*1e-3 V(%IN) R2 V(%IN)

2 0

NON_INV 10k OUT

D1 D2

R3 C1 D3 D4 100k D5 D6 R4

V1 V2 10meg

12Vdc 1n V3 V4 V5 V6 1k

-12Vdc -16Vdc 16Vdc -12Vdc 12Vdc

0 0 0

0 0

0 0 0 0

Copyright (C) Bee Technologies Inc.2012 8