2Sem-MTech-Low Power VLSI Design Homework - Unit1

•

3 gostaram•6,748 visualizações

Denunciar

Compartilhar

Denunciar

Compartilhar

Recomendados

Recomendados

Mais conteúdo relacionado

Mais procurados

Mais procurados (19)

POWER CONSUMPTION AT CIRCUIT OR LOGIC LEVEL IN CIRCUIT

POWER CONSUMPTION AT CIRCUIT OR LOGIC LEVEL IN CIRCUIT

Power Dissipation of VLSI Circuits and Modern Techniques of Designing Low Pow...

Power Dissipation of VLSI Circuits and Modern Techniques of Designing Low Pow...

IRJET- High Efficiency Bridge-Less Battery Charger for Light Electric Veh...

IRJET- High Efficiency Bridge-Less Battery Charger for Light Electric Veh...

Destaque

Destaque (17)

Design of 16 bit low power processor using clock gating technique 2-3

Design of 16 bit low power processor using clock gating technique 2-3

Book Summary - What got you here wont get you there!

Book Summary - What got you here wont get you there!

Semelhante a 2Sem-MTech-Low Power VLSI Design Homework - Unit1

www.ijeijournal.comInternational Journal of Engineering Inventions (IJEI)

International Journal of Engineering Inventions (IJEI)International Journal of Engineering Inventions www.ijeijournal.com

Semelhante a 2Sem-MTech-Low Power VLSI Design Homework - Unit1 (20)

Optimal Capacitor Placement in Distribution System using Fuzzy Techniques

Optimal Capacitor Placement in Distribution System using Fuzzy Techniques

International Journal of Engineering Inventions (IJEI)

International Journal of Engineering Inventions (IJEI)

A Literature Survey on Energy Efficient MAC Protocols For WSN

A Literature Survey on Energy Efficient MAC Protocols For WSN

High performance novel dual stack gating technique for reduction of ground bo...

High performance novel dual stack gating technique for reduction of ground bo...

IRJET- An Enhanced Cluster (CH-LEACH) based Routing Scheme for Wireless Senso...

IRJET- An Enhanced Cluster (CH-LEACH) based Routing Scheme for Wireless Senso...

IRJET- Fitness Function as Trust Value using to Efficient Multipath Routi...

IRJET- Fitness Function as Trust Value using to Efficient Multipath Routi...

Wireless Sensor Grids Energy Efficiency Enrichment Using Quorum Techniques

Wireless Sensor Grids Energy Efficiency Enrichment Using Quorum Techniques

Using the CC2430 and TIMAC for low-power wireless sensor applications: A powe...

Using the CC2430 and TIMAC for low-power wireless sensor applications: A powe...

Mais de Dr. Shivananda Koteshwar

Mais de Dr. Shivananda Koteshwar (20)

Understanding scale Clean tech and Agritech verticals

Understanding scale Clean tech and Agritech verticals

IoT product business plan creation for entrepreneurs and intrepreneurs

IoT product business plan creation for entrepreneurs and intrepreneurs

ASIC SoC Verification Challenges and Methodologies

ASIC SoC Verification Challenges and Methodologies

Último

https://app.box.com/s/7hlvjxjalkrik7fb082xx3jk7xd7liz3TỔNG ÔN TẬP THI VÀO LỚP 10 MÔN TIẾNG ANH NĂM HỌC 2023 - 2024 CÓ ĐÁP ÁN (NGỮ Â...

TỔNG ÔN TẬP THI VÀO LỚP 10 MÔN TIẾNG ANH NĂM HỌC 2023 - 2024 CÓ ĐÁP ÁN (NGỮ Â...Nguyen Thanh Tu Collection

Último (20)

UGC NET Paper 1 Mathematical Reasoning & Aptitude.pdf

UGC NET Paper 1 Mathematical Reasoning & Aptitude.pdf

General Principles of Intellectual Property: Concepts of Intellectual Proper...

General Principles of Intellectual Property: Concepts of Intellectual Proper...

Python Notes for mca i year students osmania university.docx

Python Notes for mca i year students osmania university.docx

Food safety_Challenges food safety laboratories_.pdf

Food safety_Challenges food safety laboratories_.pdf

Russian Escort Service in Delhi 11k Hotel Foreigner Russian Call Girls in Delhi

Russian Escort Service in Delhi 11k Hotel Foreigner Russian Call Girls in Delhi

Basic Civil Engineering first year Notes- Chapter 4 Building.pptx

Basic Civil Engineering first year Notes- Chapter 4 Building.pptx

ICT role in 21st century education and it's challenges.

ICT role in 21st century education and it's challenges.

This PowerPoint helps students to consider the concept of infinity.

This PowerPoint helps students to consider the concept of infinity.

On National Teacher Day, meet the 2024-25 Kenan Fellows

On National Teacher Day, meet the 2024-25 Kenan Fellows

Unit-IV; Professional Sales Representative (PSR).pptx

Unit-IV; Professional Sales Representative (PSR).pptx

Unit-V; Pricing (Pharma Marketing Management).pptx

Unit-V; Pricing (Pharma Marketing Management).pptx

TỔNG ÔN TẬP THI VÀO LỚP 10 MÔN TIẾNG ANH NĂM HỌC 2023 - 2024 CÓ ĐÁP ÁN (NGỮ Â...

TỔNG ÔN TẬP THI VÀO LỚP 10 MÔN TIẾNG ANH NĂM HỌC 2023 - 2024 CÓ ĐÁP ÁN (NGỮ Â...

2Sem-MTech-Low Power VLSI Design Homework - Unit1

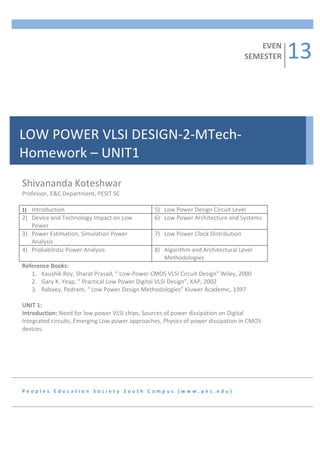

- 1. 13 EVEN SEMESTER LOW POWER VLSI DESIGN-‐2-‐MTech-‐ Homework – UNIT1 Shivananda Koteshwar Professor, E&C Department, PESIT SC 1) Introduction 5) Low Power Design Circuit Level 2) Device and Technology Impact on Low 6) Low Power Architecture and Systems Power 3) Power Estimation, Simulation Power 7) Low Power Clock Distribution Analysis 4) Probabilistic Power Analysis 8) Algorithm and Architectural Level Methodologies Reference Books: 1. Kaushik Roy, Sharat Prasad, “ Low-‐Power CMOS VLSI Circuit Design” Wiley, 2000 2. Gary K. Yeap, “ Practical Low Power Digital VLSI Design”, KAP, 2002 3. Rabaey, Pedram, “ Low Power Design Methodologies” Kluwer Academic, 1997 UNIT 1: Introduction: Need for low power VLSI chips, Sources of power dissipation on Digital Integrated circuits, Emerging Low power approaches, Physics of power dissipation in CMOS devices. P e o p l e s E d u c a t i o n S o c i e t y S o u t h C a m p u s ( w w w . p e s . e d u )

- 2. Low Power VLSI Design (2nd Semester) UNIT 1 HW v1.0 Paper Submission Team 1 Need for Low Power VLSI Chips Subramanya / Ravindra 2 Failure Mechanism with Temperature Shivukumar / Amaranath increase 3 Ultra Low Power Device and Applications Sagar / Akshay 4 VI Characteristics of Inverter and Passgate Santosh / Ajit 5 Low/High Vt Cells and MTCMOS Cells Nitin / Zowresh 6 Cooling strategies in a chip Swatishree / Chaitra 7 Packaging techniques and +/- of each Geetanjali / Harshitaa 8 Sources of Power Dissipation Rajshekhar / Vinayak 9 Scaling and different parameters Sandeep / Muralidhar Questions to be answered by all (All are 6marks questions unless specified otherwise) 1. What are the sources of power dissipation in digital ICs ? 2. With usual notation derive the equation for short circuit power dissipation in a CMOS inverter (10m) 3. Discuss the techniques to reduce power dissipation (10m) 4. Write an explanatory notes on physics of power dissipation in MOSFET devices? 5. Explain the need for Low Power VLSI Design 6. Discuss about the dynamic dissipation in CMOS 7. A 32 bit off chip bus operating at 5V and 66MHz clock rate is driving a capacitance of 25pF/bit. Each bit is estimated to have a toggling probability of 0.25 at each clock cycle. What is the power dissipation in operating the bus 8. Explain the basic principle of Low Power Design 9. Derive the most important equation for power dissipation in digital VLSI circuits taking into account the charging and discharging of capacitance in CMOS circuits 10. Explain the effects of input signal slope and output loading capacitance on short circuit current Shivoo Koteshwar’s Notes 2 shivoo@pes.edu