Mq Datasheet D3de

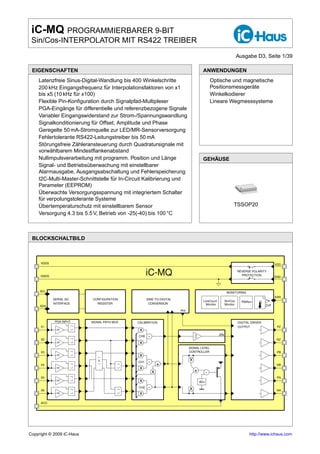

- 1. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 1/39 EIGENSCHAFTEN ANWENDUNGEN o Latenzfreie Sinus-Digital-Wandlung bis 400 Winkelschritte o Optische und magnetische o 200 kHz Eingangsfrequenz für Interpolationsfaktoren von x1 Positionsmessgeräte bis x5 (10 kHz für x100) o Winkelkodierer o Flexible Pin-Konfiguration durch Signalpfad-Multiplexer o Lineare Wegmesssysteme o PGA-Eingänge für differentielle und referenzbezogene Signale o Variabler Eingangswiderstand zur Strom-/Spannungswandlung o Signalkonditionierung für Offset, Amplitude und Phase o Geregelte 50 mA-Stromquelle zur LED/MR-Sensorversorgung o Fehlertolerante RS422-Leitungstreiber bis 50 mA o Störungsfreie Zähleransteuerung durch Quadratursignale mit vorwählbarem Mindestflankenabstand o Nullimpulsverarbeitung mit programm. Position und Länge GEHÄUSE o Signal- und Betriebsüberwachung mit einstellbarer Alarmausgabe, Ausgangsabschaltung und Fehlerspeicherung o I2C-Multi-Master-Schnittstelle für In-Circuit Kalibrierung und Parameter (EEPROM) o Überwachte Versorgungsspannung mit integriertem Schalter für verpolungstolerante Systeme o Übertemperaturschutz mit einstellbarem Sensor TSSOP20 o Versorgung 4.3 bis 5.5 V, Betrieb von -25(-40) bis 100 °C BLOCKSCHALTBILD VDDS VDD GNDS iC-MQ REVERSE POLARITY PROTECTION GND SCL MONITORING C ERR SERIAL I2C CONFIGURATION SINE-TO-DIGITAL Tw LineCount Sin/Cos PWRon INTERFACE REGISTER CONVERSION Monitor Monitor SDA Toff PHI PGA INPUT SIGNAL PATH MUX CALIBRATION DIGITAL DRIVER X1 OUTPUT PZ I/V x ZIN X2 CH0 - NZ I/V x SIGNAL LEVEL X3 CONTROLLER PB I/V x CH1 - x X4 + NB I/V x x + - X5 PA I/V x ADJ X6 CH2 - x NA I/U x ACO Copyright © 2009 iC-Haus http://www.ichaus.com

- 2. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 2/39 KURZBESCHREIBUNG Der Interpolator iC-MQ ist ein nichtlinearer A/D- steuern kann (Ausgang ACO). Für magnetische Sen- Wandler, der Sinus-/Cosinus-Sensorsignale über ein soren übernimmt diese Treiberstufe die Versorgung verzählsicheres Nachlaufverfahren mit wählbarer der MR-Messbrücken. Durch die Nachführung der Auflösung und Hysterese digitalisiert. Die Winkelauf- Sensorversorgung werden Temperatur- und Alte- lösung pro Sinus-Periode ist mit SELRES einstellbar; rungseffekte des Sensors ausgeglichen, die Ein- bis zu 400 Winkelschritte sind möglich (siehe S. 26). gangssignale stabilisiert und die exakte Kalibrierung der Eingangssignale aufrecht erhalten - dadurch ist Die inkrementale Ausgabe des Winkelwerts er- eine gleichbleibende Genauigkeit der Interpolation folgt über differentielle RS422-Treiber als Encoder- im gesamten Betriebstemperaturbereich möglich. Quadratur-Signal mit Nullimpuls, oder wahlweise als Zählersignal für 74HC191 oder 74HC193 kompatible Werden Regelungsgrenzen erreicht, kann dies am Bausteine. maskierbaren Fehlerpin ERR angezeigt werden. Er- fasst werden Störungen zum Beispiel durch Über- Der Nullimpuls wird elektronisch generiert, wenn die steuerung, Drahtbruch, Kurzschluss, Verschmutzung Freigabe über die X1/X2-Eingänge erteilt ist, und ist und Alterung. weitestgehend konfigurierbar: In der relativen Lage zum Eingangssignal, bezüglich der logischen Ver- iC-MQ enthält umfangreiche Selbsttest- und knüpfung mit A bzw. B, sowie in der Breite von 90 Systemdiagnose-Funktionen, zur Überwachung ei- bis 360 Grad (1/4 bis 1 T). nes fehlerfreien Sensorbetriebs. Für alle Fehlerer- eignisse ist separat wählbar, ob eine Meldung durch Ein vorwählbarer minimaler Flankenabstand sorgt für die Anzeige am Fehlerpin ERR oder die Abschal- Glitch-freie Ausgangssignale und verhindert Zählfeh- tung der Ausgänge erfolgen soll. Gleichzeitig ist die ler, was die Störfestigkeit der Positionserfassung er- Speicherung von Fehlern im EEPROM möglich, um höht. eine spätere Ausfalldiagnose zu ermöglichen. Für Drehgeber-Applikationen kann beispielsweise die Programmierbare Instrumentenverstärker mit wähl- Strichzahl der Codescheibe, das Sensorsignal be- barer Verstärkung erlauben differentielle oder refe- züglich Signalstärke und Frequenz, sowie per ein- renzbezogene Eingangssignale; über den Eingang stellbarem On-Chip-Sensor die Betriebstemperatur X2 kann eine externe Referenz zur Bezugsquelle für überwacht werden. die Offset-Korrektur werden. Der anzeigende Fehlerpin ERR ist bidirektional, Die Betriebsarten unterscheiden hochohmige Im- ein extern erkannter Systemfehler kann erfasst und pedanz (V-Modi) oder niederohmige Impedanz (I- ebenfalls im Fehlerspeicher registriert werden. Modi). Durch diese Anpassung an Spannungs- oder Stromsignale ist der direkte Anschluss von MR- Der Baustein iC-MQ ist verpolungsfest und stellt ei- Sensorbrücken oder Photosensoren möglich. Durch ne überwachte Spannungsversorgung zum Aufbau die Referenzfunktion am Eingang X2 werden eben- eines verpolungsfesten Systems zur Verfügung (für falls optische Abtastungen niedrig auflösender Co- Lastströme bis 20 mA). Der Verpolungsschutz be- descheiben unterstützt, die Spuren nicht differentiell steht ebenfalls für die kurzschlussfesten Leitungs- sondern gegen eine Referenzfotodiode bewerten. treiber, sodass eine versehentliche Anschlussvertau- schung bei der Inbetriebnahme toleriert wird. Die integrierte Signalkonditionierung erlaubt den Ab- gleich der Signalamplituden und Offsetspannungen, Die Bausteinkonfiguration wird nach dem Einschal- sowie die Korrektur eines Phasenfehlers zwischen ten über die serielle Konfigurations-Schnittstelle aus dem Sinus- und Cosinus-Signal. Der Kanal für das einem externen EEPROM geladen und per CRC- Nullsignal ist separat einstellbar. Prüfung verifiziert. Ein Mikrocontroller kann die Kon- figuration ebenfalls vornehmen, die implementierte Aus den konditionierten Signalen wird ein Regel- Schnittstelle ist multi-master-fähig und erlaubt einen signal gewonnen, das über die integrierte 50 mA- direkten RAM-Zugriff. Treiberstufe die Sende-LED optischer Systeme an-

- 3. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 3/39 INHALT GEHÄUSE 4 1. Fotodioden-Array am Stromeingang, LED-Versorgung über GRENZWERTE 5 Konstantstromquelle . . . . . . . . . . . 23 2. Encoder mit 100 mVss am THERMISCHE DATEN 5 Spannungseingang . . . . . . . . . . . . 23 SIGNALKONDITIONIERUNG CH0 24 KENNDATEN 6 Verstärkungseinstellung CH0 . . . . . . . . . 24 PROGRAMMIERUNG 11 Offsetabgleich CH0 . . . . . . . . . . . . . . 24 SIGNALPEGEL-REGLER und REGISTERBELEGUNG 12 SIGNALÜBERWACHUNG 25 SERIELLE SINUS-DIGITAL-WANDLUNG 26 KONFIGURATIONS-SCHNITTSTELLE 14 Beispiel der CRC Berechnungsroutine . . . . 14 AUSGANGSEINSTELLUNGEN UND EEPROM-Auswahl . . . . . . . . . . . . . . . 14 NULLSIGNAL 27 2 I C-Slave-Modus (ENSL = 1) . . . . . . . . . 15 Nullsignal-Erzeugung . . . . . . . . . . . . . 27 Funktion der CFGABZ-Einstellung . . . . . . 28 BIAS-STROMQUELLE UND Einstellungsbeispiel 1 . . . . . . . . . . . . . 28 TEMPERATURSENSOR-KALIBRIERUNG 16 Einstellungsbeispiel 2 . . . . . . . . . . . . . 28 Bias-Strom . . . . . . . . . . . . . . . . . . . 16 Konfiguration der Ausgangstreiber . . . . . . 29 Temperatursensor . . . . . . . . . . . . . . . 16 Mindestflankenabstand . . . . . . . . . . . . 29 BETRIEBSARTEN 17 FEHLERÜBERWACHUNG UND ALARMAUSGABE 30 Mode ABZ . . . . . . . . . . . . . . . . . . . 17 Fehlerprotokoll . . . . . . . . . . . . . . . . . 31 Mode 191/193 . . . . . . . . . . . . . . . . . 17 Strichzahlfehler . . . . . . . . . . . . . . . . . 31 Calibration 1, 2, 3 . . . . . . . . . . . . . . . 17 Temperatur-Überwachung . . . . . . . . . . . 31 TEST 6 . . . . . . . . . . . . . . . . . . . . . 18 Systemtest . . . . . . . . . . . . . . . . . . . 18 VERPOLUNGSSCHUTZ 32 EINGANGSKONFIGURATION 19 TESTMODUS 33 Stromsignale . . . . . . . . . . . . . . . . . . 19 Schnelle Umprogrammierung im Spannungssignale . . . . . . . . . . . . . . . 19 Single-Master-System . . . . . . . . . . 34 Schnelle Umprogrammierung im Multi-Master-System . . . . . . . . . . . 34 SIGNALPFAD-MULTIPLEXER 20 APPLIKATIONSBEISPIELE 35 SIGNALKONDITIONIERUNG CH1, CH2 21 Verstärkungseinstellung . . . . . . . . . . . . 21 APPLIKATIONSHINWEISE 37 Offsetabgleich . . . . . . . . . . . . . . . . . 22 In-Circuit Programmierung des EEPROMs . . 37 Phasenabgleich CH1 gg. CH2 . . . . . . . . 22 Absolute Winkelgenauigkeit und Flankenjitter 37 Konditionierungsbeispiele . . . . . . . . . . . 23 Hinweise zum Demo-Board . . . . . . . . . . 37

- 4. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 4/39 GEHÄUSE PIN-BELEGUNG TSSOP20 PIN-FUNKTIONEN Nr. Name Funktion 1 X1 Signaleingang 1 (Index +) 2 X2 Signaleingang 2 (Index -) 3 X3 Signaleingang 3 ( 4 X4 Signaleingang 4 5 VDDS Geschaltete Versorgungsspannung (verpolungsicher, Last bis max. 20 mA) 6 GNDS Geschaltete Masse (verpolungsicher) 7 X5 Signaleingang 5 8 X6 Signaleingang 6 9 ACO Signalpegel-Regler, Highside-Stromquellen-Ausgang 10 SDA Serielle Konfigurations-Schnittstelle, Datenleitung 11 SCL Serielle Konfigurations-Schnittstelle, Taktleitung 12 NB Inkrementalausgang B- 13 PB Inkrementalausgang B+ 14 NA Inkrementalausgang A- 15 PA Inkrementalausgang A+ 16 GND Masse 17 VDD +4.3...5.5 V Versorgungsspannung 18 NZ Inkrementalausgang Z- 19 PZ Inkrementalausgang Z+ 20 ERR Fehlersignal (Ein-/Ausgang) / Triggerein- gang Testmodus

- 5. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 5/39 GRENZWERTE Grenzwerte sind keine zulässigen Betriebsbedingungen, die Funktion ist nicht garantiert. Eine Überschreitung von Grenzwerten kann den Baustein schädigen. Kenn- Formel- Benennung Bedingungen Einh. Nr. zeichen Min. Max. G001 V() Spannung an VDD, PA, NA, PB, NB, -6 6 V PZ, NZ, SCL, SDA, ACO G002 V() Spannung an ERR -6 8 V G003 V() Pin-Pin Spannung 6 V G004 V() Spannung an X1...X6, SCL, SDA -0.3 VDDS + V 0.3 G005 I(VDD) Strom in VDD -20 400 mA G006 I() Strom in VDDS, GNDS -50 50 mA G007 I() Strom in X1...X6, SCL, SDA, ERR -20 20 mA G008 I() Strom in PA, NA, PB, NB, PZ, NZ -100 100 mA G009 I(ACO) Strom in ACO -100 20 mA G010 Vd() Zulässige ESD-Prüfspannung an allen HBM 100 pF entladen über 1.5 kΩ 2 kV Pins G011 Ptot Zulässige Verlustleistung 300 mW G012 Tj Chip-Temperatur -40 150 °C G013 Ts Lagertemperatur -40 150 °C THERMISCHE DATEN Betriebsbedingungen: VDD = 4.3 ... 5.5 V Kenn- Formel- Benennung Bedingungen Einh. Nr. zeichen Min. Typ Max. T01 Ta Zulässiger -25 100 °C Umgebungstemperaturbereich (erweiterter Temperaturbereich bis -40 °C auf Anfrage) T02 Rthja Thermischer Widerstand 80 K/W Chip / Umgebung Alle Spannungsangaben beziehen sich auf Pin GNDS, wenn kein anderer Bezugspunkt angegeben ist. In den Baustein hinein fließende Ströme zählen positiv, heraus fließende Ströme negativ.

- 6. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 6/39 KENNDATEN Betriebsbedingungen: VDD = 4.3...5.5 V, Tj = -40...125 °C, IBN auf 200 µA kalibriert, wenn nicht anders angegeben. Kenn- Formel- Benennung Bedingungen Einh. Nr. zeichen Min. Typ Max. Allgemeines 001 V(VDD) Zulässige Versorgungsspannung Laststrom I(VDDS) bis 10 mA 4.3 5.5 V Laststrom I(VDDS) bis 20 mA 4.5 5.5 V 002 I(VDD) Versorgungsstrom Tj = -40...125 °C, keine Last 25 mA Tj = 27 °C, keine Last 12 mA 003 I(VDDS) Zulässiger Laststrom in VDDS -20 0 mA 004 Vcz()hi Clamp-Spannung hi an allen Pins 11 V 005 Vc()hi Clamp-Spannung hi an Eingän- Vc()hi = V() - V(VDD), I() = 1 mA 0.4 1.5 V gen SCL, SDA 006 Vc()hi Clamp-Spannung hi an Eingän- Vc()hi = V() - V(VDD), I() = 4 mA 0.3 1.2 V gen X1...X6 007 Vc()lo Clamp-Spannung lo an allen Pins I() = -4 mA -1.2 -0.3 V Signalkonditionierung, Eingänge X1...X6 (CH1, CH2: i = 12, CH0: i = 0) 101 Vin()sig Zulässiger RINi() = 0x01 0.75 VDDS V Eingangsspannungsbereich − 1.5 RINi() = 0x09 0 VDDS V 102 Iin()sig Zulässiger Eingangsstrombereich RINi(0) = 0; BIASi = 0 -300 -10 µA RINi(0) = 0; BIASi = 1 10 300 µA 103 Iin() Eingangsstrom RINi() = 0x01 -10 10 µA 104 Rin() Eingangswiderstand gg. VREFin Tj = 27 °C; RINi(3:0) = 0x09 16 20 24 kΩ RINi(3:0) = 0x00 1.1 1.6 2.1 kΩ RINi(3:0) = 0x02 1.6 2.3 3.0 kΩ RINi(3:0) = 0x04 2.2 3.2 4.2 kΩ RINi(3:0) = 0x06 3.2 4.6 6.0 kΩ 105 TC(Rin) Temperaturkoeffizient von Rin 0.15 %/K 106 VREFin() Referenzspannungen RINi(0) = 0, BIASi = 1 1.35 1.5 1.65 V VREFin0, VREFin12 RINi(0) = 0, BIASi = 0 2.25 2.5 2.75 V 107 G0, G12 Einstellbare Verstärkungsfaktoren RINi(3) = 0, GRi und GFi = 0x0 2 RINi(3) = 0, GRi und GFi = max. 100 RINi(3) = 1, GRi und GFi = 0x0 0.5 RINi(3) = 1, GRi und GFi = max. 25 108 Gdiff Relative Verstärkung CH1 gg. GF2 = 0x10, GF1 = 0x0 39 % CH2 GF2 = 0x10, GF1 = 0x7F 255 % 109 ∆G Inkrementschrittweite der für CH0 1.06 Verstärkungsfeineinstellung für CH1 1.015 für CH2 1.06 110 INL(Gi) Integraler Linearitätsfehler der -1.06 1.06 Verstärkungseinstellung 111 Vin()diff Empfohlene Vin()diff = V(PCHx) - V(NCHx); Diff.-Eingangsspannung RINi(3) = 0 10 500 mVpp RINi(3) = 1 40 2000 mVpp 112 Vin()os Offsetspannung der bezogen auf Eingangsseite 25 µV Eingangsstufe 113 VOScal Abgleichbereich Offset bezogen auf die gewählte Quelle (VOS0 bzw. VOS12), Modus Calibration 2; ORi = 00 ±100 %V() ORi = 01 ±200 %V() ORi = 10 ±600 %V() ORi = 11 ±1200 %V() 114 ∆OF0 CH0 Inkrementschrittweite für bezogen auf die gewählte Quelle VOS0; 3.2 % Feinabgleich Offset OR0 = 0x0 115 ∆OF12 CH1/2 Inkrementschrittweite für bezogen auf die gewählte Quelle VOS12; 0.79 % Feinabgleich Offset OR12 = 0x0 116 INL(OFi) Integraler Linearitätsfehler für eingeschränkte Testabdeckung (garantiert -5 5 LSB Offsetabgleich durch Design) 117 PHI12 Abgleichbereich Phasenkorrektur CH1 gegen CH2 ±20.2 °

- 7. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 7/39 KENNDATEN Betriebsbedingungen: VDD = 4.3...5.5 V, Tj = -40...125 °C, IBN auf 200 µA kalibriert, wenn nicht anders angegeben. Kenn- Formel- Benennung Bedingungen Einh. Nr. zeichen Min. Typ Max. 118 ∆PHI12 Inkrementschrittweite der Pha- 0.63 ° senkorrektur 119 INL(PHI12) Integraler Linearitätsfehler der eingeschränkte Testabdeckung (garantiert -0.8 0.8 ° Phasenkorrektur durch Design) 120 fin() Zulässige Maximale Eingangsfre- analoger Signalpfad 200 kHz quenz 121 Vout(X2) Ausgangsspannung an X2 BIASEX = 10, I(X2) = 0, bezogen auf VREFin12 95 100 105 % 122 Vin(X2) Zuässige Eingangsspannung an BIASEX = 11 0.5 VDDS V X2 −2 123 Rin(X2) Eingangswiderstand an X2 BIASEX = 11, RIN0(3:0) = 0x01, RIN12(3:0) = 20 27 30 kΩ 0x01 Sinus-Digital-Wandlung 201 AAabs Absolute Winkelgenauigkeit bezogen auf 360° Eingangssignale, ideale 0.9 1.8 ° Signalform, quasistatisches Signal, kalibrierte Signalkonditionierung, SELHYS = 0 202 AArel Relativer Winkelfehler bezogen auf Ausgangsperiode T (siehe Bild 1), ideale Signalform, quasistatische Signale; bei 4 Flanken pro Periode 10 % bei 100 Flanken pro Periode <0.5 10 % bei 384 Flanken pro Periode 10 % bei 400 Flanken pro Periode <2 10 % 203 AAR Wiederholgenauigkeit siehe 201, VDD = const., Tj = const. 0.1 ° Leitungstreiber PA, NA, PB, NB, PZ, NZ 501 Vs()hi Sättigungsspannung hi Vs() = VDD - V(); SIK(1:0) = 00, I() = -1.2 mA 200 mV SIK(1:0) = 01, I() = -4 mA 200 mV SIK(1:0) = 10, I() = -20 mA 400 mV SIK(1:0) = 11, I() = -50 mA 700 mV 502 Vs()lo Sättigungsspannung lo SIK(1:0) = 00, I() = 1.2 mA 200 mV SIK(1:0) = 01, I() = 4 mA 200 mV SIK(1:0) = 10, I() = 20 mA 400 mV SIK(1:0) = 11, I() = 50 mA 700 mV 503 Isc()hi Kurzschlussstrom hi V() = 0 V; SIK(1:0) = 00 -4 -1.2 mA SIK(1:0) = 01 -12 -4 mA SIK(1:0) = 10 -60 -20 mA SIK(1:0) = 11 -150 -50 mA 504 Isc()lo Kurzschlussstrom lo V() = VDD; SIK(1:0) = 00 1.2 4 mA SIK(1:0) = 01 4 12 mA SIK(1:0) = 10 20 60 mA SIK(1:0) = 11 50 150 mA 505 tr() Anstiegszeit RL = 100 Ω nach GND; SSR(1:0) = 00 5 20 ns SSR(1:0) = 01 5 40 ns SSR(1:0) = 10 20 140 ns SSR(1:0) = 11 50 350 ns 506 tf() Abfallzeit RL = 100 Ω nach VDD; SSR(1:0) = 00 5 20 ns SSR(1:0) = 01 5 40 ns SSR(1:0) = 10 30 140 ns SSR(1:0) = 11 50 350 ns 507 Ilk()tri Leckstrom TRIHL(1:0) = 11, Tristate 20 100 µA 508 IIk()rev Leckstrom verpolte Versorgungsspannung 100 µA 509 Rin()cal Innenwiderstand für Testsignale Betriebsart Calibration 1, 2, 3 2.5 4 kΩ 510 I()cal Zulässige Testsignal-Belastung Betriebsart Calibration 1, 2, 3 -3 3 µA 511 tclk()lo Taktsignaldauer lo für CP, CPD, Betriebsart Mode 191/193; CPU MTD = 0x0 110 ns MTD = 0x7 800 ns 512 tw()hi Tastverhältnis bezogen auf Ausgangsperiode T, siehe Bild 1 50 %

- 8. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 8/39 KENNDATEN Betriebsbedingungen: VDD = 4.3...5.5 V, Tj = -40...125 °C, IBN auf 200 µA kalibriert, wenn nicht anders angegeben. Kenn- Formel- Benennung Bedingungen Einh. Nr. zeichen Min. Typ Max. 513 tAB Phasenlage A gg. B siehe Bild 1 25 % 514 tMTD Mindestflankenabstand Flanke zu Flanke, siehe Bild 1; MTD = 0x0, IBN auf 200 µA kalibriert 220 ns MTD = 0x0, IBN auf 220 µA kalibriert 200 ns 515 ∆t()MTD Toleranz Mindestflankenabstand Nennwerte in Tabelle 52 -15 15 % 516 ∆t()MTD Variation Mindestflankenabstand Veränderung gg. VDD = 5 V, Tj = 27 °C über +/- 2 % VDD = 4.3...5.5 V oder Tj = -40...125 °C Signalpegel-Regler ACO 601 Vs()hi Sättigungsspannung hi Vs() = VDD - V(); ADJ(8:0) = 0x11F, I(ACO) = -5 mA 1 V ADJ(8:0) = 0x13F, I(ACO) = -10 mA 1 V ADJ(8:0) = 0x15F, I(ACO) = -25 mA 1 V ADJ(8:0) = 0x17F, I(ACO) = -50 mA 1.2 V 602 Isc()hi Kurzschlussstrom hi V() = 0 ... VDD - 1 V; ADJ(8:0) = 0x11F -10 -5 mA ADJ(8:0) = 0x13F -20 -10 mA ADJ(8:0) = 0x15F -50 -25 mA V() = 0 ... VDD - 1.2 V; ADJ(8:0) = 0x17F -100 -50 mA 603 It()min Überwachung Regelbereich 1: bezogen auf Bereich ADJ(6:5) 3 %Isc untere Grenze 604 It()max Überwachung Regelbereich 2: bezogen auf Bereich ADJ(6:5) 90 %Isc obere Grenze 605 Vt()min Überwachung Signalpegel 1: bezogen auf Vscq() 40 %Vpp untere Grenze 606 Vt()max Überwachung Signalpegel 2: bezogen auf Vscq() 130 %Vpp obere Grenze Bias-Stromquelle und Referenzspannungen 801 IBN Bias-Stromquelle Calibration 1, I(NB) gg. VDDS; CFGIBN = 0x0 110 µA CFGIBN = 0xF 370 µA IBN bei T = 25 °C abgeglichen 180 200 220 µA 802 VBG Interne Bandgap-Referenz 1.2 1.25 1.3 V 803 VPAH Referenzspannung 45 50 55 %VDDS 804 V05 Referenzspannung V05 450 500 550 mV 805 V025 Referenzspannung V025 50 %V05 Power-Down-Reset 901 VDDon Einschaltschwelle VDD, System- zunehmende Spannung an VDD 3.6 4.0 4.3 V freigabe 902 VDDoff Abschaltschwelle VDD, Power- abnehmende Spannung an VDD 3.0 3.5 3.8 V Down-Reset 903 VDDhys Hysterese 0.4 V Fehlersignal Eingang/Ausgang, Pin ERR B01 Vs()lo Sättigungsspannung lo gegen GND, I() = 4 mA 0.4 V B02 Isc()lo Kurzschlussstrom lo gegen GND, V(ERR) ≤ VDD 4 5 8 mA B03 Isc() Low-Side Quellenstrom für gegen GND, V(ERR) > VTMon Datenausgabe L-Zustand 2 mA Z-Zustand 0 mA B04 Vt()hi Eingangsschwellspannung hi gegen GND 2 V B05 Vt()lo Eingangsschwellspannung lo gegen GND 0.8 V B06 Vt()hys Eingangshysterese Vt()hys = Vt()hi − Vt()lo 300 500 mV B07 Ipu() Eingangs-Pull-Up-Strom V() = 0...VDD − 1 V, EPU = 1 -400 -300 -200 µA B08 Vpu() Pull-Up-Spannung Vpu() = VDD − V(), I() = -5 µA, EPU = 1 0.4 V B09 VTMon Einschaltschwelle Testmodus zunehmende Spannung an ERR VDD + V 2

- 9. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 9/39 KENNDATEN Betriebsbedingungen: VDD = 4.3...5.5 V, Tj = -40...125 °C, IBN auf 200 µA kalibriert, wenn nicht anders angegeben. Kenn- Formel- Benennung Bedingungen Einh. Nr. zeichen Min. Typ Max. B10 VTMoff Abschaltschwelle Testmodus abnehmende Spannung an ERR VDD + V 0.5 B11 VTMhys Hysterese Testmodus VTMhys = VTMon − VTMoff 0.15 0.3 V B12 fclk() Signalfrequenz zur ENFAST = 0 120 160 200 kHz Datenausgabe ENFAST = 1 480 640 800 kHz B13 tp(ERR)in Sperrzeit für Verarbeitung einer nach dem Einschalten (VDD > VDDon) 10 ms Systemfehler-Meldung an ERR Verpolungsschutz und Spannungsschalter VDDS, GNDS C01 Vs() Sättigungsspannung gg. VDD Vs(VDDS) = VDD − V(VDDS); I(VDDS) = -10...0 mA 150 mV I(VDDS) = -20...-10 mA 250 mV C02 Vs() Sättigungsspannung gg. GND Vs(GNDS) = V(GNDS) − GND; I(GNDS) = 0...10 mA 150 mV I(GNDS) = 10...20 mA 200 mV C03 Irev(VDD) Stromaufnahme bei Verpolung V(VDD) = −5.5 V...−4.3 V -1 0 mA Serielle Konfigurations-Schnittstelle SCL, SDA D01 Vs()lo Sättigungsspannung lo I = 4 mA 400 mV D02 Isc()lo Kurzschlussstrom lo 4 75 mA D03 Vt()hi Eingangsschwellspannung hi 2 V D04 Vt()lo Eingangsschwellspannung lo 0.8 V D05 Vt()hys Eingangshysterese Vt()hys = Vt()hi − Vt()lo 300 500 mV D06 Ipu() Eingangs-Pull-Up-Strom V() = 0...VDDS − 1 V -600 -300 -60 µA D07 Vpu() Pull-Up-Spannung Vpu() = VDDS − V(), I() = -5 µA 0.4 V D08 fclk() Taktfrequenz an SCL ENFAST = 0 60 80 100 kHz ENFAST = 1 240 320 400 kHz D09 tbusy()cfg Dauer der Konfigurationsphase IBN nicht abgeglichen, EEPROM-Zugriff ohne Lesefehler, Zeit bis Ausgangsfunktion; ENFAST = 0 36 48 ms ENFAST = 1 24 34 ms D10 tbusy()err Ende der I2C-Kommunikation; IBN nicht abgeglichen; Zeit bis Freigabe der I2C-Slave V(SDA) = 0 V 4 12 ms Funktion V(SCL) = 0 V oder Arbitrierung verloren indef. ms kein EEPROM 45 135 ms CRC-Fehler 95 285 ms D11 tp() Übernahme der Masterfunktion SCL ohne Taktsignal: V(SCL) = konstant; nach I2C-Protokollfehler IBN nicht abgeglichen 25 80 240 µs IBN auf 200µA abgeglichen 64 80 120 µs Temperatur-Überwachung E01 VTs Sensorspannung VTs() = VDDS − V(PA), Temperatursensor Calibration 3, ohne Last; Tj = -40 °C 740 770 790 mV Tj = 27 °C 620 650 670 mV Tj = 100 °C 460 520 540 mV E02 TCs Temperaturkoeffizient Sensor- -1.8 mV/K spannung E03 VTth Einschaltschwellspannung für VTth() = VDDS − V(NA), Tj = 27 °C, Temperaturwarnung Calibration 3, ohne Last; CFGTA(3:0) = 0x0 260 310 360 mV CFGTA(3:0) = 0xF 470 550 630 mV E04 TCth Temperaturkoeffizient der Ein- 0.06 %/K schaltschwellspannung E05 Tw Einschaltschwelle der CFGTA(3:0) = 0x0 125 140 °C Temperaturwarnung CFGTA(3:0) = 0xF 65 80 °C E06 Thys Temperaturhysterese Warnung 80 °C < Tj < 125 °C 10 15 25 °C E07 ∆T Relative Abschalttemperatur ∆T = Toff − Tw 5 15 25 °C

- 10. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 10/39 tAB tMTD B A twhi AArel AArel T Bild 1: Definition des relativen Winkelfehlers und Mindestflankenabstand

- 11. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 11/39 PROGRAMMIERUNG Registerbelegung, Übersicht . . . . . . . . . . . . . . Seite 12 Signalkonditionierung CH0 (X1, X2) . . . . . . . Seite 24 GR0: Verstärkungbereich CH0 (grob) Serielle Konfigurations-Schnittstelle . . . . . . Seite 14 GF0: Verstärkungsfaktor CH0 (fein) ENFAST: I2 C Fast-Mode Freigabe VOS0: Offset-Bezugsquelle CH0 ENSL: I2 C Slave-Mode Freigabe DEVID: Device-ID für EEPROM mit OR0: Offset-Abgleichbereich CH0 (grob) Konfigurationsdaten (z. B. 0x50) OF0: Offset-Faktor CH0 (fein) CHKSUM: CRC über Konfigurationsdaten Signalpegel-Regler . . . . . . . . . . . . . . . . . . . . . . . . Seite 25 (Adressbereich 0x00 bis 0x2F) ADJ: Programmierung der ACO Funktion CHPREL: Chip Release END: Konfigurationsfreigabe Sinus-Digital-Wandlung . . . . . . . . . . . . . . . . . . . Seite 26 SELRES: Auflösung Kalibrierung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Seite 16 SELHYS: Hysterese CFGIBN: Bias-Strom CFGTA: Temperatur-Überwachung Ausgabelogik Quadratursignale . . . . . . . . . . . Seite 27 CFGABZ: Ausgabelogik Betriebsarten . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Seite 17 CFGZPOS: Nullsignal-Positionierung MODE: Betriebsarten ENZFF: Nullsignal-Synchronisation Eingangskonfiguration und Signalpfad-Multiplexer . . . . . . . . . . . . . . . . . . . . .Seite 19 Ausgangseinstellungen Quadratursignale Seite 29 INMODE: Umschaltung differenzielle / MTD: Mindestflankenabstand referenz-bezogene Signale SIK: Treiber Kurzschlussstrom RIN12: I/U-Modus und Eingangswiderstand SSR: Treiber Slewrate CH1, CH2 TRIHL: Treiber Betriebsart BIAS12: Referenzspannung CH1, CH2 Fehlerüberwachung und Alarmausgabe . . Seite 30 RIN0: I/U-Modus und Eingangswiderstand EMTD: Minimale Alarmanzeigedauer CH0 EPH: Alarm-Ein-/Ausgabe-Logik BIAS0: Referenzspannung CH0 EPU: Pull-Up-Freigabe für Alarmausgang BIASEX: Eingangsseitige Referenzauswahl INVZ: Invertierung Nullimpuls EMASKA: Fehlermaske für Alarmanzeige (Pin MUXIN: Zuordnung Eingang zum Kanal: ERR) X3...X6 zu CH1, CH2 EMASKE: Fehlermaske für Protokoll (EEPROM) EMASKO: Fehlermaske für Treiberabschaltung Signalkonditionierung CH1, CH2 (X3...X6) Seite 21 PDMODE: Treiberaktivierung nach GR12: Verstärkungsbereich CH1, CH2 (grob) Wiedereinschalten GF1: Verstärkungsfaktor CH1 (fein) LINECNT: Strichzahl (Linien) zwischen 2 GF2: Verstärkungsfaktor CH2 (fein) Nullimpulsen VOS12: Offset-Bezugsquelle CH1, CH2 ERR1: Fehlerprotokoll: Erster Fehler VDC1: Mittenpotential CH1 ERR2: Fehlerprotokoll: Letzter Fehler VDC2: Mittenpotential CH2 ERR3: Fehlerprotokoll: Historie OR1: Offset-Abgleichbereich CH1 (grob) OF1: Offsetfaktor CH1 (fein) Testmodus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Seite 33 OR2: Offset-Abgleichbereich CH2 (grob) EMODE: Testmodus OF2: Offsetfaktor CH2 (fein) EMODE2: Register- und Adressauswahl für PH12: Phasenabgleich CH1 gg. CH2 Testmodus

- 12. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 12/39 REGISTERBELEGUNG ÜBERSICHT Adr Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Serielle Konfigurations-Schnittstelle 0x00 ENFAST DEVID(6:0) Kalibrierung 0x01 CFGIBN(3:0) CFGTA(3:0) Betriebsarten 0x02 END 1 0 ENZFF MODE(3:0) Eingangskonfiguration 0x03 0 0 0 0 INVZ INMODE MUXIN(1:0) Signalkonditionierung CH1, CH2 0x04 GF2(4:0) GR12(2:0) 0x05 GF1(3:0) 0 0 0 0 0x06 VDC1(0) 0 0 0 0 GF1(6:4) 0x07 0 0 0 VDC1(5:1) 0x08 OR1(0) VDC2(5:0) 0 0x09 OF1(3:0) 0 0 0 OR1(1) 0x0A 0 0 OR2(1:0) OF1(7:4) 0x0B OF2(6:0) 0 0x0C PH12(2:0) 0 0 0 0 OF2(7) 0x0D BIASEX(1:0) 0 1 1 PH12(5:3) 0x0E 1 BIAS12 VOS12(1:0) RIN12(3:0) Signalpegel-Regler 0x0F ADJ(0) — 0 1 0 0 0 0 0x10 ADJ(8:1) Signalkonditionierung CH0 0x11 GF0(4:0) GR0(2:0) 0x12 OF0(5:0) OR0(1:0) 0x13 0 BIAS0 VOS0(1:0) RIN0(3:0) Fehlerüberwachung und Alarmausgabe 0x14 EMASKA(7:0) 0x15 EMODE(1:0) EMTD(2:0) EPH EMASKA(9:8) 0x16 EMASKO(7:0) 0x17 EMASKE(3:0) ENSL EPU EMASKO(9:8) 0x18 EMODE2 PDMODE EMASKE(9:4) Nullsignal-Ausgabe 0x19 CFGABZ(7:0) 0x1A CFGZPOS(7:0) Sinus-Digital-Wandlung, Mindestflankenabstand 0x1B SELRES(7:0) 0x1C — SELRES(14:8) 0x1D MTD(3:0) SELHYS(3:0) Treibereinstellungen 0x1E — — SIK(1:0) SSR(1:0) TRIHL(1:0)

- 13. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 13/39 ÜBERSICHT Adr Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Linienzähler 0x1F LINECNT(7:0) 0x20 — — LINECNT(13:8) Reserviert 0x21 0 0 0 0 1 0 0 0 0x22 — — — — — — — — 0x23 — — — — — — — — 0x24 reserviert fuer applikationsspezifische Daten 0x25 reserviert fuer applikationsspezifische Daten 0x26 reserviert fuer applikationsspezifische Daten 0x27 reserviert fuer applikationsspezifische Daten 0x28 reserviert fuer applikationsspezifische Daten 0x29 reserviert fuer applikationsspezifische Daten 0x2A reserviert fuer applikationsspezifische Daten 0x2B reserviert fuer applikationsspezifische Daten 0x2C reserviert fuer applikationsspezifische Daten 0x2D reserviert fuer applikationsspezifische Daten 0x2E reserviert fuer applikationsspezifische Daten Prüfsumme 0x2F EEPROM: CHKSUM(7:0) / ROM: CHPREL(7:0) Fehlerspeicher 0x30 ERR1(7:0) 0x31 ERR2(5:0) ERR1(9:8) 0x32 ERR3(3:0) ERR2(9:6) 0x33 — — ERR3(9:4) Hinweis Nach dem Einschalten enthält das Baustein-RAM zunächst zufällige Werte. Tab. 4: Registerbelegung

- 14. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 14/39 SERIELLE KONFIGURATIONS-SCHNITTSTELLE Die serielle Konfigurations-Schnittstelle besteht aus ENSL Adr 0x17, bit 3 den beiden Pins SCL und SDA und ermöglicht Code Funktion Schreib- und Lesezugriffe auf ein EEPROM mit I2 C- 0 Normalbetrieb Schnittstelle. Mit dem Registerbit ENFAST kann die 1 I2 C-Slave-Mode Freigabe (Device-ID 0x55) Auslesegeschwindigkeit gewählt werden. Tab. 6: Modus Konfigurations-Schnittstelle ENFAST Adr 0x00, bit 7 Code Funktion In das Register DEVID(6:0) (Adr 0x00) ist die Device- 0 Normale Taktfrequenz, f(SCL) ca. 80 kHz ID für das EEPROM eintragbar, aus dem iC-MQ die 1 Hohe Taktfrequenz, f(SCL) ca. 320 kHz Konfiguration nach Verlassen des Testmodus bezie- Hinweise Zur In-Circuit Programmierung benötigen die hen soll (siehe Seite 33). Die darin gespeicherte DE- Busleitungen SCL und SDA Pull-Up-Widerstände. VID wird nachfolgend übernommen. Für Leitungskapazitäten bis 170 pF genügen: 4.7 kΩ für 80 kHz Taktfrequenz Beispiel der CRC Berechnungsroutine 2 kΩ für 320 kHz Taktfrequenz Die Pull-Up-Widerstände dürfen 1.5 kΩ nicht unterschreiten. Zur Signaltrennung ist eine unsigned char ucDataStream = 0 ; Massebahn zwischen SCL und SDA i n t iCRCPoly = 0x11D ; unsigned char ucCRC=0; empfehlenswert. int i = 0; Zur Programmierung des EEPROMs muss iC-MQ ebenfalls Versorgungsspannung erhalten (5 V and ucCRC = 1 ; / / s t a r t v a l u e ! ! ! VDD). f o r ( iReg = 0 ; iReg <47; iReg ++) { ucDataStream = ucGetValue ( iReg ) ; Tab. 5: Taktfrequenz Konfigurations-Schnittstelle f o r ( i =0; i <=7; i ++) { i f ( ( ucCRC & 0x80 ) ! = ( ucDataStream & 0x80 ) ) ucCRC = (ucCRC << 1 ) ^ iCRCPoly ; else Nach dem Einschalten der Versorgung sind die Aus- ucCRC = (ucCRC << 1 ) ; ucDataStream = ucDataStream << 1 ; gänge von iC-MQ hochohmig (Tristate*) bis eine gülti- } ge Konfiguration aus dem EEPROM mit der Device-ID } 0x50 ausgelesen wurde. EEPROM-Auswahl Bitfehler im Speicherbereich 0x00 bis 0x2F werden Folgende Mindestanforderungen müssen erfüllt sein: durch den im Register CHKSUM(7:0) hinterlegten CRC-Wert erkannt (Adr 0x2F im EEPROM, CRC- • Funktion ab 3.3 bis 5 V, I2 C-Schnittstelle Polynom “1 0001 1101“ mit Startwert "1"). • Mindestens 512 bit, 64x8 (genutzter Adressbereich: 0x00 bis 0x3F) Werden die gelesenen Konfigurationsdaten nicht durch den CRC-Wert bestätigt, wird der Einlesevor- • Unterstützung von Page Write mit mindestens gang wiederholt. Sind nach dem vierten Einlesevor- 4 Byte großen Pages. Andernfalls muss auf die gang keine gültigen Konfigurationsdaten vorhanden, Protokollierung von Fehlern im EEPROM ver- beendet iC-MQ den EEPROM-Zugriff und wechselt in zichtet werden (EMASKE = 0x0). den I2 C-Slave-Modus. Dieser Wechsel erfolgt spätes- tens nach 150 ms (siehe Kenndaten D11), zum Bei- • Device ID 0x50 "1010 000", keine Belegung von spiel wenn kein EEPROM angeschlossen ist. 0x55 (A2...A0 = 0). Andernfalls kann iC-MQ nicht über 0x55 im I2 C Slave-Mode angesprochen werden. Für Bausteine, die eine gültige Konfiguration aus dem EEPROM laden, entscheidet das Register-Bit ENSL über die Freigabe der I2 C-Slave-Funktion. Bausteinempfehlung: Atmel AT24C01B, ST M24C01W

- 15. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 15/39 I2 C-Slave-Modus (ENSL = 1) Register Lesezugriff im I2 C-Slave-Modus (ENSL = 1) In diesem Modus verhält sich iC-MQ wie ein I2 C- Adresse Inhalt Slave mit der Device-ID 0x55 und die Konfigurations- 0x00-0x21 Konfiguration: Registeradressen 0x00-0x21 Schnittstelle erlaubt Schreib- und Lese-Zugriffe auf iC- 0x22-0x2A Nicht verfügbar MQ’s interne Register. 0x2B-0x2E Konfiguration: Registeradressen 0x2B-0x2E 0x2F Chipversion (ROM) Zur Überprüfung der Chipversion ist eine Kennung im 0x30-0x33 Konfiguration: Registeradressen 0x30-0x33 ROM hinterlegt und über Adresse 0x2F lesbar; ein 0x34-0x3A Nicht verfügbar Schreibzugriff auf diese Adresse ist nicht zulässig. 0x3B-0x3E Konfiguration: Registeradressen 0x2B-0x2E 0x3F Chipversion (ROM) CHPREL Adr 0x2F, bit 7:0 (ROM) 0x40-0x43 Aktueller Fehlerspeicher Code Chipversion 0x44-0x7F Nicht verfügbar 0x00 Nicht verfügbar 0x04 iC-MQ 3 Tab. 9: RAM-Lesezugriff 0x08 iC-MQ X 0x09 iC-MQ X1 Register Schreibzugriff im I2 C-Slave-Modus (ENSL = 1) Adresse Zugriff und Bedingungen Tab. 7: Chipversion 0x00 Änderungen uneingeschränkt möglich 0x01 Änderungen möglich END Adr 0x02, bit 7 (falsche Werte für CFGIBN können die Funtion beeinträchtigen) Code Funktion 0x02 Änderung der Bits 6:0 zulässig wenn Sin/D- 0 Sin/D-Wandlung und Ausgangstreiber Wandlerfunktion gestoppt (END = 0, bzw. Bit 7); ausgeschaltet Neustart der Sin/D-Wandlung durch Änderung von (ungültige Konfigurationsdaten im RAM) END (Bit 7) zulässig, wenn Betriebsart unverändert 1 Neustart Sin/D-Wandlung, Ausgangstreiber aktiv (Bits 6:0 konstant) (gültige Konfigurationsdaten im RAM) 0x03-0x16 Änderungen uneingeschränkt möglich 0x17 Änderung der Bits 7:4 und 2:0 zulässig Tab. 8: Konfigurationsfreigabe (ENSL, Bit 3 muss 1 gesetzt bleiben) 0x18 Änderungen uneingeschränkt möglich 0x19-0x21 Änderungen zulässig wenn Sin/D-Wandlerfunktion gestoppt (END = 0) 0x2B-0x2E Änderungen uneingeschränkt möglich Sonstige Keine Änderungen zulässig Tab. 10: RAM-Schreibzugriff

- 16. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 16/39 BIAS-STROMQUELLE UND TEMPERATURSENSOR-KALIBRIERUNG Bias-Strom Widerstands am Pin ERR erzeugt werden. Die Kalibrierung der Bias-Stromquelle in der Betriebs- art Calibration 1 (siehe Tabelle 13) ist Vorausset- Beispiel: VTs(T1 ) ist ca. 650 mV, gemessen von VDDS zung für die Einhaltung der ausgewiesenen elektri- gegen PA, bei T1 = 25 °C; schen Kenndaten und mitbestimmend für das Chip- Timing (z.B. SCL-Taktfrequenz). Zur Einstellung wird Anschliessend wird die benötigte Vergleichsspannung der IBN Bias-Strom über einen 10-kΩ-Widerstand von VTth(T1 ) berechnet. In diese Berechnung geht die ge- Pin VDDS gg. Pin NB gemessen. Der Sollwert ist wünschte Warnungstemperatur T2 , die Temperaturko- 200 µA, was einer Messspannung von 2 V entspricht. effizienten TCs und TCth (für TCs und TCth siehe el. Kenndaten Abschnitt E), sowie der Messwert VTs(T1 ) CFGIBN Adr 0x01, bit 7:4 ein: 31 31 Code k IBN ∼ 39−k Code k IBN ∼ 39−k 0x0 79 % 0x8 100 % 0x1 81 % 0x9 103 % VTs(T1 ) + TCs · (T2 − T1 ) VTth(T1 ) = 0x2 84 % 0xA 107 % 1 + TCth · (T2 − T1 ) 0x3 86 % 0xB 111 % 0x4 88 % 0xC 115 % Beispiel: Für T2 = T1 + 100 K muss VTth(T1 ) auf 0x5 91 % 0xD 119 % 443 mV programmiert werden. 0x6 94 % 0xE 124 % 0x7 97 % 0xF 129 % Die Vergleichsspannung VTth(T1 ) steht für eine hoch- ohmige Messung (10 MΩ) am Ausgangspin NA zur Tab. 11: Bias-Strom Verfügung (Messung gg. VDDS) und muss durch Pro- grammierung von CFGTA(3:0) auf den berechneten Temperatursensor Wert eingestellt werden. Die Kalibrierung der Temperaturüberwachung erfolgt in der Betriebsart Calibration 3. Beispiel: Die Änderung von VTth(T1 ) von 310 mV (ge- messen für CFGTA(3:0)= 0x0) auf 443 mV entspricht Für die Einstellung auf die gewünschte Warnungstem- 143 %, der nächstliegende Wert für CFGTA ist 0x9; peratur T2 wird zunächst die Sensorspannung VTs des Temperatursensors bestimmt, bei der die Warnungs- CFGTA Adr 0x01, bit 3:0 meldung erfolgt. Dazu wird am Pin PA eine Span- Code k VTth ∼ 65+3k 65 Code k VTth ∼ 65+3k 65 nungsrampe von VDDS in Richtung GNDS durchfah- 0x0 100 % 0x8 137 % ren, bis Pin ERR die Warnungsmeldung anzeigt. Dazu 0x1 105 % 0x9 142 % sind die folgenden Einstellungen erforderlich: EMAS- 0x2 109 % 0xA 146 % KA = 0x20, EMTD = 0x00, EPH = 0x00. 0x3 114 % 0xB 151 % 0x4 118 % 0xC 155 % Das Signal an ERR wechselt zunächst von Tri-State 0x5 123 % 0xD 160 % nach Low (bei Erreichen der Warnungsschwelle VTs) 0x6 128 % 0xE 165 % und nachfolgend von Low nach Tri-State (bei Über- 0x7 132 % 0xF 169 % schreitung der internen Hysterese, was für die Kali- Hinweise Bei CFGTA = 0xF ist Toff 80 °C typ., bei CFGTA = 0x0 ist Toff 155 °C typ. brierung nicht relevant ist). Um Verwechslungen aus- zuschliessen, sollte ein eindeutiger Zustandswechsel (von Low nach High) mit Hilfe eines externen Pull-Up- Tab. 12: Temperatur-Überwachung

- 17. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 17/39 BETRIEBSARTEN iC-MQ stellt verschiedene Betriebsarten zur Verfü- mit Nullimpuls erfolgt. Nur in diesen beiden Betriebs- gung, die Funktion der Ausgänge PA, NA, PB, NB, PZ, arten sind die Leitungstreiber sowie der Verpolungs- NZ und ERR wird hierfür umgeschaltet. schutz aktiv. Zur Winkelwertausgabe im Normalbetrieb sind zwei Zur Konditionierung der Eingangssignale, zur Kalibrie- Betriebsarten wählbar: Mode 191/193 stellt Steuersi- rung sowie zum Testen von iC-MQ sind Calibration gnale für 74HC191 oder 74HC193 kompatible Zähler- und Test Betriebsarten wählbar. Es werden digitale bausteine zur Verfügung, während im Mode ABZ die und analoge Testsignale zur Verfügung gestellt, letz- inkrementale Ausgabe als Encoder-Quadratursignal tere müssen stets hochohmig gemessen werden. MODE(3:0) Adr. 0x02; Bit 3:0 Code Betriebsart PA NA PB NB PZ NZ ERR 0x00 Mode ABZ A not(A) B not(B) Z not(Z) ERR 0x0F Mode 191/193 CPD CPU CP nU/D MR nPL ERR 0x01 Calibration 1 TANAZ(2) VREFIZ VREFISC IBN PCH0 NCH0 IERR 0x02 Calibration 2 PCH1 NCH1 PCH2 NCH2 VDC1 VDC2 0x03 Test 3* VPAH VPD — CGUCK IPF V05 IERR 0x04 Test 4* PS_out NS_out PC_out NC_out PZO NZO IERR 0x05 Test 5* PSIN NSIN PCOS NCOS PZO NZO IERR 0x06 Test 6* PCH1I NCH1I PCH2I NCH2I VDC1 VDC2 res. 0x07 Calibration 3 VTs VTth — — VTTFE VTTSE ERR 0x08 Lo-Signal alle Ausgänge sowie SCL, SDA, ERR auf Low 0x09 Hi-Signal alle Ausgänge auf High 0x0A Test 10* TP CLK6 CLK1 CLK3/8 ZIn CLK4 0x0B Systemtest* A4 A8 B4 B8 ZIn TP1 ERR 0x0C Test 12* A not(A) B not(B) Z not(Z) ERR 0x0D — — — — — — — — 0x0E IDDQ Test* alle PU/PD-Widerstände deaktiviert, Oszillator und Analogversorgung deaktiviert Hinweise *) Testfunktionen für iC-Haus Bausteintest. Tab. 13: Betriebsarten Mode ABZ Mode 191/193 In der Betriebsart Mode ABZ werden A/B-Signale er- Pin Signal Beschreibung zeugt und über PA, NA und PB, NB ausgegeben. PA CPD Clock Down Pulse Gleichzeitig steht ein frei konfigurierbares Nullsignal NA CPU Clock Up Pulse an den Pins PZ und NZ zur Verfügung. Die differen- PB CP Clock Pulse tiellen RS422-Leitungstreiber sind aktiv, ein Nx-Pin lie- NB nU/D Count Direction (0: up, 1: down) fert stets das zum Px-Pin invertierte, komplementäre PZ MR Asynch. Master Reset (active high) Signal. Signal ist ’1’ wenn Nullpos. erreicht, sonst ’0’. NZ nPL Asynch. Parallel Load Input (active low) / Reset (active low) Signal ist ’0’ wenn Nullpos. erreicht, sonst ’1’. Tab. 14: Betriebsart für 74HC191 oder 74HC193 kom- patible Zählerbausteine. Mode 191/193 In der Betriebsart Mode 191/193 liefern die Ausgabe- Calibration 1, 2, 3 pins Steuersignale für 74HC191 oder 74HC193 kom- Diese Betriebsarten werden zur Konditionierung der patible Zählerbausteine, gemäß der folgenden Tabel- Eingangssignale und zur Kalibrierung von iC-MQ ver- le. Die Treiberfähigkeit (SIK) sowie die Slewrate (SSR) wendet. In der Betriebsart Calibration 1 ist der BIAS- der Ausgangstreiber müssen so gewählt werden, dass Strom (IBN) messbar und es stehen die analogen Si- die Taktpulse mit typisch 50 ns Low-Signal ausgege- gnale der Nullspur nach dem Signalabgleich zur Ver- ben werden können (siehe El. Kenndaten 511). fügung (PCH0, NCH0).

- 18. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 18/39 In der Betriebsart Calibration 2 werden die kondi- Auflösung 8 alle 45 Grad einen Schaltpunkt. Das Ka- tionierten Sinus- und Cosinus-Signale ausgegeben librierungsziel ist ein Tastverhältnis von jeweils exakt (PCH1, NCH1, PCH2, NCH2). Zusätzlich steht das 50% (für A4 , B4 und A8 , B8 ). Für den Systemtest sind Mittenpotential VDC1 der Abgleichschaltung CH1 und die folgenden Einstellungen erforderlich: das Mittenpotential VDC2 der Abgleichschaltung CH2 zur Verfügung (Abgleichbeschreibung siehe Seite 21). • MODE = 0x0B In der Betriebsart Calibration 3 werden die internen Si- gnale der Temperaturüberwachung zur Verfügung ge- • SELRES = 0x1B0 stellt. Die Kalibrierung der Bias-Stromquelle und der • SELHYS = 0xF Temperaturüberwachung ist auf Seite 16, der Abgleich der Nullspur auf Seite 24 beschrieben. • CFGABZ(7:4) = ’0000’ TEST 6 Die Eingangsspannungen an den Pins X3 bis X6 kön- Systemtest nen in der Betriebsart Test 6 überprüft werden. Dazu Pin Signal Beschreibung sind die folgenden Einstellungen erforderlich: PA A4 Offset CH1 NA A8 Phasenabweichung von 90° zwischen CH1 und CH2 • GF1 = 0x0 PB B4 Offset CH2 • GF2 = 0x0 NB B8 Amplitudenabweichung zwischen CH1 und CH2 • Byte 0x05, Bit 3:0 = ’0000’ PZ ZIn Digitales Nullsignal, unmaskiert NZ TP1 Prüfung der Impulszahl (Linien) zwischen • Byte 0x0F, Bit 3 = ’1’ zwei Nullsignalen Lo-Signal: Prüfung aktiv (Zustand nach dem • Byte 0x0F, Bit 4 = ’0’ Einschalten) Hi-Signal: Prüfung beendet Die Fehleranzeige an ERR wird erst nach Systemtest dem zweiten Nullsignal gültig (Freigabe erforderlich). Diese Betriebsart ermöglicht die Einstellung der Si- gnalkonditionierung anhand komparierter Sinus- und Cosinus-Signale. Hierfür erzeugt der Interpolator in der Tab. 15: Digitale Kalibriersignale

- 19. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 19/39 EINGANGSKONFIGURATION Alle Eingangsstufen sind als Instrumentenverstärker ausgeführt und direkt für differenzielle Eingangssigna- le geeignet. Referenz-bezogene Eingangssignale kön- nen ebenfalls verarbeitet werden, der Eingang X2 kann als Referenzeingang geschaltet werden. Die Auswahl ob Strom- oder Spannungssignale verarbeitet werden erfolgt mit RIN12 und RIN0. INMODE Adr 0x03, bit 2 Code Funktion 0 Differenzielle Eingangssignale 1 Single-ended Eingangssignale * Bild 2: Signalkonditionierung Hinweis * Eingang X2 ist Referenz für alle Eingänge. Tab. 16: Eingangssignal-Modus Stromsignale RIN12 Adr 0x0E, bit 3:0 Im I-Modus wird an jedem Eingangspin ein Ein- RIN0 Adr 0x13, bit 3:0 gangswiderstand Rin() aktiv, der das Stromsi- Code Nominal Rin() Intern Rui() I/U Mode gnal in ein Spannungssignal umwandelt. Der Ein- –000 1.7 kΩ 1.6 kΩ Stromeingang gangswiderstand Rin() setzt sich aus einem Pin- –010 2.5 kΩ 2.3 kΩ Stromeingang Anschlusswiderstand und dem Widerstand Rui() zu- –100 3.5 kΩ 3.2 kΩ Stromeingang sammen, der an die einstellbare Vorspannungsquelle –110 4.9 kΩ 4.6 kΩ Stromeingang VREFin() geschaltet ist (BIASEX muss auf ’00’ gesetzt 1—1 20 kΩ 5 kΩ Spannungsein- sein). Die nebenstehende Tabelle zeigt die Wahlmög- gang lichkeiten; Rin() gibt den typischerweise resultierenden 0—1 hochohmig 1 MΩ Spannungsein- gang Eingangswiderstand an (siehe El. Kenndaten für Tole- ranzangaben). Der Eingangswiderstand sollte so ein- Tab. 17: I/U Modus und Eingangswiderstand gestellt werden, dass sich Mittenpotentiale VDC1 und VDC2 zwischen 125 mV und 250 mV ergeben (prüfbar im Modus Calibration 2). BIAS12 Adr 0x0E, bit 6 BIAS0 Adr 0x13, bit 6 Spannungssignale Code VREFin() Sensortyp Im U-Modus ist ein Spannungsteiler optional wähl- 0 2.5 V Lowside Stomsenke (I Mode) bar, der zu große Eingangsamplituden auf ca. 25 % 1 1.5 V Highside Stromquelle (I Mode) reduziert. Die Schaltung entspricht der Widerstands- Hinweis Gültig ausser für BIASEX=11 kette im I-Modus, deutlich vergrößert wird hier der Pin-Anschlusswiderstand. Für Sensoren, deren Offset- Tab. 18: Referenzspannung Kalibrierung proportional zu einer externen DC- Spannungsquelle erfolgen soll, ist über BIASEX die BIASEX Adr 0x0D, bit 7:6 Referenzquelle wählbar (für alle anderen Sensoren ist Code VREFin() Signal an X2 BIASEX auf ’00’ zu setzen). 00* 1.5 / 2.5 V Neg. Nullsignal (Index -), Eingang (intern) 10 1.5 / 2.5 V Referenzspg. VREFin12, Ausgang (intern) 11 extern Spannung an X2 wird zu VREFin Tab. 19: Eingangsseitige Referenzauswahl

- 20. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 20/39 SIGNALPFAD-MULTIPLEXER MUX_IN Calibration MUX_OUT X1 X2 PCH0i PCH0o INVZ PZO + 0 1 + ZIN NCH0i NCH0o VREFin0 - NZO - X3 MUXIN(0) 0 1 PCH2i PCH2o X4 + PC_out NCH2i NCH2o MUXIN(1) - NC_out 0 1 X5 PCH1i PCH1o + PS_out MUXIN(1) NCH1i NCH1o X6 0 1 - NS_out VDC1 VDC1 VREFin12 INMODE VDC2 VDC2 Bild 3: Funktionsweise der Multiplexer An den Pins X1, X2 werden die Signale für den Index- MUXIN Adr 0x03, bit 1:0 kanal CH0 eingespeist. Die Zuordnung der Pins X3 Code PCH1i NCH1i PCH2i NCH2i bis X6 zu den internen Kanälen CH1 und CH2 wählt 00 X4 X2 X3 X2 MUXIN. Für referenzbezogene Eingangssignale kann 01 nicht erlaubt INMODE aktiviert werden, wodurch X2 als Bezugssi- 10 nicht erlaubt gnal geschaltet wird. Zur Ausgabe erlaubt INVZ nach- 11 X4 X2 X5 X2 folgend die Invertierung der Signalphase für den Kanal CH0. Tab. 21: Eingangsmultiplexer für INMODE = 1 MUXIN Adr 0x03, bit 1:0 INVZ Adr 0x03, bit 3 Code PCH1i NCH1i PCH2i NCH2i Code PZO NZO 00 X4 X6 X3 X5 0 PCH0o NCH0o 01 nicht erlaubt 1 NCH0o PCH0o 10 X4 X5 X3 X6 11 X4 X3 X5 X6 Tab. 22: Invertierung Nullimpuls Tab. 20: Eingangsmultiplexer für INMODE = 0

- 21. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 21/39 SIGNALKONDITIONIERUNG CH1, CH2 Die für den Abgleich der Sinus-Signale benötigten analogen Spannungssignale können in der Betriebs- art Calibration 2 gemessen werden. Alternativ ste- GR12 Adr 0x04, bit 2:0 hen charakteristische digitale Testsignale für Offset-, Code Bereich RIN12=0x9 Bereich RIN12=0x9 Amplituden- und Phasenfehler in der Betriebsart Sys- 0x0 0.5 2.0 temtest zur Verfügung. 0x1 1.0 4.1 0x2 1.3 5.3 Verstärkungseinstellung 0x3 1.7 6.7 Die Verstärkung wird in vier Schritten eingestellt: 0x4 2.2 8.7 0x5 2.6 10.5 1. Die Nachführung der Sensor-Versorgung wird ab- 0x6 3.3 13.2 geschaltet und die Konstantstromquelle für den ACO- 0x7 4.0 16.0 Ausgang auf einen geeigneten Ausgangsstrom einge- stellt (Register ADJ; Stromwert nahe dem späteren Ar- Tab. 23: Verstärkungsbereich CH1, CH2 beitspunkt). GF2 Adr 0x04, bit 7:3 2. Der grobe Verstärkungsbereich wird ausgewählt, Code Faktor sodass intern Differenz-Signalamplituden von ca. 0x00 1.00 1 Vss entstehen (Signal Px gg. Nx, siehe Bild). 0x01 1.06 GF 2 ... 6.25 31 3. Anschließend wird über die Feinverstärkung GF2 0x1F 6.25 die CH2-Signalamplitude auf 1 Vss justiert. Tab. 24: Fein-Verstärkung CH2 4. Danach kann über die Feinverstärkung GF1 die CH1-Signalamplitude an die CH2-Signalamplitude GF1 Adr 0x06, bit 2:0, Adr 0x05, bit 7:4 angepasst werden. Es ergibt sich eine Gesamt- Code Faktor verstärkung für differentielle Eingangssignale von 0x00 1.0 GR12 * GFi. 0x01 1.015 GF 1 ... 6.25 124 0x7F 6.53 Tab. 25: Fein-Verstärkung CH1 Px VPx R0 VPNx Nx VNx GND Bild 4: Definition 1 Vss-Signal. Der Abschluss R0 muss während Test und Calibration Modes hochohmig sein.

- 22. iC-MQ PROGRAMMIERBARER 9-BIT Sin/Cos-INTERPOLATOR MIT RS422 TREIBER Ausgabe D3, Seite 22/39 Offsetabgleich Der Offsetabgleich-Bereich für CH1 und CH2 ist ab- Für den Offsetabgleich ist zuerst mit VOS12 die Be- hängig von der gewählten Quelle VOS12 und wird mit zugsquelle auszuwählen. Dafür stehen zwei Festspan- OR1 und OR2 eingestellt. Anschliessend erfolgt die nungen sowie zwei abhängige Quellen zur Verfügung. Kalibrierung für Sinus und Cosinus über die Fakto- Die Festspannungsquellen sind für externe Sensoren ren OF1 sowie OF2. Das Abgleichziel ist jeweils er- auszuwählen, die bereits selbstgeregelte und stabile reicht, wenn der DC-Anteil der Differenzsignale PCHi Signale anbieten. gg. NCHi zu Null wird. Zum Betrieb von Photosensoren in optischen Enco- OR1 Adr 0x09, bit 0; Adr 0x08, bit 7 dern bietet iC-MQ in Verbindung mit der geregelten OR2 Adr 0x0A, bit 5:4 Sensor-Stromquelle zur LED-Versorgung (Pin ACO) Code Bereich eine Offset-Nachführung über die abhängige Quelle 0x0 x1 VDC. Das VDC-Potential folgt höheren DC-Fotoströ- 0x1 x2 men automatisch. Für diese Funktion müssen die Mit- 0x2 x6 tenpotentiale VDC1 und VDC2 über den wählbaren k- 0x3 x12 Faktor auf einen minimalen AC-Anteil eingestellt wer- den (dieser Abgleich muss wiederholt werden, wenn Tab. 28: Offsetabgleich CH1, CH2 die Verstärkungseinstellung geändert wird). Die idea- le DC-Spannungshöhe von 0.125 bis 0.25 V wird über den Eingangswiderstand Rui() gewählt. OF1 Adr 0xA, bit 3:0; Adr 0x9, bit 7:4 OF2 Adr 0xC, bit 0; Adr 0xB, bit 7:1 Die Rückführung der Pin-Spannung V(ACO) erfüllt Code Faktor Code Faktor die gleiche Aufgabe wie die Quelle VDC, wenn MR- 0x00 0 0x80 0 Brückensensoren über die geregelte Sensor-Strom- 0x01 0.0079 0x81 −0.0079 quelle versorgt werden. Die Einstellung der VDC-Quel- ... 0.0079 · OFi ... −0.0079 · OFi len entfällt in diesem Fall. 0x7F 1 0xFF −1 VOS12 Adr 0x0E, bit 5:4 Tab. 29: Offsetabgleich Faktor CH1, CH2 Code Quelle 0x0 0.05 · V(ACO) 0x1 0.5 V Phasenabgleich CH1 gg. CH2 0x2 0.25 V Die Phasenverschiebung zwischen CH1 und CH2 0x3 VDC (VDC1 für CH1, VDC2 für CH2) kann über den Parameter PH12 eingestellt werden. Im Anschluss daran müssen möglicherweise die Kalibrie- Tab. 26: Offsetabgleich Referenzquelle CH1, CH2 rungen für den Amplitudenausgleich, für die Mittenpo- tentiale und Offsetspannungen korrigiert werden. VDC1 Adr 0x07, bit 4:0; Adr 0x06, bit 7 VDC2 Adr 0x08, bit 6:1 PH12 Adr 0xD, bit 2:0; Adr 0xC, bit 7:5 Code VDC = k · VPi + (1 − k) · VNi Code Korrekturwinkel Code Korrekturwinkel 0x00 k = 0.33 0x00 +0 0x20 −0 0x01 k = 0.335 0x01 +0.63 0x21 −0.63 ... k = 0.33 + VDCi · 0.0052 ... +0.63 · PH12 ... −0.63 · PH12 0x3F k = 0.66 0x1F +20.2 0x3F −20.2 Tab. 27: Mittenpotentiale CH1, CH2 Tab. 30: Phasenabgleich CH1 gg. CH2