Denunciar

Compartilhar

Baixar para ler offline

Recomendados

Mais conteúdo relacionado

Mais procurados

Mais procurados (20)

Simple Capacitive Voltage Transformer (CVT) Testing for Switchyard Equipment

Simple Capacitive Voltage Transformer (CVT) Testing for Switchyard Equipment

Original PNP Transistor 2SB688 B688 8A 120V New Toshiba

Original PNP Transistor 2SB688 B688 8A 120V New Toshiba

Quasi-resonant Flyback Converter Simulations with Saber - APEC 2016

Quasi-resonant Flyback Converter Simulations with Saber - APEC 2016

Original N-CHANNEL MOSFET SUP75N06 75N06 75A 60V TO-220 New Vishay Siliconix

Original N-CHANNEL MOSFET SUP75N06 75N06 75A 60V TO-220 New Vishay Siliconix

Original Mosfet 4N90C FQP4N90C FQP4N90 900V 4A TO-220 New

Original Mosfet 4N90C FQP4N90C FQP4N90 900V 4A TO-220 New

Destaque

Manual de Estudiante _ ABT-CCP-151-TSM _ RSLogix 5000, Level 2 _ Programacion...

Manual de Estudiante _ ABT-CCP-151-TSM _ RSLogix 5000, Level 2 _ Programacion...Marco Enrique Ramos Castillo

Manual de Estudiante ABT-CCP-146-TSMES - Fundamentos del Sistema RSLogix 5000...

Manual de Estudiante ABT-CCP-146-TSMES - Fundamentos del Sistema RSLogix 5000...Marco Enrique Ramos Castillo

Student Manual _ ABT-CCP-143-TSM _ RSLogix 5000, Level 3 _ Project Development

Student Manual _ ABT-CCP-143-TSM _ RSLogix 5000, Level 3 _ Project DevelopmentMarco Enrique Ramos Castillo

Manual de Practica Rslogix5000 para Programadores Nivel I _ LOT-SP004A-ES-E

Manual de Practica Rslogix5000 para Programadores Nivel I _ LOT-SP004A-ES-EMarco Enrique Ramos Castillo

Destaque (20)

Manual de Estudiante _ ABT-CCP-151-TSM _ RSLogix 5000, Level 2 _ Programacion...

Manual de Estudiante _ ABT-CCP-151-TSM _ RSLogix 5000, Level 2 _ Programacion...

Manual de Estudiante ABT-CCP-146-TSMES - Fundamentos del Sistema RSLogix 5000...

Manual de Estudiante ABT-CCP-146-TSMES - Fundamentos del Sistema RSLogix 5000...

Student Manual _ ABT-CCP-143-TSM _ RSLogix 5000, Level 3 _ Project Development

Student Manual _ ABT-CCP-143-TSM _ RSLogix 5000, Level 3 _ Project Development

Manual de Practica Rslogix5000 para Programadores Nivel I _ LOT-SP004A-ES-E

Manual de Practica Rslogix5000 para Programadores Nivel I _ LOT-SP004A-ES-E

Level 3 RSLogix 5000 development & Programming of ControlLogix Projects CCP 143

Level 3 RSLogix 5000 development & Programming of ControlLogix Projects CCP 143

Semelhante a RSLogix 5000 Report(s)

Semelhante a RSLogix 5000 Report(s) (20)

Original NPN Transistor KRC106M C106 106 TO-92 New KEC

Original NPN Transistor KRC106M C106 106 TO-92 New KEC

Original Transistor NPN MJE13003 KSE13003 E13003 13003 1.5A 400V TO-126 New

Original Transistor NPN MJE13003 KSE13003 E13003 13003 1.5A 400V TO-126 New

Original NPN Transistor MJD44H11T4G 4H11G TO-252 New ON Semiconductor

Original NPN Transistor MJD44H11T4G 4H11G TO-252 New ON Semiconductor

Original PNP Transistor MJD45H11T4G 5H11G TO-252 New ON Semiconductor

Original PNP Transistor MJD45H11T4G 5H11G TO-252 New ON Semiconductor

Original N-CHANNEL Mosfet FQPF10N60 10N60 10A 600V TO-220F New Fairchild

Original N-CHANNEL Mosfet FQPF10N60 10N60 10A 600V TO-220F New Fairchild

Current Transformers parameter design and graphs - size and design requirements

Current Transformers parameter design and graphs - size and design requirements

Design and implementation of cyclo converter for high frequency applications

Design and implementation of cyclo converter for high frequency applications

Original N-Channel Mosfet FQPF5N50C 5N50C 500V 3A TO-220F New Fairchild

Original N-Channel Mosfet FQPF5N50C 5N50C 500V 3A TO-220F New Fairchild

Original N-CHANNEL MOSFET FDS4480 4480 40V SOP-8 New Fairchild

Original N-CHANNEL MOSFET FDS4480 4480 40V SOP-8 New Fairchild

RSLogix 5000 Report(s)

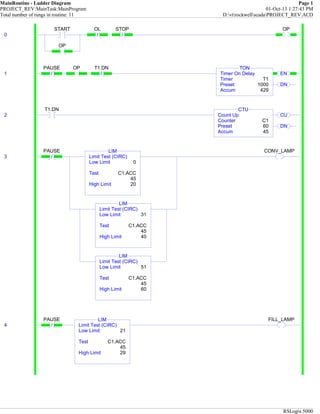

- 1. MainRoutine - Ladder Diagram Page 1 PROJECT_REV:MainTask:MainProgram 01-Oct-13 1:27:43 PM Total number of rungs in routine: 11 D:vtrockwellscadaPROJECT_REV.ACD RSLogix 5000 0 START OP / OL / STOP OP 1 / PAUSE OP / T1.DN EN DN Timer On Delay Timer T1 Preset 1000 Accum 429 TON 2 T1.DN CU DN Count Up Counter C1 Preset 60 Accum 45 CTU 3 / PAUSE Limit Test (CIRC) Low Limit 0 Test C1.ACC 45 High Limit 20 LIM Limit Test (CIRC) Low Limit 31 Test C1.ACC 45 High Limit 40 LIM Limit Test (CIRC) Low Limit 51 Test C1.ACC 45 High Limit 60 LIM CONV_LAMP 4 / PAUSE Limit Test (CIRC) Low Limit 21 Test C1.ACC 45 High Limit 29 LIM FILL_LAMP

- 2. MainRoutine - Ladder Diagram Page 2 PROJECT_REV:MainTask:MainProgram 01-Oct-13 1:27:44 PM Total number of rungs in routine: 11 D:vtrockwellscadaPROJECT_REV.ACD RSLogix 5000 5 / PAUSE Limit Test (CIRC) Low Limit 41 Test C1.ACC 45 High Limit 45 LIM CAPPING_LAMP 6 Equal Source A C1.ACC 45 Source B 60 EQU RES C1 7 Limit Test (CIRC) Low Limit 0 Test C1.ACC 45 High Limit 20 LIM PHASE1 8 Limit Test (CIRC) Low Limit 31 Test C1.ACC 45 High Limit 40 LIM PHASE2 9 Limit Test (CIRC) Low Limit 45 Test C1.ACC 45 High Limit 60 LIM PHASE3 10 STOP RES C1 (End)